|

|

PDF KU80L188EC Data sheet ( Hoja de datos )

| Número de pieza | KU80L188EC | |

| Descripción | (KU80C188EC / KU80C186EC / KU80L188EC / KU80L186EC) 16-Bit Embedded Processors | |

| Fabricantes | Intel | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de KU80L188EC (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

80C186EC 80C188EC AND 80L186EC 80L188EC

16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS

X Fully Static Operation

X True CMOS Inputs and Outputs

Y Integrated Feature Set

Low-Power Static Enhanced 8086

CPU Core

Two Independent DMA Supported

UARTs each with an Integral Baud

Rate Generator

Four Independent DMA Channels

22 Multiplexed I O Port Pins

Two 8259A Compatible

Programmable Interrupt Controllers

Three Programmable 16-Bit Timer

Counters

32-Bit Watchdog Timer

Ten Programmable Chip Selects with

Integral Wait-State Generator

Memory Refresh Control Unit

Power Management Unit

On-Chip Oscillator

System Level Testing Support

(ONCE Mode)

Y Available in Extended Temperature

Range (b40 C to a85 C)

Y Supports 80C187 Numerics Processor

Extension (80C186EC only)

Y Package Types

100-Pin EIAJ Quad Flat Pack (QFP)

100-Pin Plastic Quad Flat Pack

(PQFP)

100-Pin Shrink Quad Flat Pack

(SQFP)

Y Speed Versions Available (5V)

25 MHz (80C186EC25 80C188EC25)

20 MHz (80C186EC20 80C188EC20)

13 MHz (80C186EC13 80C188EC13)

Y Speed Version Available (3V)

16 MHz (80L186EC16 80L188EC16)

13 MHz (80L186EC13 80L188EC13)

Y Direct Addressing Capability to 1 Mbyte

Memory and 64 Kbyte I O

Y Low-Power Operating Modes

Idle Mode Freezes CPU Clocks but

Keeps Peripherals Active

Powerdown Mode Freezes All

Internal Clocks

Powersave Mode Divides All Clocks

by Programmable Prescalar

mThe 80C186EC is a member of the 186 Integrated Processor Family The 186 Integrated Processor Family

incorporates several different VLSI devices all of which share a common CPU architecture the 8086 8088

oThe 80C186EC uses the latest high density CHMOS technology to integrate several of the most common

.csystem peripherals with an enhanced 8086 CPU core to create a powerful system on a single monolithic

usilicon die

w.datasheet4Other brands and names are the property of their respective owners

Information in this document is provided in connection with Intel products Intel assumes no liability whatsoever including infringement of any patent or

wcopyright for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products Intel retains the right to make

changes to these specifications at any time without notice Microcomputer Products may have minor variations to this specification known as errata

w COPYRIGHT © INTEL CORPORATION, 2004

August, 2004

Order Number: 272434-006

1 page

80C186EC 188EC 80L186EC 188EC

272434 – 2

NOTE

1 The LC network is only required when using a third overtone crystal

Figure 2 80C186EC Clock Connections

80C186EC PERIPHERAL

ARCHITECTURE

The 80C186EC integrates several common system

peripherals with a CPU core to create a compact yet

powerful system The integrated peripherals are de-

signed to be flexbile and provide logical interconnec-

tions between supporting units (e g the DMA unit

can accept requests from the Serial Communica-

tions Unit)

The list of integrated peripherals includes

Two cascaded 8259A compatible Programma-

ble Interrupt Controllers

3-Channel Timer Counter Unit

2-Channel Serial Communications Unit

4-Channel DMA Unit

10-Output Chip-Select Unit

32-bit Watchdog Timer Unit

I O Port Unit

Refresh Control Unit

Power Management Unit

The registers associated with each integrated pe-

ripheral are contained within a 128 x 16-bit register

file called the Peripheral Control Block (PCB) The

base address of the PCB is programmable and can

be located on any 256 byte address boundary in ei-

ther memory or I O space

Figure 3 provides a list of the registers associated

with the PCB The Register Bit Summary individually

lists all of the registers and identifies each of their

programming attributes

5

5 Page

80C186EC 188EC 80L186EC 188EC

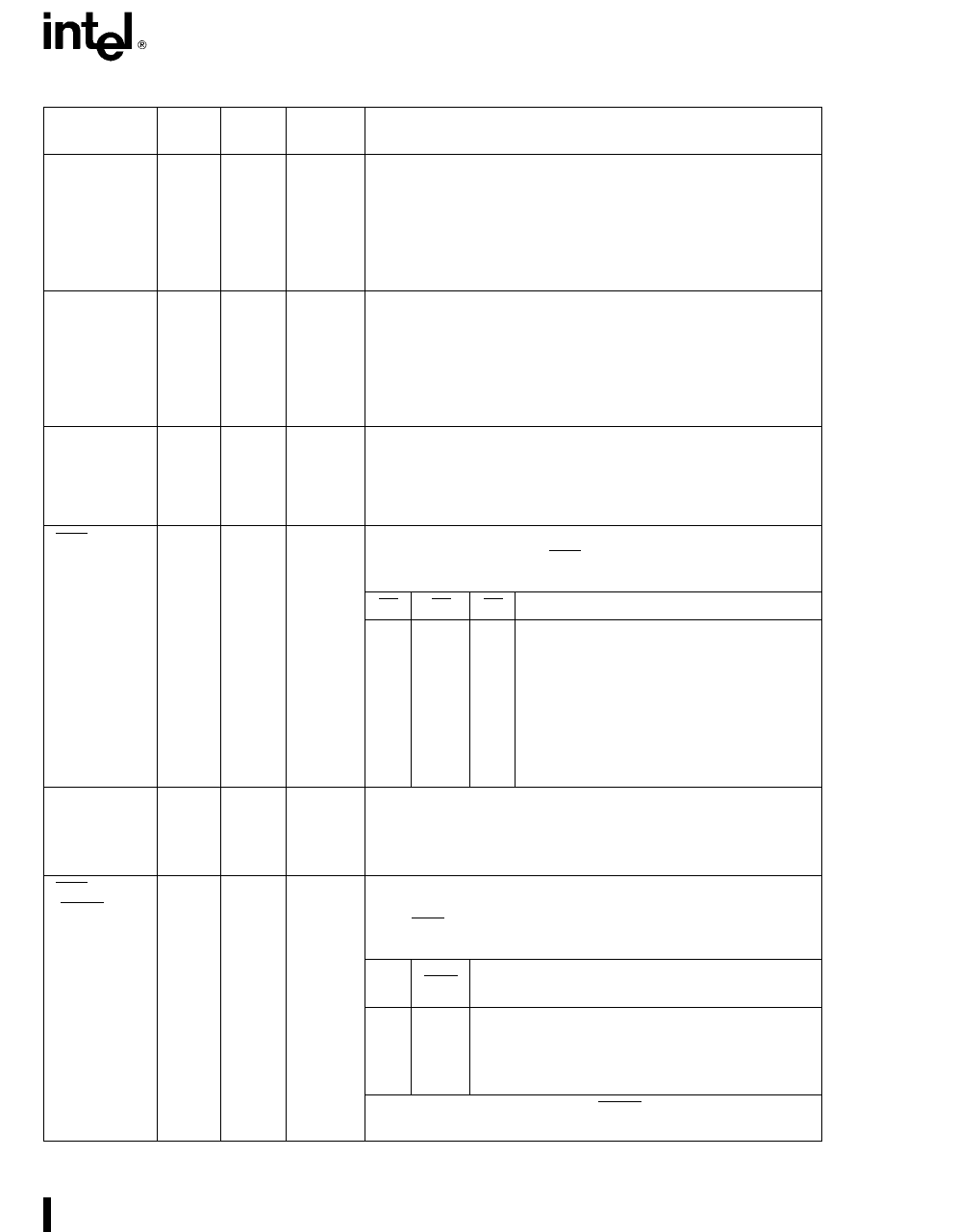

Pin Name

A18 S5

A17 S4

A16 S3

(A15 8)

AD15 CAS2

AD14 CAS1

AD13 CAS0

AD12 0

(AD7 0)

S2 0

ALE

BHE

(RFSH)

Pin

Type

IO

IO

IO

O

O

O

Input

Type

A(L)

S(L)

S(L)

Table 2 Pin Descriptions (Continued)

Output

States

Pin Description

H(Z)

R(WH)

I(0)

P(0)

These pins drive address information during the address

phase of the bus cycle During T2 and T3 these pins drive

status information (which is always 0 on the 80C186EC)

These pins are used as inputs during factory test driving

these pins low during reset will cause unspecified operation

On the 80C188EC A15 8 provide valid address information

for the entire bus cycle

H(Z)

R(Z)

I(0)

P(0)

These pins are part of the multiplexed ADDRESS and DATA

bus During the address phase of the bus cycle address bits

15 through 13 are presented on these pins and can be

latched using ALE Data information is transferred during the

data phase of the bus cycle Pins AD15 13 CAS2 0 drive the

82C59 slave address information during interrupt

acknowledge cycles

H(Z)

R(Z)

I(0)

P(0)

These pins provide a multiplexed ADDRESS and DATA bus

During the address phase of the bus cycle address bits 0

through 12 (0 through 7 on the 80C188EC) are presented on

the bus and can be latched using ALE Data information is

transferred during the data phase of the bus cycle

H(Z)

R(1)

I(1)

P(1)

Bus cycle Status are encoded on these pins to provide bus

transaction information S2 0 are encoded as follows

S2 S1 S0

Bus Cycle Initiated

000

001

010

011

100

101

110

111

Interrupt Acknowledge

Read I O

Write I O

Processor HALT

Instruction Queue Fetch

Read Memory

Write Memory

Passive (No bus activity)

H(0) Address Latch Enable output is used to strobe address

R(0) information into a transparent type latch during the address

I(0) phase of the bus cycle

P(0)

H(Z)

R(Z)

I(1)

P(1)

Byte High Enable output to indicate that the bus cycle in

progress is transferring data over the upper half of the data

bus BHE and A0 have the following logical encoding

A0 BHE

Encoding (for 80C186EC

80L186EC only)

00

01

10

11

Word transfer

Even Byte transfer

Odd Byte transfer

Refresh operation

On the 80C188EC 80L188EC RFSH is asserted low to

indicate a refresh bus cycle

NOTE

Pin names in parentheses apply to the 80C188EC 80L188EC

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet KU80L188EC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KU80L188EC | (KU80C188EC / KU80C186EC / KU80L188EC / KU80L186EC) 16-Bit Embedded Processors | Intel |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |