|

|

PDF TC58FVM62A Data sheet ( Hoja de datos )

| Número de pieza | TC58FVM62A | |

| Descripción | TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS | |

| Fabricantes | Toshiba Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TC58FVM62A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

TC58FVM6(T/B)2A(FT/XB)65

TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

64MBIT (8M × 8 BITS/4M × 16 BITS) CMOS FLASH MEMORY

DESCRIPTION

The TC58FVM6T2A/B2A is a 67108864-bit, 3.0-V read-only electrically erasable and programmable flash

memory organized as 8388608 words × 8 bits or as 4194304 words × 16 bits. The TC58FVM6T2A/B2A features

commands for Read, Program and Erase operations to allow easy interfacing with microprocessors. The commands

are based on the JEDEC standard. The Program and Erase operations are automatically executed in the chip. The

TC58FVM6T2A/B2A also features a Simultaneous Read/Write operation so that data can be read during a Write or

Erase operation.

FEATURES

• Power supply voltage

• Block erase architecture

VDD = 2.3 V~3.6 V

8 × 8 Kbytes/127 × 64 Kbytes

• Operating temperature

• Boot block architecture

Ta = −40°C~85°C

TC58FVM6T2A: top boot block

• Organization

TC58FVM6B2A: bottom boot block

8M × 8 bits/4M × 16 bits

• Mode control

• Functions

Compatible with JEDEC standard commands

Simultaneous Read/Write

Page Read

• Erase/Program cycles

105 cycles typ.

Auto Program, Auto Page Program

• Access Time (Random/Page)

Auto Block Erase, Auto Chip Erase

Fast Program Mode/Acceleration Mode

VDD

CL = 30 pF

CL = 100 pF

Program Suspend/Resume

2.7~3.6 V

65 ns/25 ns

70 ns/30 ns

Erase Suspend/Resume

2.3~3.6 V

70 ns/30 ns

75 ns/35 ns

data polling/Toggle bit

block protection, boot block protection

Automatic Sleep, support for hidden ROM area

common flash memory interface (CFI)

Byte/Word Modes

•

Power consumption

10 µA (Standby)

15 mA (Program/Erase operation)

55 mA (Random Read operation)

11 mA (Address Increment Read operation)

5 mA (Page Read operation)

• Package

TC58FVM6**AFT:

TSOPI48-P-1220-0.50 (weight: 0.51 g)

TC58FVM6**AXB:

P-TFBGA56-0710-0.80AZ (weight: 0.125 g)

2003-01-29 1/61

1 page

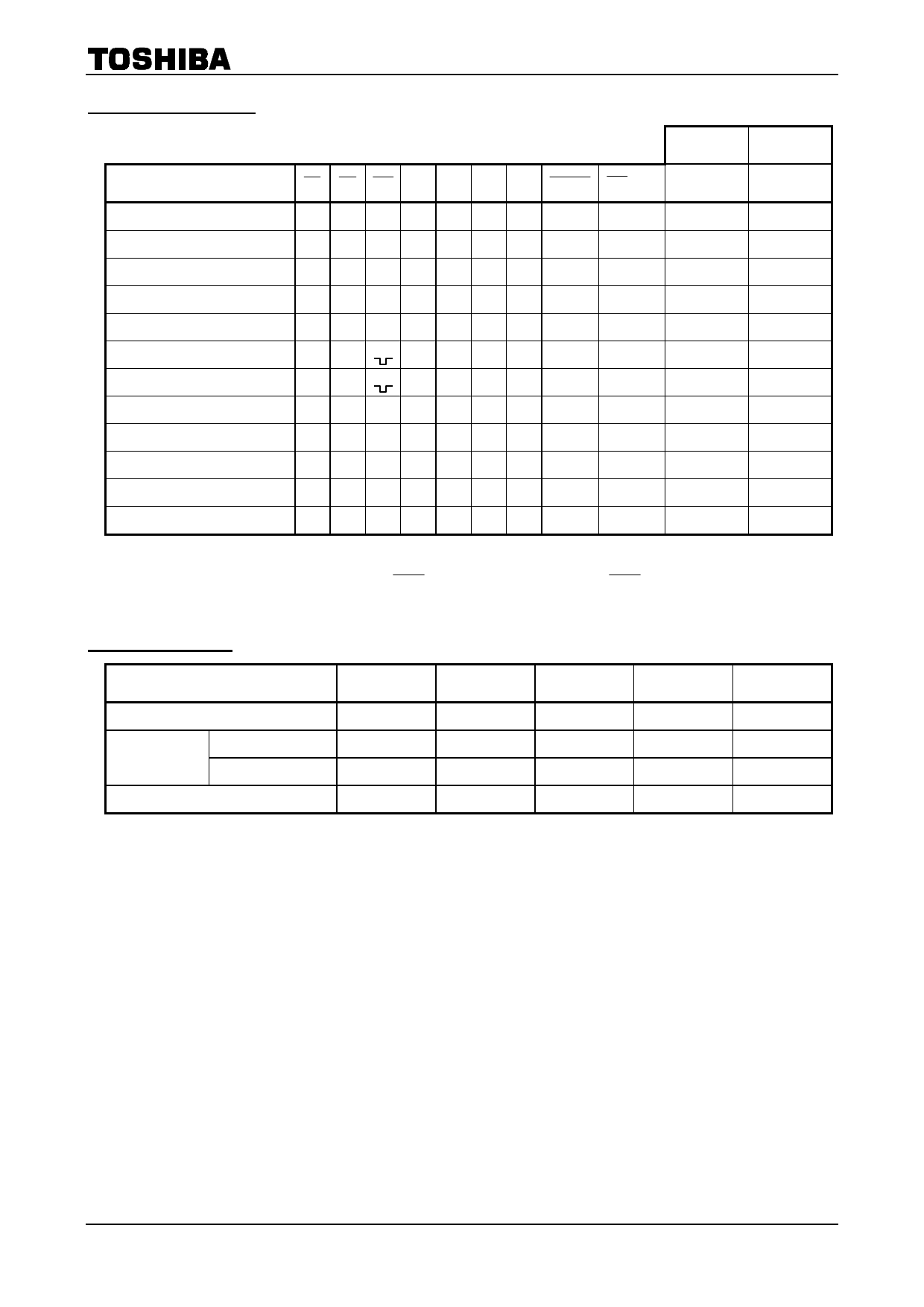

MODE SELECTION

TC58FVM6(T/B)2A(FT/XB)65

BYTE MODE WORD MODE

MODE

CE OE WE A9 A6 A1 A0 RESET WP/ACC DQ0~DQ7(1) DQ0~DQ15

Read/Page Read

L L H A9 A6 A1 A0

H

*

DOUT

ID Read (Manufacturer Code)

L L H VID L L L

H

*

Code

ID Read (Device Code)

L L H VID L L H

H

*

Code

Standby

H* * * * * *

H

*

High-Z

Output Disable

Write

Block Protect 1

Block Protect 2

Verify Block Protect

Temporary Block Unprotect

Hardware Reset/Standby

*HH* * * *

L H (2) A9 A6 A1 A0

L VID (2) VID L H L

LHH* LHL

L L H VID L H L

*******

*******

*

H

H

VID

H

VID

L

*

*

*

*

*

*

*

High-Z

DIN

*

*

Code

*

High-Z

Boot Block Protect

*******

*

L

*

Notes: * = VIH or VIL, L = VIL, H = VIH

(1) DQ8~DQ14 are High-Z and DQ15/A-1 is Address Input in Byte Mode.

Addresses are A21~A0 in Word Mode ( BYTE = VIH), A21~A-1 in Byte Mode ( BYTE = VIL).

(2) Pulse input

DOUT

Code

Code

High-Z

High-Z

DIN

*

*

Code

*

High-Z

*

ID CODE TABLE

CODE TYPE

A21~A12

A6

A1

Manufacturer Code

*L

Device Code

TC58FVM6T2A

TC58FVM6B2A

Verify Block Protect

*

*

BA(2)

L

L

L

Notes: * = VIH or VIL, L = VIL, H = VIH

(1) DQ8~DQ14 are High-Z and DQ15/A-1 is Address Input in Byte Mode.

(2) BA: Block Address

(3) 0001h - Protected Block

0000h - Unprotected Block

L

L

L

H

A0 CODE (HEX)(1)

L 0098h

H 0057h

H 0058h

L Data(3)

2003-01-29 5/61

5 Page

Program Suspend/Resume Mode

TC58FVM6(T/B)2A(FT/XB)65

Program Suspend is used to enable Data Read by suspending the Write operation. The device accepts a

Program Suspend command in Write Mode (including Write operations performed during Erase Suspend) but

ignores the command in other modes. When the command is input, the address of the bank on which Write is

being performed must be specified. After input of the command, the device will enter Program Suspend Read

Mode after tSUSP.

During Program Suspend, Cell Data Read, ID Read and CFI Data Read can be performed. When Data Write

is suspended, the address to which Write was being performed becomes undefined. ID Read and CFI Data Read

are the same as usual.

After completion of Program Suspend input a Program Resume command to return to Write Mode. When

inputting the command, specify the address of the bank on which Write is being performed. If the ID Read or

CFI Data Read functions is being used, abort the function before inputting the Resume command. On receiving

the Resume command, the device returns to Write Mode and resumes outputting the Hardware Sequence flag

for the bank to which data is being written.

Program Suspend can be run in Fast Program Mode or Acceleration Mode. However, note that when running

Program Suspend in Acceleration Mode, VACC must not be released.

Auto Chip Erase Mode

The Auto Chip Erase Mode is set using the Chip Erase command. An Auto Chip Erase operation starts on the

rising edge of WE in the sixth bus cycle. All memory cells are automatically preprogrammed to 0, erased and

verified as erased by the chip. The device status is indicated by the Hardware Sequence flag.

Command input is ignored during an Auto Chip Erase. A hardware reset can interrupt an Auto Chip Erase

operation. If an Auto Chip Erase operation is interrupted, it cannot be completed correctly. Hence an additional

Erase operation must be performed.

Any attempt to erase a protected block is ignored. If all blocks are protected, the Auto Erase operation will not

be executed and the device will enter Read mode 250µs after the rising edge of the WE signal in the sixth bus

cycle.

If an Auto Chip Erase operation fails, the device will remain in the erasing state and will not return to Read

Mode. The device status is indicated by the Hardware Sequence flag. Either a Reset command or a hardware

reset is required to return the device to Read Mode after a failure.

In this case it cannot be ascertained which block the failure occurred in. Either abandon use of the device

altogether, or perform a Block Erase on each block, identify the failed block, and stop using it. The host

processor must take measures to prevent subsequent use of the failed block.

2003-01-29 11/61

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet TC58FVM62A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TC58FVM62A | TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS | Toshiba Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |