|

|

PDF ICS950910 Data sheet ( Hoja de datos )

| Número de pieza | ICS950910 | |

| Descripción | Programmable Timing Control Hub for P4 | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS950910 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

ICS950910

Programmable Timing Control Hub™ for P4™

Recommended Application:

VIA P4X/P4M/KT/KN266/333 style chipsets.

Output Features:

• 1 - Pair of differential CPU clocks @ 3.3V (CK408)/

1 - Pair of differential open drain CPU clocks (K7)

• 1 - Pair of differential push pull CPU_CS clocks @ 2.5V

• 3 - AGP @ 3.3V

• 7 - PCI @ 3.3V

• 1 - 48MHz @ 3.3V fixed

• 1 - 24_48MHz @ 3.3V

• 2 - REF @ 3.3V, 14.318MHz

Key Specifications:

• CPU_CS - CPUT/C: <±250ps

• CPU_CS - AGP: <±250ps

• CPU - DDR: <±250ps

• PCI - PCI: <500ps

• CPU - PCI: Min = 1.0ns, Typ = 2.0ns, Max = 4.0ns

Features/Benefits:

• Programmable output frequency.

• Programmable output divider ratios.

• Programmable output rise/fall time.

• Programmable output skew.

• Programmable spread percentage for EMI control.

• DDR output buffer supports up to 200MHz.

• Watchdog timer technology to reset system

if system malfunctions.

• Programmable watch dog safe frequency.

• Support I2C Index read/write and block read/write

operations.

• Uses external 14.318MHz crystal.

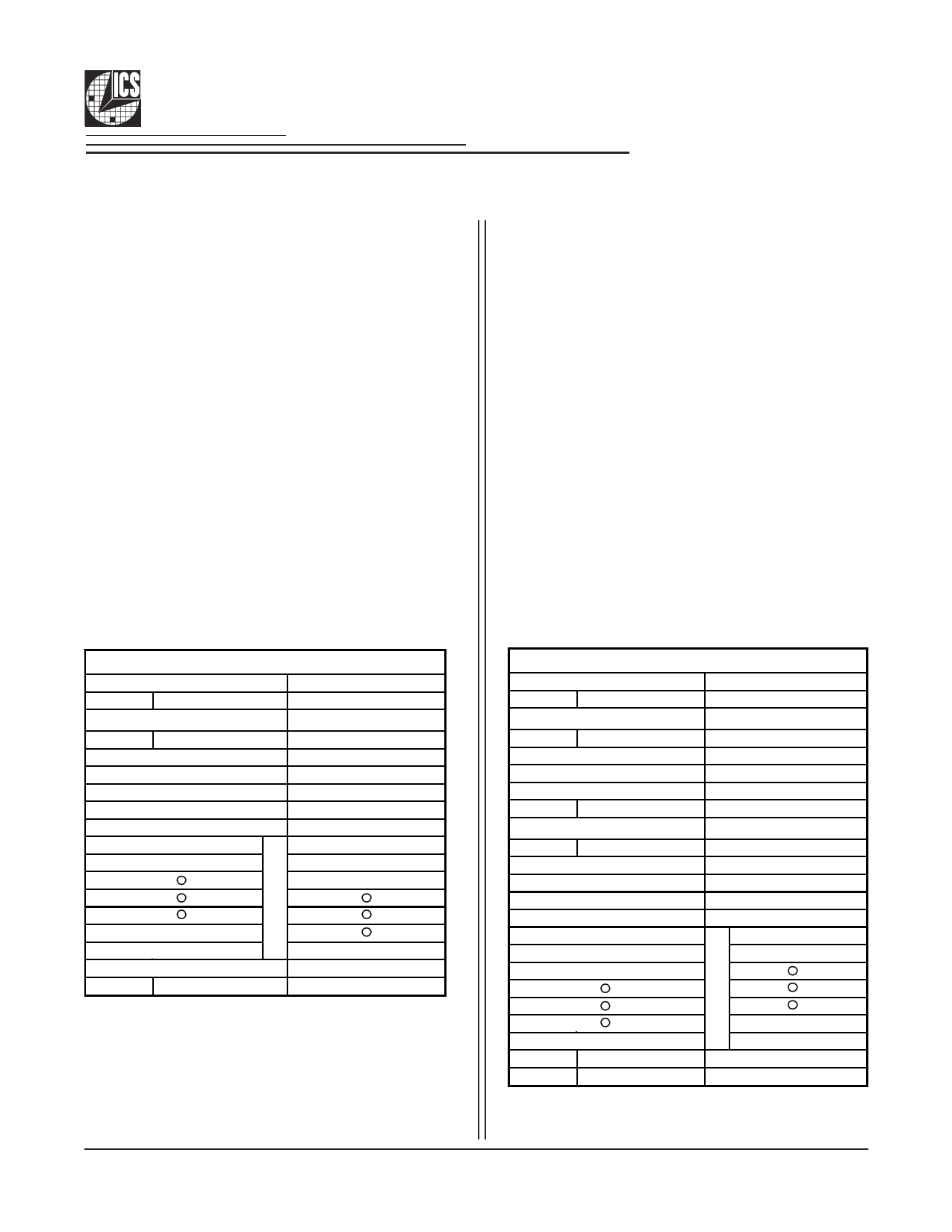

Frequency Table

Bit2 Bit7 Bit6 Bit5 Bit4

FS3 FS2 FS1 FS0

CPU

MHz

1 0 0 0 0 105.00

1 0 0 0 1 140.00

1 0 0 1 0 210.00

1 0 0 1 1 174.99

1 0 1 0 0 80.00

1 0 1 0 1 106.66

1 0 1 1 0 160.00

1 0 1 1 1 133.33

1 1 1 0 0 100.00

1 1 1 0 1 133.33

1 1 1 1 0 200.00

1 1 1 1 1 166.66

1 1 0 0 0 100.00

1 1 0 0 1 133.33

1 1 0 1 0 200.00

1 1 0 1 1 166.66

AGP

MHz

70.00

70.00

70.00

70.00

53.34

53.34

53.34

53.34

66.67

66.67

66.67

66.67

66.67

66.67

66.67

66.67

PCI

MHz

35.00

35.00

35.00

35.00

26.66

26.66

26.66

26.66

33.33

33.33

33.33

33.33

33.33

33.33

33.33

33.33

Spread %

0.3 % Center Spread

0.3 % Center Spread

0.3 % Center Spread

0.3 % Center Spread

0.3 % Center Spread

0.3 % Center Spread

0.3 % Center Spread

0.3 % Center Spread

0.3 % Center Spread

0.3 % Center Spread

0.3 % Center Spread

0.3 % Center Spread

0 - 0.6% Down Spread

0 - 0.6% Down Spread

0 - 0.6% Down Spread

0 - 0.6% Down Spread

MULTISEL0

Board Target

Trace/Term Z

0 50 ohms

1 50 ohms

Reference R,

Iref =

VDD/(3*Rr)

Rr = 221 1%,

Iref = 5.00mA

Rr = 475 1%,

Iref = 2.32mA

Output

Current

Voh @ Z

Ioh = 4* I REF 1.0V @ 50

Ioh = 6* I REF 0.7V @ 50

0735A—03/18/04

Pin Configuration

*FS0/REF0 1

56 Vtt_PWRGD#**/REF1

GND 2

55 VDDREF

X1 3

54 GND

X2 4

53 CPUCLKT/CPUCLKODT

VDDAGP 5

52 CPUCLKC/CPUCLKODC

*MODE/AGPCLK0 6

51 VDDCPU3.3

*SEL_408/K7/AGPCLK1 7

50 VDDCPU2.5

*(PCI_STOP#)AGPCLK2 8

49 CPUC_CS

GNDAGP 9

48 CPUT_CS

**FS1/PCICLK_F 10

47 GND

***PCICLK1 11

46 FBOUT

*MULTSEL/PCICLK2 12

45 BUF_IN

GNDPCI 13

44 DDRT0

PCICLK3 14

43 DDRC0

PCICLK4 15

42 DDRT1

VDDPCI 16

41 DDRC1

PCICLK5 17

40 VDD2.5

*(CLK_STOP#)PCICLK6 18

39 GND

GND48 19

38 DDRT2

*FS3/48MHz 20

37 DDRC2

*FS2/24_48MHz 21

36 DDRT3

AVDD48 22

35 DDRC3

VDD 23

34 VDD2.5

GND 24

33 GND

IREF 25

32 DDRT4

*(PD#)RESET# 26

31 DDRC4

SCLK 27

30 DDRT5

SDATA 28

29 DDRC5

56-SSOP

* Internal Pull-Up Resistor

** Internal Pull-Down Resistor

*** A 120k pull-down resistor to GND is needed on this pin.

1 page

Integrated

Circuit

Systems, Inc.

ICS950910

General I2C serial interface information

How to Write:

• Controller (host) sends a start bit.

• Controller (host) sends the write address D2 (H)

• ICS clock will acknowledge

• Controller (host) sends the begining byte location = N

• ICS clock will acknowledge

• Controller (host) sends the data byte count = X

• ICS clock will acknowledge

• Controller (host) starts sending Byte N through

Byte N + X -1

(see Note 2)

• ICS clock will acknowledge each byte one at a time

• Controller (host) sends a Stop bit

How to Read:

• Controller (host) will send start bit.

• Controller (host) sends the write address D2 (H)

• ICS clock will acknowledge

• Controller (host) sends the begining byte

location = N

• ICS clock will acknowledge

• Controller (host) will send a separate start bit.

• Controller (host) sends the read address D3 (H)

• ICS clock will acknowledge

• ICS clock will send the data byte count = X

• ICS clock sends Byte N + X -1

• ICS clock sends Byte 0 through byte X (if X(H)

was written to byte 8).

• Controller (host) will need to acknowledge each byte

• Controllor (host) will send a not acknowledge bit

• Controller (host) will send a stop bit

Index Block Write Operation

Controller (Host)

T starT bit

ICS (Slave/Receiver)

Slave Address D2(H)

WR WRite

ACK

Beginning Byte = N

ACK

Data Byte Count = X

ACK

Beginning Byte N

ACK

Byte N + X - 1

P stoP bit

ACK

*See notes on the following page.

0735A—03/18/04

5

Index Block Read Operation

Controller (Host)

ICS (Slave/Receiver)

T starT bit

Slave Address D2(H)

WR WRite

ACK

Beginning Byte = N

ACK

RT Repeat starT

Slave Address D3(H)

RD ReaD

ACK

ACK

ACK

Data Byte Count = X

Beginning Byte N

N Not acknowledge

P stoP bit

Byte N + X - 1

5 Page

Integrated

Circuit

Systems, Inc.

ICS950910

Byte 17: Output Divider Control Register

Bit

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Name

AGP_INV

Reserved

CPU_INV

CPU_INV

PCI Div 3

PCI Div 2

PCI Div 1

PCI Div 0

PWD

Description

0 AGP Phase Inversion bit

0 Reserved

0 CPU T/C Phase Inversion bit

0 CPUT/C_CS Phase Inversion bit

1

0

0

PCI clock divider ratio can be configured via these 4 bits

individually. For divider selection table refer to Table 2.

Default at power up is latched FS divider.

1

Table 1

Div (3:2)

00 01 10 11

Div (1:0)

00 /2 /4 /8 /16

01 /3 /6 /12 /24

10 /5 /10 /20 /40

11 /7 /14 /28 /56

Table 2

Div (3:2)

00 01 10 11

Div (1:0)

00 /4 /8 /16 /32

01 /3 /6 /12 /24

10 /5 /10 /20 /40

11 /9 /18 /36 /72

Byte 18: Group Skew Control Register

Bit

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Name

CPUCLKT/C_CS

Group Skew

Control

CPUCLKT/C

Group Skew

Control

AGPCLK

Group Skew

Control

Reserved

Reserved

PWD

1

0

1

0

1

0

X

X

Description

These 2 bits delay the CPUCLKT/C_CS with respect to

CPUCLKT/C

00 = 0ps 01 = 250ps 10 = 500ps 11 =750ps

These 2 bits delay the CPUCLKT/C clock with respect to

CPUCLKT/C_CS

00 = 0ps 01 = 250ps 10 = 500ps 11 = 750ps

These 2 bits delay the AGPCLK clocks with respect to CPUCLK

00 = 0ps 01 = 250ps 10 = 500ps 11 = 750ps

Reserved

Reserved

Byte 19: Group Skew Control Register

Bit

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Name

Reserved

PCICLK(5:0)

Group Skew

Control

PWD

1

0

0

0

1

0

0

0

Description

Reserved

These 4 bits can change the CPU to PCI (5:0) skew from 1.4ns -

2.9ns. Default at power up is - 2.5ns. Each binary increment or

decrement of Bits (3:0) will increase or decrease the delay of the

PCI clocks by 100ps.

0735A—03/18/04

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet ICS950910.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS950910 | Programmable Timing Control Hub for P4 | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |