|

|

PDF AD5251 Data sheet ( Hoja de datos )

| Número de pieza | AD5251 | |

| Descripción | (AD5251 / AD5252) Dual 64-and 256-Position I2C Nonvolatile Memory Digital Potentiometers | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD5251 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

Dual 64-and 256-Position I2C Nonvolatile

Memory Digital Potentiometers

AD5251/AD5252

FEATURES

AD5251: Dual 64-position resolution

AD5252: Dual 256-position resolution

1 kΩ, 10 kΩ, 50 kΩ, 100 kΩ

Nonvolatile memory1 stores wiper setting w/write protection

Power-on refreshed with EEMEM settings in 300 µs typ

EEMEM rewrite time = 540 µs typ

Resistance tolerance stored in nonvolatile memory

12 extra bytes in EEMEM for user-defined information

I2C compatible serial interface

Direct read/write access of RDAC2 and EEMEM registers

Predefined linear increment/decrement commands

Predefined ±6 dB step change commands

Synchronous or aysynchronous dual channel update

Wiper setting read back

4 MHz bandwidth—1 kΩ version

Single supply 2.7 V to 5.5 V

Dual supply ±2.25 V to ±2.75 V

2 slave address decoding bits allow operation of 4 devices

100-year typical data retention TA = 55°C

Operating temperature –40°C to +85°C

APPLICATIONS

Mechanical potentiometer replacement

General purpose DAC replacement

LCD panel VCOM adjustment

GENERAL DESCRIPTION

The AD5251/AD5252 are dual-channel, I2C, nonvolatile mem-

ory, digitally controlled potentiometers with 64/256 positions,

respectively. These devices perform the same electronic adjust-

ment functions as mechanical potentiometers, trimmers, and

variable resistors. The parts’ versatile programmability allows

multiple modes of operation, including read/write access in the

RDAC and EEMEM registers, increment/decrement of

resistance, resistance changes in ±6 dB scales, wiper setting

readback, and extra EEMEM for storing user-defined infor-

mation such as memory data for other components, look-up

table, or system identification information.

The AD5251/AD5252 allow the host I2C controllers to write

any of the 64- or 256-step wiper settings in the RDAC registers

and store them in the EEMEM. Once the settings are stored,

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

White LED brightness adjustment

RF base station power amp bias control

Programmable gain and offset control

Programmable voltage-to-current conversion

Programmable power supply

Sensor calibrations

FUNDAMENTAL BLOCK DIAGRAM

VDD

VSS

DGND

WP

SCL

SDA

AD0

AD1

I2C

SERIAL

INTERFACE

POWER-

ON RESET

RDAC EEMEM

EEMEM

POWER-ON

REFRESH

RAB

TOL

RDAC1

REGIS-

TER

RDAC1

DATA

CONTROL

RDAC3

REGIS-

TER

RDAC3

COMMAND

DECODE LOGIC

ADDRESS

DECODE LOGIC

CONTROL LOGIC

AD5251/

AD5252

A1

W1

B1

A3

W3

B3

Figure 1.

1The terms nonvolatile memory and EEMEM are used interchangeably.

2The terms digital potentiometer and RDAC are used interchangeably.

they are restored automatically to the RDAC registers at system

power-on; the settings can also be restored dynamically.

The AD5251/AD5252 provide additional increment,

decrement, +6 dB step change, and –6 dB step change in

synchronous or asynchronous channel update modes. The

increment and decrement functions allow stepwise linear

adjustments, while ±6 dB step changes are equivalent to

doubling or halving the RDAC wiper setting. These functions

are useful for steep-slope nonlinear adjustments such as white

LED brightness and audio volume control. The parts have a

patented resistance tolerance storing function which enable the

user to access the EEMEM and obtain the absolute end-to-end

resistance values of the RDACs for precision applications.

The AD5251/AD5252 are available in TSSOP-14 packages in

1 kΩ, 10 kΩ, 50 kΩ, and 100 kΩ options and all parts can

operate over the –40°C to +85°C extended industrial

temperature range.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

1 page

AD5251/AD5252

10 kΩ, 50 kΩ, 100 kΩ Versions. VDD = +3 V ± 10% or + 5 V ± 10%. VSS = 0 V or VDD/VSS = ± 2.5 V ± 10%. VA = +VDD, VB = 0 V,

–40°C < TA < +85°C, unless otherwise noted.

Table 2.

Parameter

Symbol

Conditions

Min Typ1

Max Unit

DC CHARACTERISTICS

RHEOSTAT MODE

Resolution

N AD5251/AD5252

6/8 Bits

Resistor Differential NL2

R-DNL

RWB, RWA = NC, AD5251

−0.75 ±0.1

+0.75 LSB

Resistor Nonlinearity2

R-INL

RWB, RWA = NC, AD5252

RWB, RWA = NC, AD5251

−1 ±0.25

−0.75 ±0.25

+1 LSB

+0.75 LSB

RWB, RWA = NC, AD5252

−2.5 ±1

+2.5 LSB

Nominal Resistor Tolerance

Resistance Temperature

Coefficent

∆RAB/RAB

TA = 25°C

(∆RAB/RAB) × 106/∆T

−20

650

+20 %

ppm/°C

Wiper Resistance

RW

IW = 1 V/R, VDD = 5 V

75 130 Ω

IW = 1 V/R, VDD = 3 V

200 300 Ω

Channel Resistance Matching ∆RAB1/∆RAB2

RAB = 10 kΩ, 50 kΩ

0.15 %

RAB = 100 kΩ

0.05 %

DC CHARACTERISTICS

POTENTIOMETER DIVIDER

MODE

Differential Nonlinearity3

Integral Nonlinearity

3

Voltage Divider

Temperature Coefficent

Full-Scale Error

Zero-Scale Error

RESISTOR TERMINALS

Voltage Range4

Capacitance5 Ax, Bx

Capacitance5 Wx

Common-Mode Leakage

Current

DIGITAL INPUTS and OUTPUTS

Input Logic High

Input Logic Low

Output Logic High (SDA)

Output Logic Low (SDA)

Leakage Current

A0 Leakage Current

Input Leakage Current

(Other than WP and A0)

Input Capacitance5

POWER SUPPLIES

Single-Supply Power Range

DNL AD5251

AD5252

INL AD5251

AD5252

(∆VW/VW) × 106/∆T

VWFSE

VWZSE

Code = half scale

Code = full scale, AD5251

Code = full scale, AD5252

Code = zero scale, AD5251

Code = zero scale, AD5252

VA, VB, VW

CA, CB

CW

ICM

f = 1 kHz, measured to GND,

Code = half scale

f = 1 kHz, measured to GND,

Code = half scale

VA = VB = VDD/2

−0.5

−1

−0.5

−1.5

−1

−3

0

0

VSS

VIH VDD =5 V, VSS = 0 V

2.4

VDD/VSS = +2.7 V/0 V or VDD/VSS = ±2.5 V 2.1

VIL VDD = 5 V, VSS = 0 V

VDD/VSS = +2.7 V/0 V or VDD/VSS =±2.5 V

VOH

RPULL-UP = 2.2 kΩ to VDD = 5 V, VSS = 0 V

4.9

VOL RPULL-UP = 2.2 kΩ to VDD = 5 V, VSS = 0 V

IWP WP = VDD

IA0 A0 = GND

II VIN = 0 V or VDD

CI

VDD VSS = 0 V

2.7

±0.1

±0.3

±0.15

±0.5

15

−0.3

−1

0.3

1.2

85

95

0.01

5

+0.5 LSB

+1 LSB

+0.5 LSB

+1.5 LSB

ppm/°C

0 LSB

0 LSB

1 LSB

3 LSB

VDD V

pF

pF

1 µA

V

V

0.8 V

0.6 V

V

0.4 V

5 µA

3 µA

±1 µA

pF

5.5 V

Rev. 0 | Page 5 of 28

5 Page

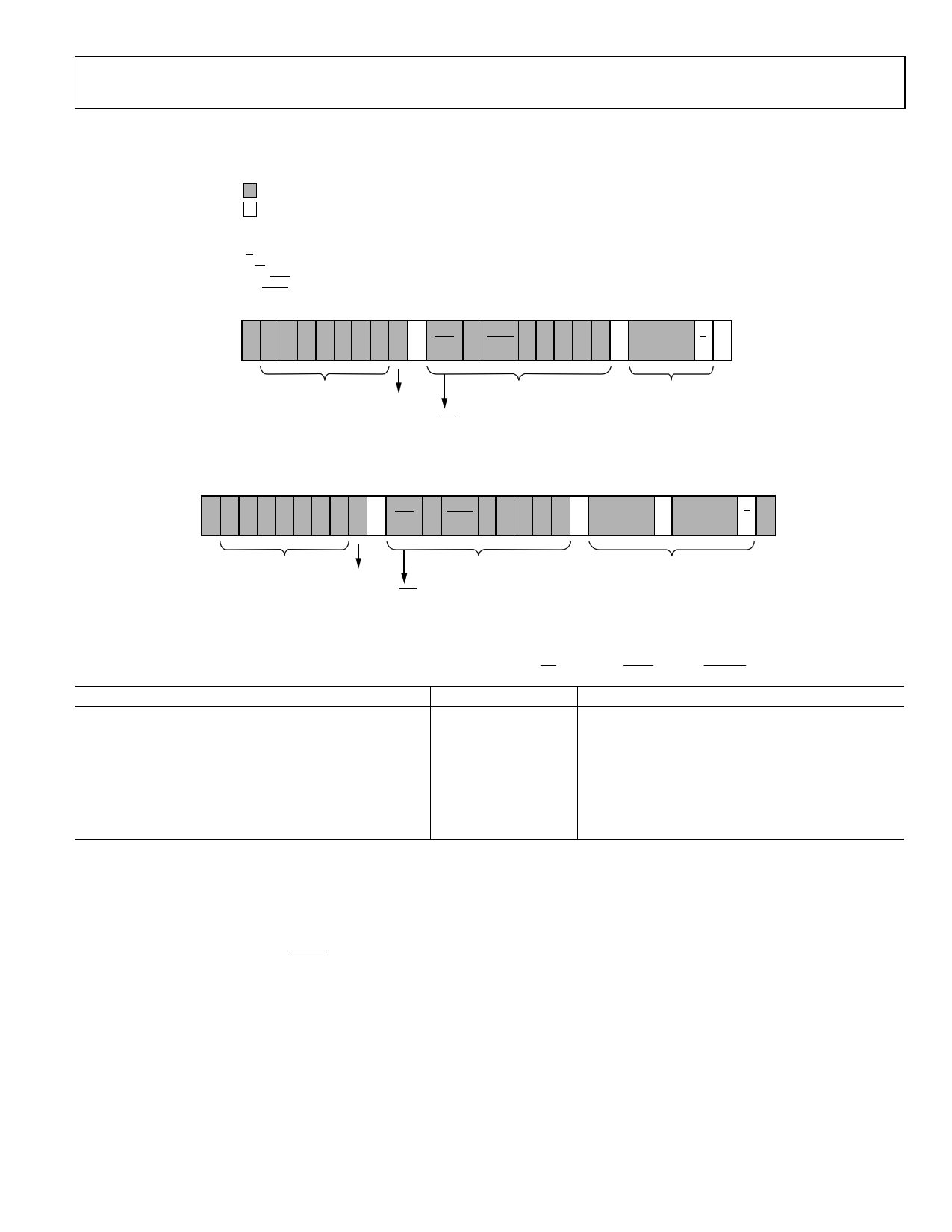

I2C INTERFACE DETAIL DESCRIPTION

AD5251/AD5252

FROM MASTER TO SLAVE

FROM SLAVE TO MASTER

S = START CONDITION

P = STOP CONDITION

A = ACKNOWLEDGE (SDA LOW)

A = NOT ACKNOWLEDGE (SDA HIGH)

R/W = READ ENABLE AT HIGH AND WRITE ENABLE AT LOW

CMD/REG = COMMAND ENABLE BIT, LOGIC HIGH/REGISTER ACCESS BIT, LOGIC LOW

EE/RDAC = EEMEM REGISTER, LOGIC HIGH/RDAC REGISTER, LOGIC LOW

A4, A3, A2, A1, A0 = RDAC/EEMEM REGISTER ADDRESSES

S 0 1 0 1 1 A A 0 A CMD/ 0 EE/ A A A A A A

DD

10

REG

RDAC 4 3 2 1 0

DATA

A/ P

A

SLAVE ADDRESS

0 WRITE

0 REG

INSTRUCTIONS

AND ADDRESS

Figure 7. Single Write Mode

(1 BYTE +

ACKNOWLEDGE)

S 0 1 0 1 1 A A 0 A CMD/ 0 EE/ A A A A A A RDAC1 A RDAC3 A/ P

DD

10

REG

RDAC 4 3 2 1 0

DATA

DATA

A

RDAC SLAVE ADDRESS

0 WRITE

RDAC INSTRUCTIONS

AND ADDRESS

0 REG

Figure 8. Consecutive Write Mode

(N BYTES +

ACKNOWLEDGE)

Table 6. Addresses for Writing Data Byte Contents to RDAC Registers (R/W = 0, CMD/REG = 0, EE/RDAC = 0)

A4 A3 A2 A1 A0 RDAC

Data Byte Description

0 0 0 0 0 Reserved

0 0 0 0 1 RDAC1

6- or 8 bit wiper setting (2 MSBs of AD5251 are X)

0 0 0 1 0 Reserved

0 0 0 1 1 RDAC3

6- or 8 bit wiper setting (2 MSBs of AD5251 are X)

0 0 1 0 0 Reserved

:::::

0 1 1 1 1 Reserved

RDAC/EEMEM WRITE

Setting the wiper position requires an RDAC write operation.

The single write operation is shown in Figure 7, and the

consecutive write operation is shown in Figure 8. In the

consecutive write operation, if the RDAC is selected and the

address starts at 00001, the first data byte goes to RDAC1 and

the second data byte goes to RDAC3. The RDAC address is

shown in Table 6.

While the RDAC wiper setting is controlled by a specific RDAC

register, each RDAC register corresponds to a specific EEMEM

location, which provides nonvolatile wiper storage functionality.

The addresses are shown in Table 7. The single and consecutive

write operations apply also to EEMEM write operations.

There are 12 nonvolatile memory locations: EEMEM4 to

EEMEM15. Users can store a total of 12 bytes of information,

such as memory data for other components, look-up tables, or

system identification information.

In a write operation to the EEMEM registers, the device disables

the I2C interface during the internal write cycle. Acknowledge

polling is required to determine the completion of the write

cycle. See EEMEM Write-Acknowledge Polling.

Rev. 0 | Page 11 of 28

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet AD5251.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD5251 | (AD5251 / AD5252) Dual 64-and 256-Position I2C Nonvolatile Memory Digital Potentiometers | Analog Devices |

| AD5252 | (AD5251 / AD5252) Dual 64-and 256-Position I2C Nonvolatile Memory Digital Potentiometers | Analog Devices |

| AD5253 | Quad 64-/256-Position I2C Nonvolatile Memory Digital Potentiometers | Analog Devices |

| AD5254 | Quad 64-/256-Position I2C Nonvolatile Memory Digital Potentiometers | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |