|

|

PDF ICS8735-01 Data sheet ( Hoja de datos )

| Número de pieza | ICS8735-01 | |

| Descripción | ZERO DELAY CLOCK GENERATOR | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS8735-01 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

ICS8735-01

1:5 DIFFERENTIAL-TO-3.3V LVPECL

ZERO DELAY CLOCK GENERATOR

GENERAL DESCRIPTION

ICS

The ICS8735-01 is a highly versatile 1:5 Differ-

ential-to-3.3V LVPECL clock generator and a

HiPerClockS™ member of the HiPerClockS™ family of High

Performance Clock Solutions from ICS. The

ICS8735-01 has a fully integrated PLL and can

be configured as zero delay buffer, multiplier or divider, and

has an output frequency range of 31.25MHz to 700MHz. The

reference divider, feedback divider and output divider are each

programmable, thereby allowing for the following output-to-

input frequency ratios: 8:1, 4:1, 2:1, 1:1, 1:2, 1:4, 1:8. The

external feedback allows the device to achieve “zero delay”

between the input clock and the output clocks. The PLL_SEL

pin can be used to bypass the PLL for system test and debug

purposes. In bypass mode, the reference clock is routed

around the PLL and into the internal output dividers.

FEATURES

• 5 differential 3.3V LVPECL outputs

• Selectable differential clock inputs

• CLKx, nCLKx pair can accept the following differential

input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL

• Output frequency range: 31.25MHz to 700MHz

• Input frequency range: 31.25MHz to 700MHz

• VCO range: 250MHz to 700MHz

• Programmable dividers allow for the following output-to-input

frequency ratios: 8:1, 4:1, 2:1, 1:1, 1:2, 1:4, 1:8

• External feedback for “zero delay” clock regeneration

with configurable frequencies

• Cycle-to-cycle jitter: 25ps (maximum)

• Output skew: 25ps (maximum)

• Static phase offset: 50ps ± 100ps

• 3.3V supply voltage

• 0°C to 70°C ambient operating temperature

• Industrial temperature information available upon request

BLOCK DIAGRAM

PLL_SEL

CLK0

nCLK0

CLK1

nCLK1

CLK_SEL

FB_IN

nFB_IN

÷1, ÷2, ÷4, ÷8,

÷16, ÷32, ÷64

0

1

PLL

8:1, 4:1, 2:1, 1:1,

1:2, 1:4, 1:8

SEL0

SEL1

SEL2

SEL3

MR

8735AY-01

PIN ASSIGNMENT

Q0

nQ0

Q1

nQ1

0

Q2 32 31 30 29 28 27 26 25

1

nQ2

SEL0 1

2 4 VCCO

Q3 SEL1 2

23 Q3

nQ3

CLK0 3

22 nQ3

Q4

nQ4

nCLK0

CLK1

4

5

ICS8735-01 21 Q2

20 nQ2

nCLK1 6

19 Q1

CLK_SEL 7

18 nQ1

MR 8

1 7 VCCO

9 10 11 12 13 14 15 16

32-Lead LQFP

7mm x 7mm x 1.4mm package body

Y Package

Top View

32-Lead VFQFN

5mm x 5mm x 0.95 package body

K Package

Top View

www.icst.com/products/hiperclocks.html

REV. F NOVEMBER 12, 2004

1

1 page

Integrated

Circuit

Systems, Inc.

ICS8735-01

1:5 DIFFERENTIAL-TO-3.3V LVPECL

ZERO DELAY CLOCK GENERATOR

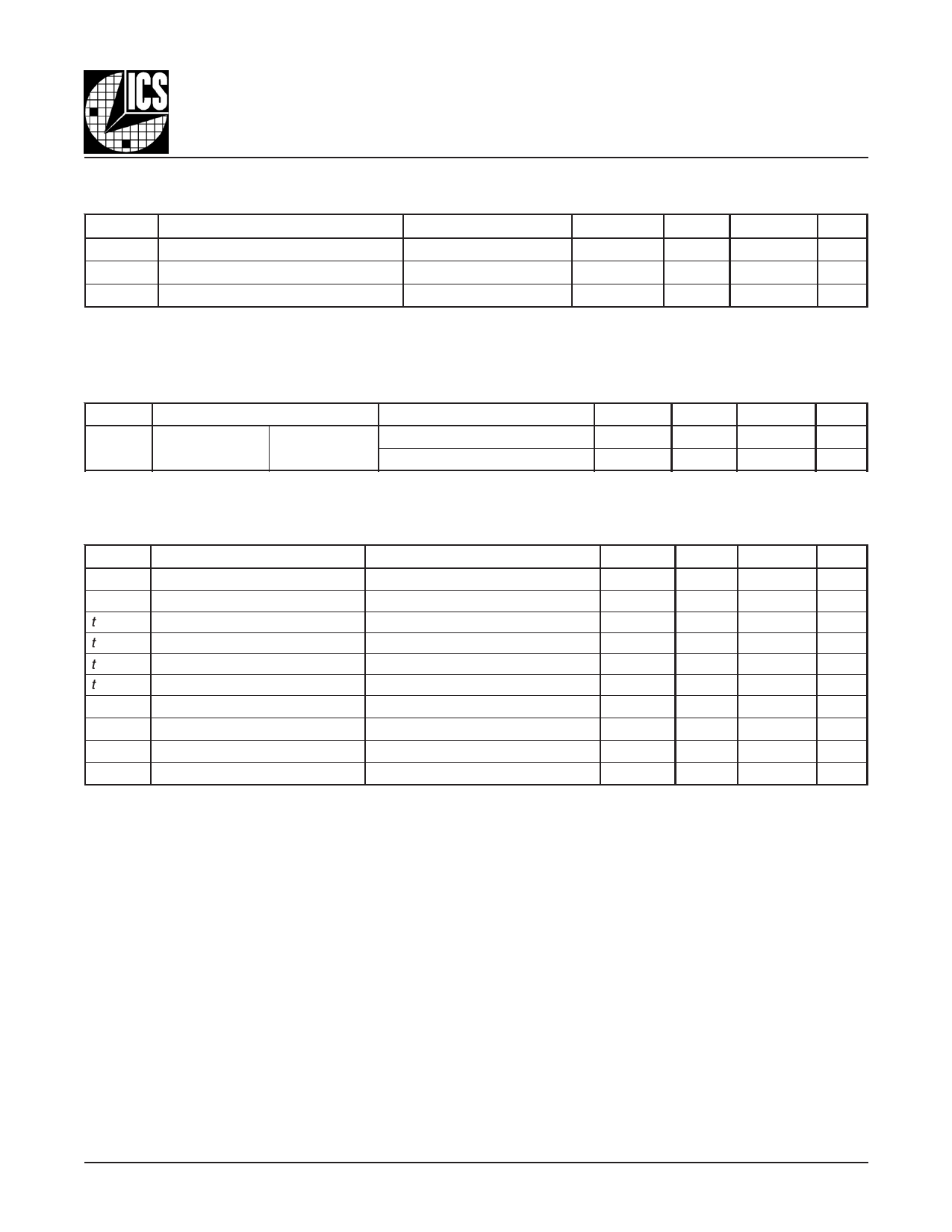

TABLE 4D. LVPECL DC CHARACTERISTICS, VCC = VCCA = VCCO = 3.3V±5%, TA = 0°C TO 70°C

Symbol Parameter

Test Conditions

Minimum

VOH Output High Voltage; NOTE 1

VOL Output Low Voltage; NOTE 1

VSWING

Peak-to-Peak Output Voltage Swing

NOTE 1: Outputs terminated with 50Ω to VCCO - 2V.

VCCO - 1.4

VCCO - 2.0

0.6

Typical

Maximum

VCCO - 1.0

VCCO - 1.7

1.0

Units

V

V

V

TABLE 5. INPUT FREQUENCY CHARACTERISTICS, VCC = VCCA = VCCO = 3.3V±5%, TA = 0°C TO 70°C

Symbol

f

IN

Parameter

Input Frequency

CLK0, nCLK0,

CLK1, nCLK1

Test Conditions

PLL_SEL = 1

PLL_SEL = 0

Minimum

31.25

Typical

Maximum

700

700

Units

MHz

MHz

TABLE 6. AC CHARACTERISTICS, VCC = VCCA = VCCO = 3.3V±5%, TA = 0°C TO 70°C

Symbol Parameter

Test Conditions

Minimum Typical Maximum

fMAX Output Frequency

tPD Propagation Delay; NOTE 1

t(Ø) Static Phase Offset; NOTE 2, 5

PLL_SEL = 0V, f ≤ 700MHz

PLL_SEL = 3.3V

700

3.4 4.2

-50 50 150

tsk(o) Output Skew; NOTE 3, 5

25

tjit(cc)

tjit(θ)

Cycle-to-Cycle Jitter; NOTE 5, 6

Phase Jitter; NOTE 4, 5, 6

25

±50

tL PLL Lock Time

tR Output Rise Time

tF Output Fall Time

odc Output Duty Cycle

20% to 80% @ 50MHz

20% to 80% @ 50MHz

300

300

47

1

700

700

53

All parameters measured at fMAX unless noted otherwise.

NOTE 1: Measured from the differential input crossing point to the differential output crossing point.

NOTE 2: Defined as the time difference between the input reference clock and the averaged feedback input signal,

when the PLL is locked and the input reference frequency is stable.

NOTE 3: Defined as skew between outputs at the same supply voltage and with equal load conditions.

Measured at the output differential cross points.

NOTE 4: Phase jitter is dependent on the input source used.

NOTE 5: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 6: Characterized at VCO frequency of 622MHz.

Units

MHz

ns

ps

ps

ps

ps

ms

ps

ps

%

8735AY-01

www.icst.com/products/hiperclocks.html

5

REV. F NOVEMBER 12, 2004

5 Page

Integrated

Circuit

Systems, Inc.

ICS8735-01

1:5 DIFFERENTIAL-TO-3.3V LVPECL

ZERO DELAY CLOCK GENERATOR

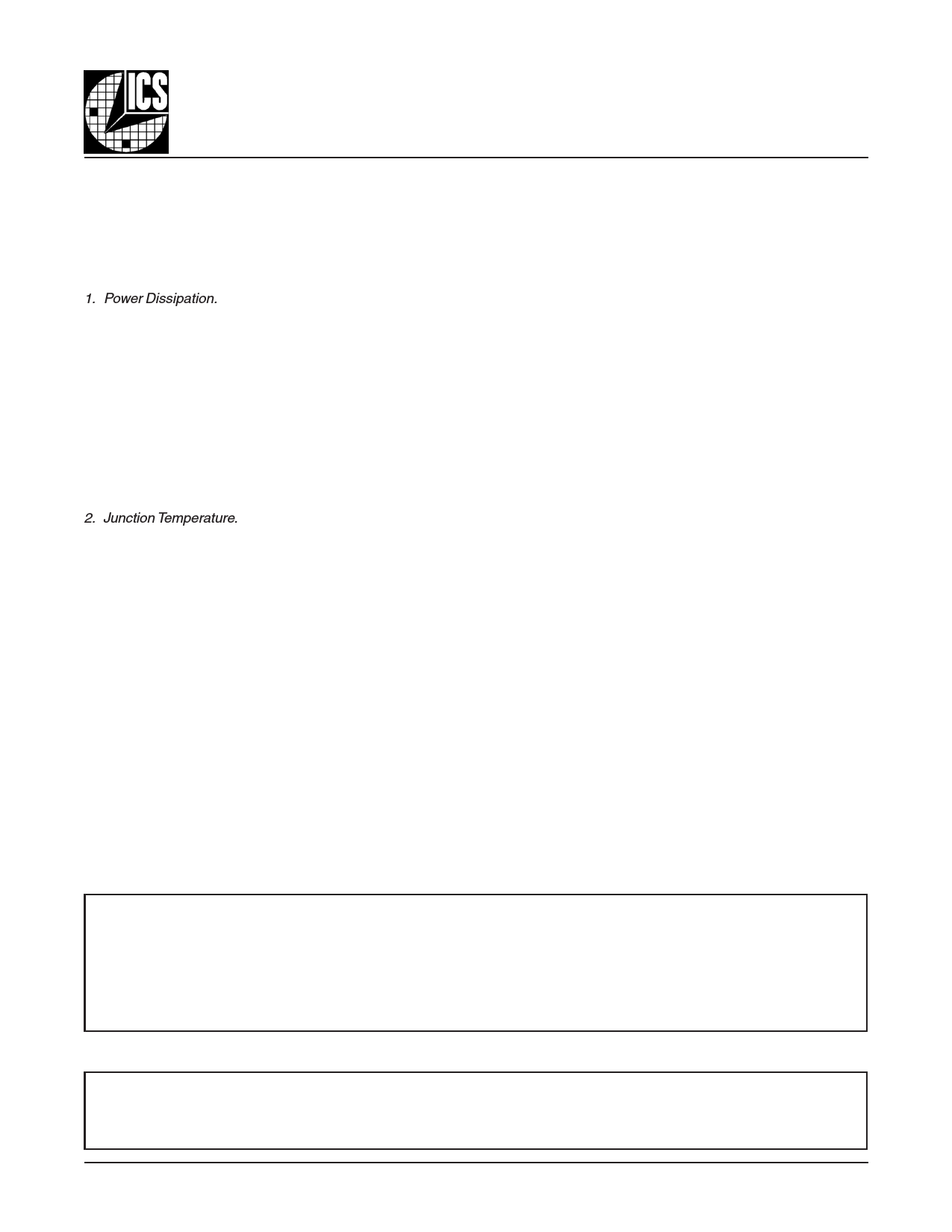

POWER CONSIDERATIONS

This section provides information on power dissipation and junction temperature for the ICS8735-01.

Equations and example calculations are also provided.

1. Power Dissipation.

The total power dissipation for the ICS8735-01 is the sum of the core power plus the power dissipated in the load(s).

The following is the power dissipation for VCC = 3.3V + 5% = 3.465V, which gives worst case results.

NOTE: Please refer to Section 3 for details on calculating power dissipated in the load.

• Power (core)MAX = VCC_MAX * IEE_MAX = 3.465V * 150mA = 520mW

• Power (outputs) = 30.2mW/Loaded Output pair

MAX

If all outputs are loaded, the total power is 5 * 30.2mW = 151mW

Total Power_MAX (3.465V, with all outputs switching) = 520mW + 151mW = 671mW

2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad and directly affects the reliability of the

device.The maximum recommended junction temperature for HiPerClockSTM devices is 125°C.

The equation for Tj is as follows: Tj = θJA * Pd_total + TA

Tj = Junction Temperature

θJA = Junction-to-Ambient Thermal Resistance

Pd_total = Total Device Power Dissipation (example calculation is in section 1 above)

TA = Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance θJA must be used . Assuming a

moderate air flow of 200 linear feet per minute and a multi-layer board, the appropriate value is 42.1°C/W per Table 7A below.

Therefore, Tj for an ambient temperature of 70°C with all outputs switching is:

70°C + 0.671W * 42.1°C/W = 98°C. This is well below the limit of 125°C

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow,

and the type of board (single layer or multi-layer).

TABLE 7A. THERMAL RESISTANCE θJA FOR 32-PIN LQFP, FORCED CONVECTION

θJA by Velocity (Linear Feet per Minute)

Single-Layer PCB, JEDEC Standard Test Boards

0

67.8°C/W

200

55.9°C/W

Multi-Layer PCB, JEDEC Standard Test Boards

47.9°C/W

42.1°C/W

500

50.1°C/W

39.4°C/W

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

TABLE 7B. θJAVS. AIR FLOW TABLE FOR 32 LEAD VFQFN PACKAGE

θJA 0 Air Flow (Linear Feet per Minute)

0

Multi-Layer PCB, JEDEC Standard Test Boards

34.8C/W

8735AY-01

www.icst.com/products/hiperclocks.html

11

REV. F NOVEMBER 12, 2004

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet ICS8735-01.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS8735-01 | ZERO DELAY CLOCK GENERATOR | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |