|

|

PDF KM732V787 Data sheet ( Hoja de datos )

| Número de pieza | KM732V787 | |

| Descripción | 128Kx32-Bit Synchronous Burst SRAM | |

| Fabricantes | Samsung Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de KM732V787 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

KM732V787

Document Title

128Kx32-Bit Synchronous Burst SRAM

Revision History

Rev. No. History

1.0 Initial draft

2.0 Modify Rev. No. from 0.0 to 1.0.

3.0 Add VDDQ Supply voltage( 2.5V )

128Kx32 Synchronous SRAM

Draft Date

May. 19. 1998

Jun. 02. 1998

Dec. 02. 1998

Remark

Final

Final

Final

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the

specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any ques-

tions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

- 1 - December 1998

Rev 3.0

1 page

KM732V787

128Kx32 Synchronous SRAM

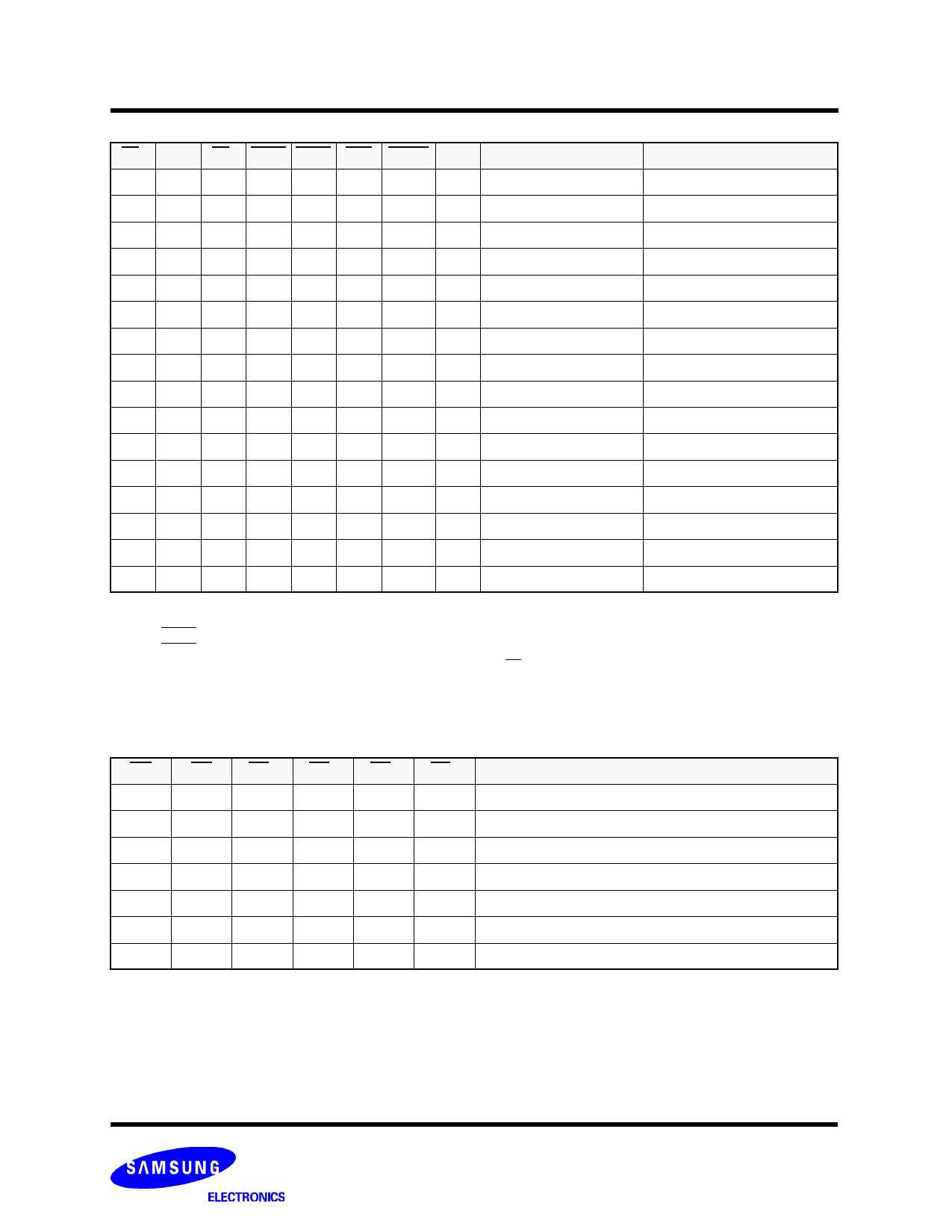

SYNCHRONOUS TRUTH TABLE

CS1 CS2 CS2 ADSP ADSC ADV WRITE CLK ADDRESS ACCESSED

HXXXLX X ↑

N/A

L LXLXX X ↑

N/A

LXHLXX X ↑

N/A

L LXXLX X ↑

N/A

LXHXLX X ↑

N/A

LHL LXX X ↑

External Address

LHLHLX L ↑

External Address

LHLHLX H ↑

External Address

XXXHHL H ↑

Next Address

HXXXHL H ↑

Next Address

XXXHHL L ↑

Next Address

HXXXHL L ↑

Next Address

XXXHHH H ↑

Current Address

HXXXHH H ↑

Current Address

XXXHHH L ↑

Current Address

HXXXHH L ↑

Current Address

Notes : 1. X means "Don′t Care".

2. The rising edge of clock is symbolized by ↑.

3. WRITE = L means Write operation in WRITE TRUTH TABLE.

WRITE = H means Read operation in WRITE TRUTH TABLE.

4. Operation finally depends on status of asynchronous input pins(ZZ and OE).

OPERATION

Not Selected

Not Selected

Not Selected

Not Selected

Not Selected

Begin Burst Read Cycle

Begin Burst Write Cycle

Begin Burst Read Cycle

Continue Burst Read Cycle

Continue Burst Read Cycle

Continue Burst Write Cycle

Continue Burst Write Cycle

Suspend Burst Read Cycle

Suspend Burst Read Cycle

Suspend Burst Write Cycle

Suspend Burst Write Cycle

WRITE TRUTH TABLE

GW

BW

WEa

WEb

WEc

WEd

OPERATION

HHXXXX

READ

H L HHHH

READ

HL LHHH

WRITE BYTE a

H L H L HH

WRITE BYTE b

HLHHL L

WRITE BYTE c and d

HL L L L L

WRITE ALL BYTEs

LXXXXX

WRITE ALL BYTEs

Notes : 1. X means "Don′t Care".

2. All inputs in this table must meet setup and hold time around the rising edge of CLK(↑).

- 5 - December 1998

Rev 3.0

5 Page

KM732V787

128Kx32 Synchronous SRAM

- 11 -

December 1998

Rev 3.0

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet KM732V787.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KM732V787 | 128Kx32-Bit Synchronous Burst SRAM | Samsung Semiconductor |

| KM732V789 | 128Kx32-Bit Synchronous Pipelined Burst SRAM | Samsung Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |