|

|

PDF XC18Vxxx Data sheet ( Hoja de datos )

| Número de pieza | XC18Vxxx | |

| Descripción | In-System Programmable Configuration PROMs | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XC18Vxxx (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

0

R

DS026 (v4.0) June 11, 2003

00

Features

• In-system programmable 3.3V PROMs for

configuration of Xilinx FPGAs

- Endurance of 20,000 program/erase cycles

- Program/erase over full commercial/industrial

voltage and temperature range (–40°C to +85°C)

• IEEE Std 1149.1 boundary-scan (JTAG) support

• Simple interface to the FPGA

• Cascadable for storing longer or multiple bitstreams

• Low-power advanced CMOS FLASH process

XC18V00 Series In-System

Programmable Configuration

PROMs

Product Specification

• Dual configuration modes

- Serial Slow/Fast configuration (up to 33 MHz)

- Parallel (up to 264 Mb/s at 33 MHz)

• 5V tolerant I/O pins accept 5V, 3.3V and 2.5V signals

• 3.3V or 2.5V output capability

• Available in PC20, SO20, PC44, and VQ44 packages

• Design support using the Xilinx Alliance and

Foundation series software packages.

• JTAG command initiation of standard FPGA

configuration

Description

Xilinx introduces the XC18V00 series of in-system program-

mable configuration PROMs (Figure 1). Devices in this 3.3V

family include a 4-megabit, a 2-megabit, a 1-megabit, and a

512-kilobit PROM that provide an easy-to-use, cost-effec-

tive method for re-programming and storing Xilinx FPGA

configuration bitstreams.

When the FPGA is in Master Serial mode, it generates a

configuration clock that drives the PROM. A short access

time after CE and OE are enabled, data is available on the

PROM DATA (D0) pin that is connected to the FPGA DIN

pin. New data is available a short access time after each ris-

ing clock edge. The FPGA generates the appropriate num-

ber of clock pulses to complete the configuration. When the

FPGA is in Slave Serial mode, the PROM and the FPGA

are clocked by an external clock.

CLK CE

When the FPGA is in Master-SelectMAP mode, the FPGA

generates a configuration clock that drives the PROM.

When the FPGA is in Slave-Parallel or Slave-SelectMAP

Mode, an external oscillator generates the configuration

clock that drives the PROM and the FPGA. After CE and

OE are enabled, data is available on the PROMs DATA

(D0-D7) pins. New data is available a short access time

after each rising clock edge. The data is clocked into the

FPGA on the following rising edge of the CCLK. A free-run-

ning oscillator can be used in the Slave-Parallel or

Slave-SelecMAP modes.

Multiple devices can be concatenated by using the CEO

output to drive the CE input of the following device. The

clock inputs and the DATA outputs of all PROMs in this

chain are interconnected. All devices are compatible and

can be cascaded with other members of the family or with

the XC17V00 one-time programmable Serial PROM family.

OE/Reset

TCK

TMS

TDI

TDO

Control

and

JTAG

Interface

Data

Address

Memory

Data

Serial

or

Parallel

Interface

CEO

D0 DATA

Serial or Parallel Mode

7

D[1:7]

Parallel Interface

CF

Figure 1: XC18V00 Series Block Diagram

DS026_01_090502

©2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at http://www.xilinx.com/legal.htm. All other

trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this fea-

ture, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you

may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any war-

ranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

DS026 (v4.0) June 11, 2003

Product Specification

www.xilinx.com

1-800-255-7778

1

1 page

R XC18V00 Series In-System Programmable Configuration PROMs

Xilinx FPGAs and Compatible PROMs

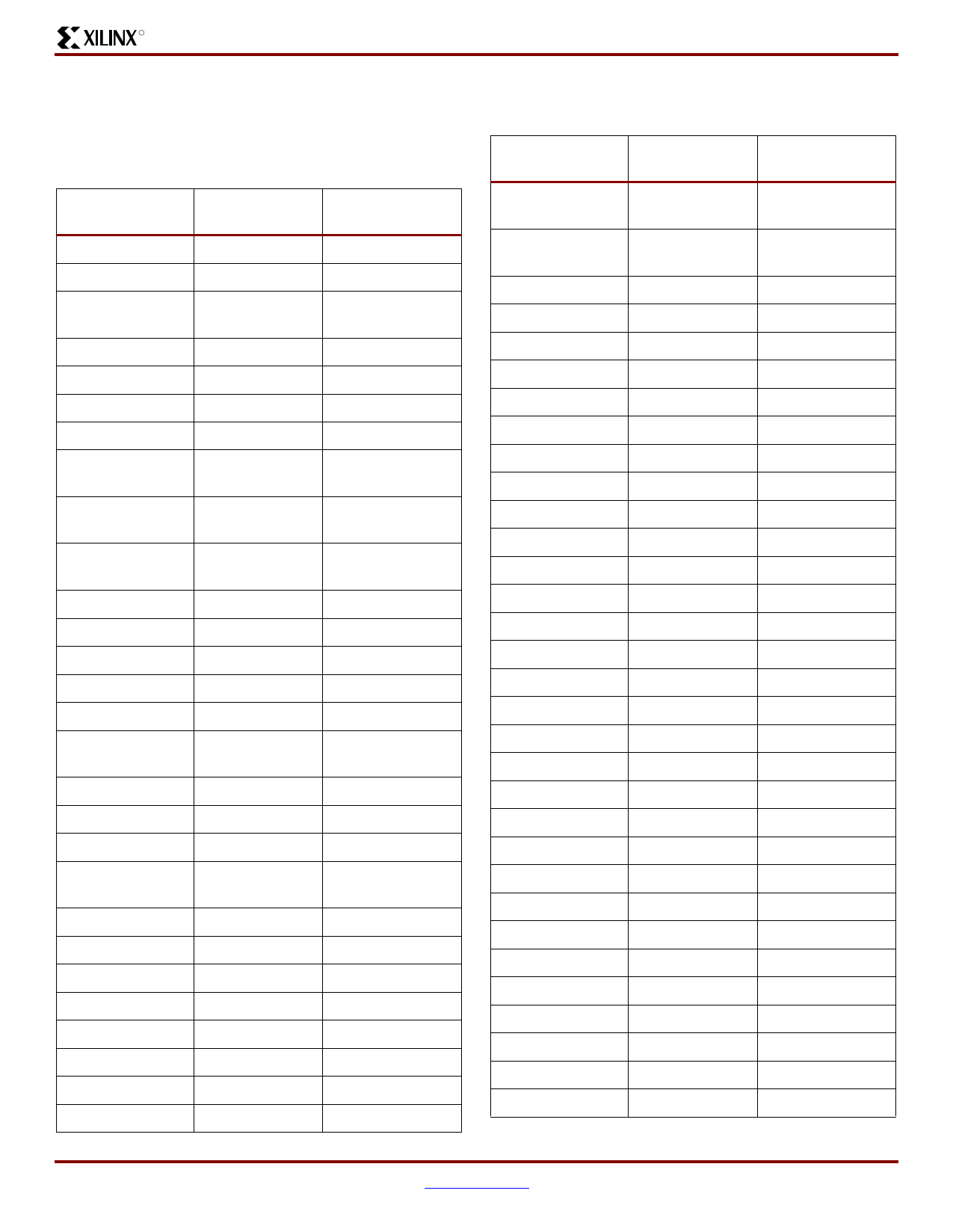

Table 2 provides a list of Xilinx FPGAs and compatible

PROMs.

Table 2: Xilinx FPGAs and Compatible PROMs

Device

Configuration

Bits

XC18V00

Solution

XC2VP2

1,305,440

XC18V02

XC2VP4

3,006,560

XC18V04

XC2VP7

4,485,472

XC18V04 +

XC18V512

XC2VP20

8,214,624

2 of XC18V04

XC2VP30

11,364,608

3 of XC18V04

XC2VP40

15,563,264

4 of XC18V04

XC2VP50

19,021,472

5 of XC18V04

XC2VP70

25,604,096

6 of XC18V04 +

XC18V512

XC2VP100

33,645,312

8 of XC18V04 +

XC18V512

XC2VP125

42,782,208

10 of XC18V04 +

XC18V01

XC2V40

360,096

XC18V512

XC2V80

635,296

XC18V01

XC2V250

1,697,184

XC18V02

XC2V500

2,761,888

XC18V04

XC2V1000

4,082,592

XC18V04

XC2V1500

5,659,296

XC18V04

+ XC18V02

XC2V2000

7,492,000

2 of XC18V04

XC2V3000

10,494,368

3 of XC18V04

XC2V4000

15,659,936

4 of XC18V04

XC2V6000

21,849,504

5 of XC18V04 +

XC18V02

XC2V8000

29,063,072

7 of XC18V04

XCV50

559,200

XC18V01

XCV100

781,216

XC18V01

XCV150

1,040,096

XC18V01

XCV200

1,335,840

XC18V02

XCV300

1,751,808

XC18V02

XCV400

2,546,048

XC18V04

XCV600

3,607,968

XC18V04

Table 2: Xilinx FPGAs and Compatible PROMs

Device

Configuration

Bits

XC18V00

Solution

XCV800

4,715,616

XC18V04 +

XC18V512

XCV1000

6,127,744

XC18V04 +

XC18V02

XCV50E

630,048

XC18V01

XCV100E

863,840

XC18V01

XCV200E

1,442,016

XC18V02

XCV300E

1,875,648

XC18V02

XCV400E

2,693,440

XC18V04

XCV405E

3,430,400

XC18V04

XCV600E

3,961,632

XC18V04

XCV812E

6,519,648

2 of XC18V04

XCV1000E

6,587,520

2 of XC18V04

XCV1600E

8,308,992

2 of XC18V04

XCV2000E

10,159,648

3 of XC18V04

XCV2600E

12,922,336

4 of XC18V04

XCV3200E

16,283,712

4 of XC18V04

XC2S15

197,696

XC18V512

XC2S30

336,768

XC18V512

XC2S50

559,200

XC18V01

XC2S100

781,216

XC18V01

XC2S150

1,040,096

XC18V01

XC2S200

1,335,840

XC18V02

XC2S50E

630,048

XC18V01

XC2S100E

863,840

XC18V01

XC2S150E

1,134,496

XC18V02

XC2S200E

1,442,016

XC18V02

XC2S300E

1,875,648

XC18V02

XC2S400E

2,693,440

XC18V04

XC2S600E

3,961,632

XC18V04

XC3S50

439,264

XC18V512

XC3S200

1,047,616

XC18V01

XC3S400

1,699,136

XC18V02

XC3S1000

3,223,488

XC18V04

DS026 (v4.0) June 11, 2003

Product Specification

www.xilinx.com

1-800-255-7778

5

5 Page

R XC18V00 Series In-System Programmable Configuration PROMs

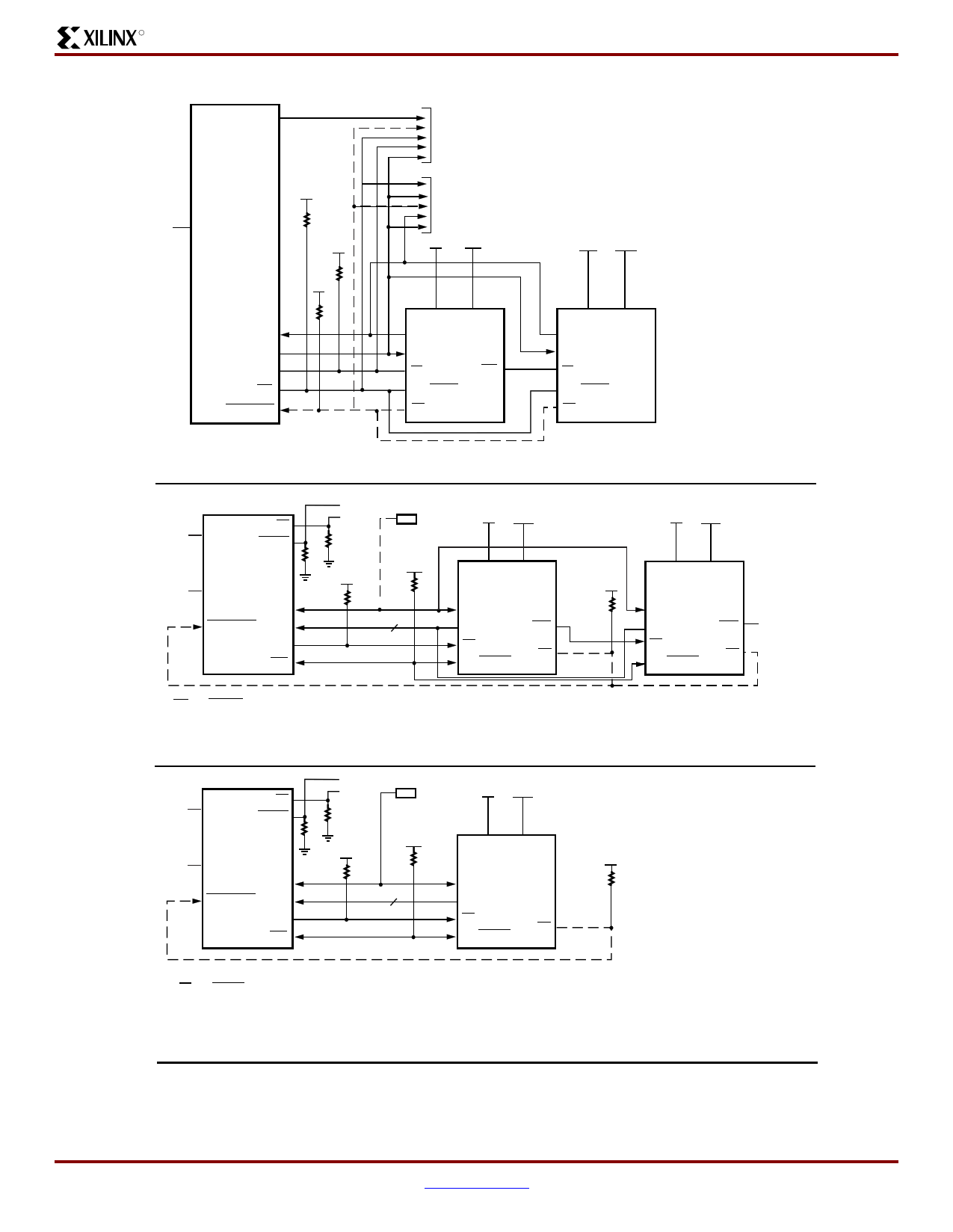

DOUT

FPGA

Modes(1)

Vcco(2)

4.7K

Vcco(2)

OPTIONAL

Daisy-chained

FPGAs with

different

configurations

OPTIONAL

Slave FPGAs

with identical

configurations

VCCINT VCCO(2)

(2)

VCCINT VCCO

Vcco(2)

DIN

CCLK

DONE

INIT

PROGRAM

4.7K

VCCINT VCCO

DATA

First

CLK PROM

CE CEO

OE/RESET

CF

VCCINT VCCO

DATA

CLK

CE

Cascaded

PROM

OE/RESET

CF

Notes:

1For Mode pin connections and Done pullup value, refer to the appropriate FPGA data sheet.

2For compatible voltages, refer to the appropriate FPGA data sheet.

(a) Master Serial Mode

Modes(2)

CS

WRITE

VIRTEX

Select MAP

I/O(1)

I/O(1)

1K 1K

Vcco(4)

External VCCINT VCCO(4)

Osc (3)

Vcco(4)

VCCINT VCCO

NC BUSY

(2) 4.7K

XC18Vxx

CCLK

PROGRAM D[0:7]

CLK

8

D[0:7]

CEO

DONE

INIT

CE

OE/RESET

CF

(4)

VCCINT VCCO

Vcco(4)

4.7K

VCCINT VCCO

XC18Vxx

CLK

D[0:7]

CEO

CE

OE/RESET

CF

Notes:

1CS and WRITE must be either driven Low or pulled down externally. One option is shown.

2For Mode pin connections and Done pullup value, refer to the appropriate FPGA data sheet.

3External oscillator required for Virtex/Virtex-E SelectMAP or Virtex-II/Virtex-II Pro Slave-SelectMAP modes.

4For compatible voltages, refer to the appropriate FPGA data sheet.

(b) Virtex/Virtex-E/Virtex-II/Virtex-II Pro SelectMAP Mode

Modes(2)

CS

WRITE

Spartan-II,

Spartan-IIE

I/O(1)

I/O(1)

1K 1K

Vcco(4)

External VCCINT VCCO(4)

Osc (3)

Vcco(4)

VCCINT VCCO

NC BUSY

(2) 3.3K XC18Vxx

CCLK

PROGRAM D[0:7]

CLK

8

D[0:7]

(4)

VCCINT

4.7K

DONE

INIT

CE

OE/RESET

CF

Notes:

1 CS and WRITE must be pulled down to be used as I/O. One option is shown.

2 For Mode pin connections and Done pullup value and if Drive Done configuration option is not active, refer to

the appropriate FPGA data sheet.

3 External oscillator required for Spartan-II/Spartan-IIE Slave-Parallel modes.

4 For compatible voltages, refer to the appropriate FPGA data sheet.

(c) Spartan-II/Spartan-IIE Slave-Parallel Mode

DS026_05_060403

Figure 7: (a) Master Serial Mode (b) Virtex/Virtex-E/Virtex-II Pro SelectMAP Mode (c) Spartan-II/Spartan-IIE

Slave-Parallel Mode (dotted lines indicate optional connection)

DS026 (v4.0) June 11, 2003

Product Specification

www.xilinx.com

1-800-255-7778

11

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet XC18Vxxx.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XC18Vxxx | In-System Programmable Configuration PROMs | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |