|

|

PDF DS1339 Data sheet ( Hoja de datos )

| Número de pieza | DS1339 | |

| Descripción | Serial Real-Time Clock | |

| Fabricantes | Dallas Semiconducotr | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS1339 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

DS1339

I2C Serial Real-Time Clock

www.maxim-ic.com

GENERAL DESCRIPTION

The DS1339 serial real-time clock (RTC) is a low-

power clock/date device with two programmable time-

of-day alarms and a programmable square-wave

output. Address and data are transferred serially

through an I2C* bus. The clock/date provides seconds,

minutes, hours, day, date, month, and year

information. The date at the end of the month is

automatically adjusted for months with fewer than 31

days, including corrections for leap year. The clock

operates in either the 24-hour or 12-hour format with

AM/PM indicator. The DS1339 has a built-in power-

sense circuit that detects power failures and

automatically switches to the backup supply,

maintaining time and date operation.

APPLICATIONS

Handhelds (GPS, POS Terminals)

Consumer Electronics (Set-Top Box, Digital

Recording, Network Appliance)

Office Equipment (Fax/Printers, Copier)

Medical (Glucometer, Medicine Dispenser)

Telecommunications (Routers, Switches, Servers)

Other (Utility Meter, Vending Machine, Thermostat,

Modem)

FEATURES

§ Real-Time Clock (RTC) Counts Seconds, Minutes,

Hours, Day, Date, Month, and Year with Leap-

Year Compensation Valid Up to 2100

§ Available in a Surface-Mount Package with an

Integrated Crystal (DS1339C)

§ I2C Serial Interface

§ Two Time-of-Day Alarms

§ Programmable Square-Wave Output

§ Oscillator Stop Flag

§ Automatic Power-Fail Detect and Switch Circuitry

§ Trickle-Charge Capability

§ Underwriters Laboratory (UL) Recognized

Pin Configurations appear at end of data sheet.

*I2C is a trademark of Philips Corp. Purchase of I2C components

from Maxim Integrated Products, Inc., or one of its sublicensed

Associated Companies, conveys a license under the Philips I2C

Patent Rights to use these components in an I2C system, provided

that the system conforms to the I2C Standard Specification as

defined by Philips.

ORDERING INFORMATION

PART

DS1339C-2

DS1339C-2+

DS1339C-3

DS1339C-3+

DS1339C-33

DS1339C-33+

DS1339U-2

DS1339U-3

DS1339U-3+

DS1339U-33

DS1339U-33+

TEMP RANGE

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

+ Denotes a lead-free/RoHS-compliant device.

## = second line, revision code

2 = 2.0V (VCC ±10%)

3 = 3.0V (VCC ±10%)

33 = 3.3V (VCC ±10%)

* A “+” on the top mark indicates a lead-free device.

VOLTAGE (V)

2.0

2.0

3.0

3.0

3.3

3.3

2.0

3.0

3.0

3.3

3.3

PIN-PACKAGE

16 SO (300 mils)

16 SO (300 mils)

16 SO (300 mils)

16 SO (300 mils)

16 SO (300 mils)

16 SO (300 mils)

8 mSOP

8 mSOP

8 mSOP

8 mSOP

8 mSOP

TOP MARK*

DS1339C-2

DS1339C-2

DS1339C-3

DS1339C-3

DS1339C-33

DS1339C-33

1339 ##-2

1339 ##-3

1339 ##-3

1339 ##-33

1339 ##-33

1 of 18

REV: 071205

1 page

DS1339 I2C Serial Real-Time Clock

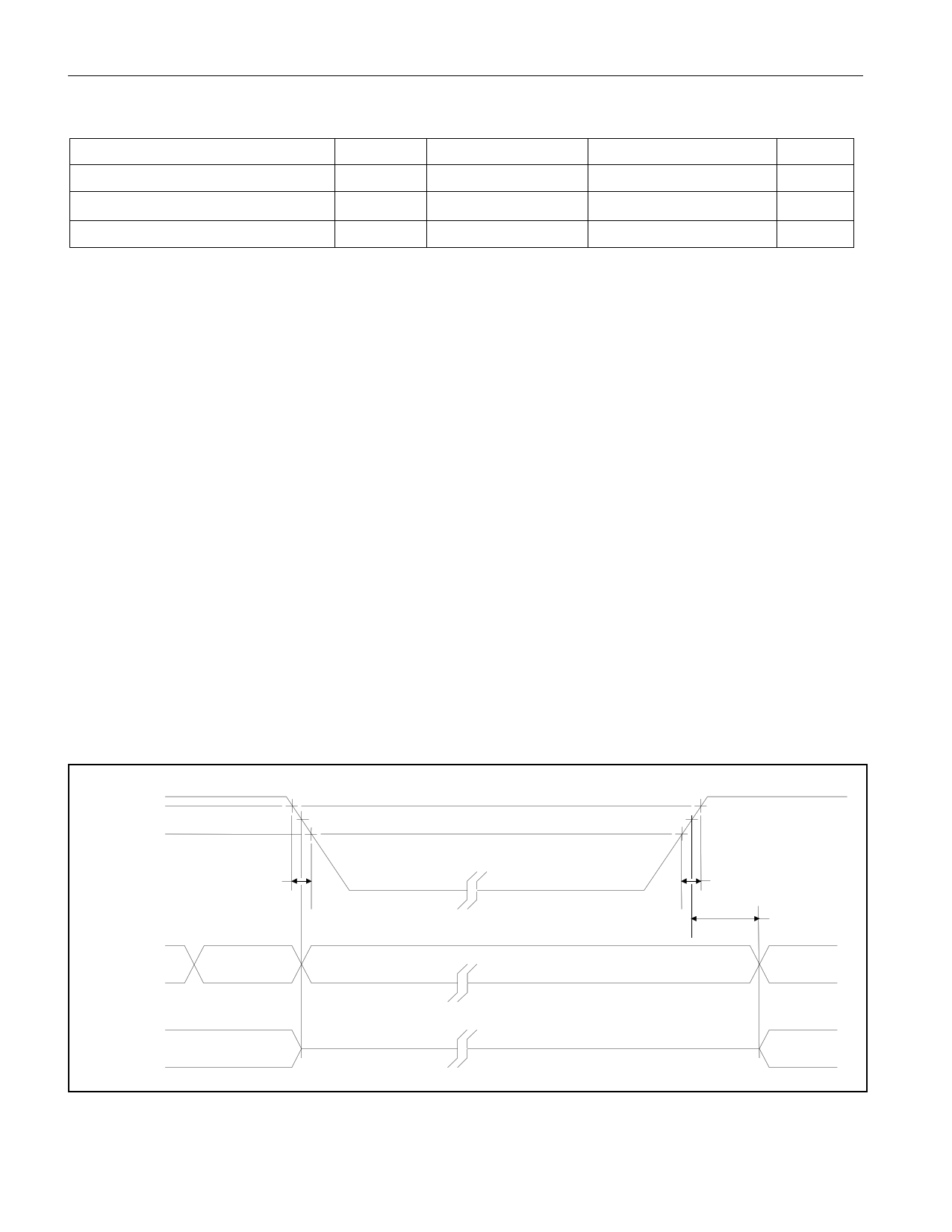

POWER-UP/DOWN CHARACTERISTICS

(TA = -40 C to +85°C) (Note 1, Figure 1)

PARAMETER

SYMBOL

CONDITIONS

Recovery at Power-Up

tREC (Note 14)

VCC Fall Time; VPF(MAX) to VPF(MIN)

tVCCF

VCC Rise Time; VPF(MIN) to VPF(MAX)

tVCCR

MIN TYP MAX UNITS

2 ms

300 ms

0 ms

WARNING: Under no circumstances are negative undershoots, of any amplitude, allowed when device is in

battery-backup mode.

Note 1:

Note 2:

Note 3:

Note 4:

Note 5:

Note 6:

Note 7:

Note 8:

Note 9:

Note 10:

Note 11:

Note 12:

Note 13:

Note 14:

Limits at -40°C are guaranteed by design and are not production tested.

SCL only.

SDA and SQW/INT.

ICCA—SCL at fSC max, VIL = 0.0V, VIH = VCC, trickle charger disabled.

Specified with the I2C bus inactive, VIL = 0.0V, VIH = VCC, trickle charger disabled.

Using recommended crystal on X1 and X2.

After this period, the first clock pulse is generated.

A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the VIHMIN of the SCL signal) to bridge

the undefined region of the falling edge of SCL.

The maximum tHD:DAT need only be met if the device does not stretch the LOW period (tLOW) of the SCL signal.

A fast-mode device can be used in a standard-mode system, but the requirement tSU:DAT ³ to 250ns must then be met. This is

automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW

period of the SCL signal, it must output the next data bit to the SDA line tR(MAX) + tSU:DAT = 1000 + 250 = 1250ns before the SCL line

is released.

CB—total capacitance of one bus line in pF.

Guaranteed by design. Not production tested.

The parameter tOSF is the period of time the oscillator must be stopped for the OSF flag to be set over the voltage range of 0.0V £

VCC £ VCCMAX and 1.3V £ VBACKUP £ 3.7V.

This delay applies only if the oscillator is running. If the oscillator is disabled or stopped, no power-up delay occurs.

Figure 1. Power-Up/Down Timing

VPF(MVACXC)

VPF(MIN)

tVCCF

INPUTS

RECOGNIZED

DON'T CARE

tVCCR

tREC

RECOGNIZED

OUTPUTS

VALID

HIGH-Z

VALID

5 of 18

5 Page

DS1339 I2C Serial Real-Time Clock

TIME AND DATE OPERATION

The time and date information is obtained by reading the appropriate register bytes. Figure 6 shows the RTC

registers. The time and date are set or initialized by writing the appropriate register bytes. The contents of the time

and date registers are in the BCD format. The DS1339 can be run in either 12-hour or 24-hour mode. Bit 6 of the

hours register is defined as the 12- or 24-hour mode-select bit. When high, the 12-hour mode is selected. In the

12-hour mode, bit 5 is the AM/PM bit with logic high being PM. In the 24-hour mode, bit 5 is the second 10-hour bit

(20 to 23 hours). All hours values, including the alarms, must be re-entered whenever the 12/24-hour mode bit is

changed. The century bit (bit 7 of the month register) is toggled when the years register overflows from 99 to 00.

The day-of-week register increments at midnight. Values that correspond to the day of week are user-defined, but

must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday and so on). Illogical time and date entries result

in undefined operation.

When reading or writing the time and date registers, secondary (user) buffers are used to prevent errors when the

internal registers update. When reading the time and date registers, the user buffers are synchronized to the

internal registers on any start or stop, and when the address pointer rolls over to zero. The countdown chain is

reset whenever the seconds register is written. Write transfers occurs on the acknowledge pulse from the device.

To avoid rollover issues, once the countdown chain is reset, the remaining time and date registers must be written

within one second. If enabled, the 1Hz square-wave output transitions high 500ms after the seconds data transfer,

provided the oscillator is already running.

ALARMS

The DS1339 contains two time of day/date alarms. Alarm 1 can be set by writing to registers 07h to 0Ah. Alarm 2

can be set by writing to registers 0Bh to 0Dh. The alarms can be programmed (by the Alarm Enable and INTCN

bits of the Control Register) to activate the SQW/INT output on an alarm match condition. Bit 7 of each of the time

of day/date alarm registers are mask bits (Table 2). When all the mask bits for each alarm are logic 0, an alarm

only occurs when the values in the timekeeping registers 00h to 06h match the values stored in the time of

day/date alarm registers. The alarms can also be programmed to repeat every second, minute, hour, day, or date.

Table 2 shows the possible settings. Configurations not listed in the table result in illogical operation.

The DY/DT bits (bit 6 of the alarm day/date registers) control whether the alarm value stored in bits 0 to 5 of that

register reflects the day of the week or the date of the month. If DY/DT is written to a logic 0, the alarm is the result

of a match with date of the month. If DY/DT is written to a logic 1, the alarm is the result of a match with day of the

week.

The device checks for an alarm match once per second. When the RTC register values match alarm register

settings, the corresponding Alarm Flag ‘A1F’ or ‘A2F’ bit is set to logic 1. If the corresponding Alarm Interrupt

Enable ‘A1IE’ or ‘A2IE’ is also set to logic 1 and the INTCN bit is set to logic 1, the alarm condition activates the

SQW/INT) signal. If the BBSQI bit is set to 1, the INT output activates while the part is being powered by VBACKUP.

The alarm output remains active until the alarm flag is cleared by the user.

11 of 18

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet DS1339.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS1330AB | (DS1330Y / DS1330AB) 256k Nonvolatile SRAM with Battery Monitor | Dallas Semiconducotr |

| DS1330W | 3.3V 256K Nonvolatile SRAM with Battery Monitor | Dallas Semiconducotr |

| DS1330Y | (DS1330Y / DS1330AB) 256k Nonvolatile SRAM with Battery Monitor | Dallas Semiconducotr |

| DS1336 | Afterburner Chip | Dallas Semiconducotr |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |