|

|

PDF DS1807 Data sheet ( Hoja de datos )

| Número de pieza | DS1807 | |

| Descripción | Addressable Dual Audio Taper Potentiometer | |

| Fabricantes | Dallas Semiconducotr | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS1807 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

DS1807

Addressable Dual Audio Taper Potentiometer

www.dalsemi.com

FEATURES

§ Operates from 3V or 5V Power Supplies

§ Ultra-low power consumption

§ Two digitally controlled, 65-position

potentiometers

§ Logarithmic resistor characteristics (1 dB per

step)

§ Zero-crossing detection eliminates noise

caused by discrete wiper changes

§ Addressable using 3-Chip Select Inputs

§ Serial/Synchronous Bus Inputs

§ Operating Temperature Range:

- Industrial: -40°C to +85°C

§ Standard Resistance Value: 45 kΩ

PIN DESCIPTION

L0, L1

- Low End of Resistor

H0, H1

- High End of Resistor

W0,W1

- Wiper Terminal of Resistor

VCC

A0..A2

- 3V/5V Power Supply Input

- Chip Select Inputs

SDA

- Serial Data I/O

SCL - Serial Clock Input

GND

- Ground

AGND

- Analog Ground

NC - No connection

PIN ASSIGNMENT

GND

A2

A1

A0

W0

L0

H0

1

2

3

4

5

6

7

14 VCC

13 SCL

12 SDA

11 AGND

10 H1

9 L1

8 W1

DS1807 14-Pin DIP (300-mil)

DS1807E 14-Pin TSSOP (173-mil)

GND

A2

A1

NC

A0

W0

L0

H0

1

2

3

4

5

6

7

8

16 VCC

15 NC

14 SCL

13 SDA

12 AGND

11 H1

10 L1

9 W1

DS1807S 16-Pin SOIC (300-mil)

See mech. Drawings Section

DESCRIPTION

The DS1807 Addressable Dual Audio Taper Potentiometer is a dual audio taper potentiometer having a

logarithmic resistive characteristic. Each potentiometer has a total of 65 wiper positions including the

mute position. Adjacent wiper positions are separated by 1 dB giving a total attenuation range of 64 dB.

When the wipers are in the mute position, attenuation in excess of 90 dB is achieved. The DS1807 also

provides a zero-crossing detection capability. This capability eliminates noise caused by discrete wiper

position changes. The DS1807 is controlled via a two-input, serial synchronous interface that provides the

capability of addressing up to eight different DS1807s. Addressability is obtained via communication

protocol and three (3) address select inputs A0, A1, and A2. Communication protocol allows for the exact

positioning of the DS1807 wiper’s position. Additionally, communication protocol allows for

independent or simultaneous setting of the two potentiometers' wipers. Wiper positions can also be read

via the 2-wire serial interface.

1 of 13

110499

1 page

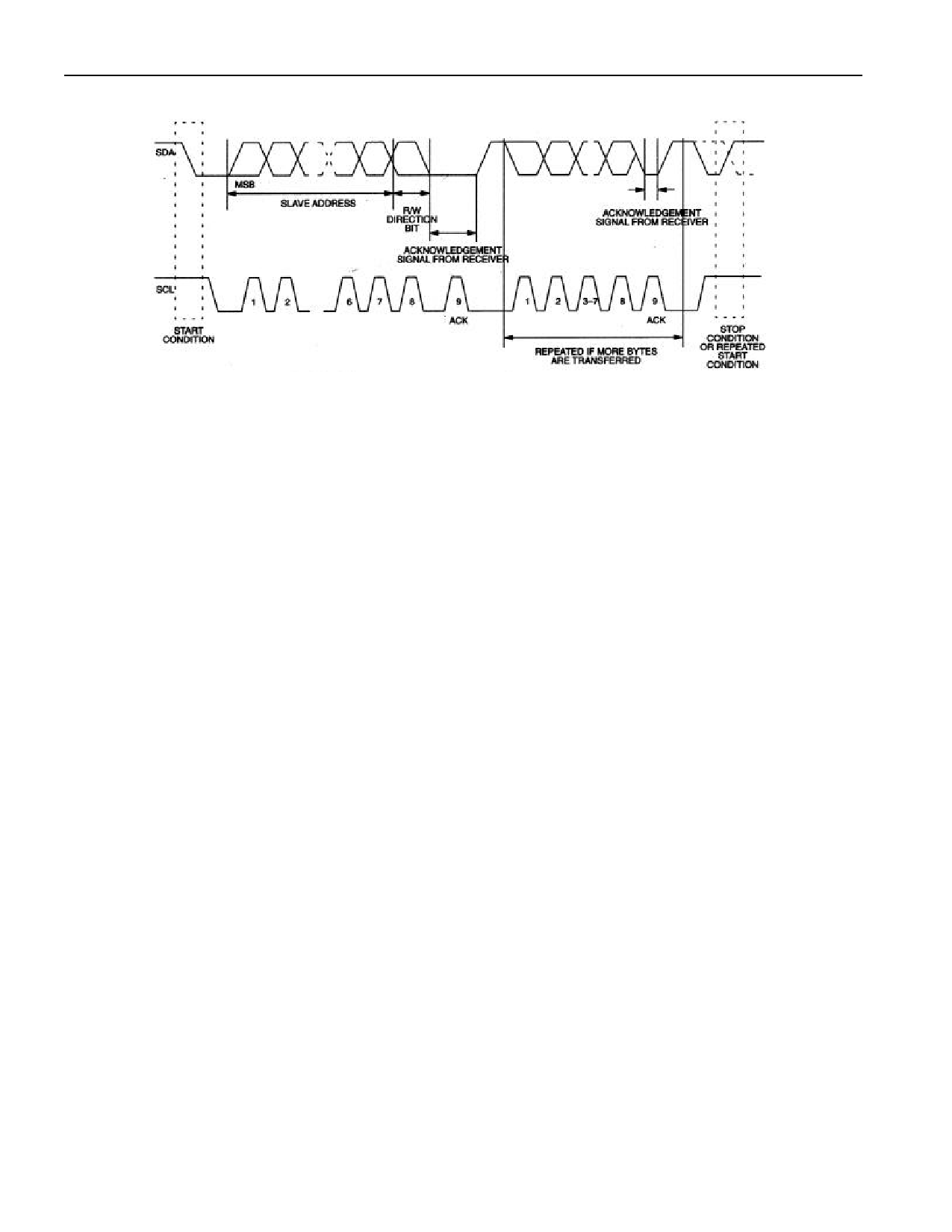

2-WIRE DATA TRANSFER OVERVIEW Figure 4

DS1807

Accordingly, the following bus conditions have been defined:

Bus not busy: Both data and clock lines remain HIGH.

Start data transfer: A change in the state of the data line, from HIGH to LOW, while the clock is

HIGH, defines a START condition.

Stop data transfer: A change in the state of the data line, from LOW to HIGH, while the clock line is

HIGH, defines the STOP condition.

Data valid: The state of the data line represents valid data when, after a START condition, the data line

is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed

during the LOW period of the clock signal. There is one clock pulse per bit of data. Figure 4 details how

data transfer is accomplished on the 2-wire bus. Depending upon the state of the R/W bit, two types of

data transfer are possible:

Each data transfer is initiated with a START condition and terminated with a STOP condition. The

number of data bytes transferred between START and STOP conditions is not limited, and is determined

by the master device. The information is transferred byte-wise and each receiver acknowledges with a 9th

bit.

Within the bus specifications a regular mode (100 kHz clock rate) and a fast mode (400 kHz clock rate)

are defined. The DS1807 works in both modes.

Acknowledge: Each receiving device, when addressed, is obliged to generate an acknowledge after the

reception of each byte. The master device must generate an extra clock pulse which is associated with this

acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a

way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of

course, setup and hold times must be taken into account. A master must signal an end of data to the slave

by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case,

the slave must leave the data line HIGH to enable the master to generate the STOP condition.

5 of 13

110499

5 Page

ANALOG RESISTOR CHARACTERISTICS

PARAMETER

SYMBOL MIN

End to End Resistor Tolerance

Absolute Tolerance

Interchannel Matching

-20

-1

-0.5

Tap-to-Tap

-0.25

-3 dB Cutoff Frequency

Temperature Coefficient

fcutoff

700

Total Harmonic Distortion

(V IN =1 V RMS , 1 kHz, Tap

= -6 dB)

Output Noise (20 Hz to 20 kHz,

Grounded Input, Tap = -6 dB)

Digital Feedthrough

(20 Hz to 20 kHz, Tap = -6 dB)

Interchannel Isolation

(1 kHz, Tap = -6 dB)

Mute Control Active

THD

DS1807

(-40°C to +85°C;VCC=2.7V to 5.5V)

TYP

MAX UNITS NOTES

+20 % 17

+1 dB 10

+0.5 dB 15

+0.25

dB

11

kHz 14

750 ppm/°C

0.002

% 14

2.2

-90

-100

-100

µVRMS

dB

dB

dB

14

14

14

AC ELECTRICAL CHARACTERISTICS

PARAMETER

SYMBOL MIN

SCL Clock Frequency

Bus Free Time Between STOP and

START Condition

Hold Time (Repeated) START

Condition

Low Period of SCL Clock

High Period of SCL Clock

Data Hold Time

fSCL

tBUF

tHD:STA

tLOW

tHIGH

tHD:DAT

0

0

1.3

4.7

0.6

4.0

1.3

4.7

0.6

4.0

0

0

(-40°C to +85°C;VCC=2.7V to 5.5V)

TYP MAX UNITS NOTES

400 kHz

*

100 **

µs *

**

µs 5

µs

µs

0.9 µs 6,7

Data Set-Up Time

Rise Time of both SDA and SCL

Signals

Fall Time of both SDA and SCL

Signals

Set-Up Time for STOP Condition

Capacitive Load for each Bus Line

*fast mode

**standard mode

tSU:DAT

tR

tF

tSU:STO

CR

100

250

20+0.1CR

20+0.1CR

0.6

4.0

11 of 13

300

1000

300

300

400

ns 8

ns 9

ns 9

µs

pF

110499

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet DS1807.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS1800 | Dual Inverting Log Gain/Attenuator | Dallas Semiconducotr |

| DS1800-3 | AC-DC / Distributed Power Front-End 1U | Emerson |

| DS1801 | Dual Audio Taper Potentiometer | Dallas Semiconducotr |

| DS1802 | Dual Audio Taper Potentiometer With Pushbutton Control | Dallas Semiconducotr |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |