|

|

PDF OR2C15A Data sheet ( Hoja de datos )

| Número de pieza | OR2C15A | |

| Descripción | Field-Programmable Gate Arrays | |

| Fabricantes | Lattice | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de OR2C15A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Data Sheet

October 2003

ORCA® Series 2

Field-Programmable Gate Arrays

Features

■ High-performance, cost-effective, low-power

0.35 µm CMOS technology (OR2CxxA), 0.3 µm CMOS

technology (OR2TxxA), and 0.25 µm CMOS technology

(OR2TxxB), (four-input look-up table (LUT) delay less

than 1.0 ns with -8 speed grade)

■ High density (up to 43,200 usable, logic-only gates; or

99,400 gates including RAM)

■ Up to 480 user I/Os (OR2TxxA and OR2TxxB I/Os are

5 V tolerant to allow interconnection to both 3.3 V and

5 V devices, selectable on a per-pin basis)

■ Four 16-bit look-up tables and four latches/flip-flops per

PFU, nibble-oriented for implementing 4-, 8-, 16-, and/or

32-bit (or wider) bus structures

■ Eight 3-state buffers per PFU for on-chip bus structures

■ Fast, on-chip user SRAM has features to simplify RAM

design and increase RAM speed:

— Asynchronous single port: 64 bits/PFU

— Synchronous single port: 64 bits/PFU

— Synchronous dual port: 32 bits/PFU

■ Improved ability to combine PFUs to create larger RAM

structures using write-port enable and 3-state buffers

■ Fast, dense multipliers can be created with the multiplier

mode (4 x 1 multiplier/PFU):

— 8 x 8 multiplier requires only 16 PFUs

— 30% increase in speed

■ Flip-flop/latch options to allow programmable priority of

synchronous set/reset vs. clock enable

■ Enhanced cascadable nibble-wide data path

capabilities for adders, subtractors, counters, multipliers,

and comparators including internal fast-carry operation

■ Innovative, abundant, and hierarchical nibble-

oriented routing resources that allow automatic use of

internal gates for all device densities without sacrificing

performance

■ Upward bit stream compatible with the ORCA ATT2Cxx/

ATT2Txx series of devices

■ Pinout-compatible with new ORCA Series 3 FPGAs

■ TTL or CMOS input levels programmable per pin for the

OR2CxxA (5 V) devices

■ Individually programmable drive capability:

12 mA sink/6 mA source or 6 mA sink/3 mA source

■ Built-in boundary scan (IEEE*1149.1 JTAG) and

3-state all I/O pins, (TS_ALL) testability functions

■ Multiple configuration options, including simple, low pin-

count serial ROMs, and peripheral or JTAG modes for in-

system programming (ISP)

■ Full PCI bus compliance for all devices

■ Supported by industry-standard CAE tools for design

entry, synthesis, and simulation with ispLEVER Develop-

ment System support (for back-end implementation)

■ New, added features (OR2TxxB) have:

— More I/O per package than the OR2TxxA family

— No dedicated 5 V supply (VDD5)

— Faster configuration speed (40 MHz)

— Pin selectable I/O clamping diodes provide 5V or 3.3V

PCI compliance and 5V tolerance

— Full PCI bus compliance in both 5V and 3.3V PCI sys-

tems

* IEEE is a registered trademark of The Institute of Electrical and

Electronics Engineers, Inc.

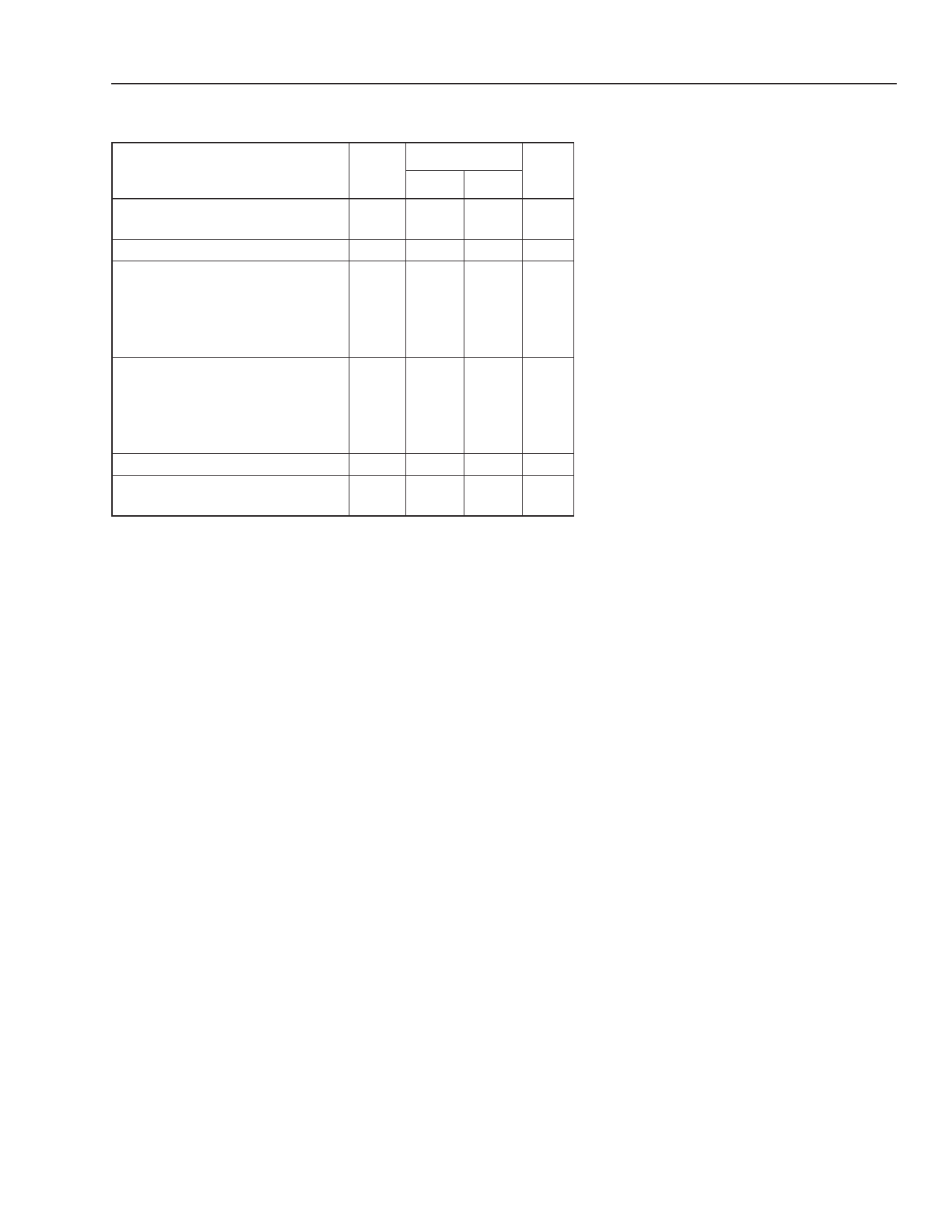

Table 1. ORCA Series 2 FPGAs

Device

OR2C04A/OR2T04A

OR2C06A

OR2C08A/OR2T08A

OR2C10A/OR2T10A

OR2C12A

OR2C15A/OR2T15A/OR2T15B

OR2C26A/OR2T26A

OR2C40A/OR2T40A/OR2T40B

Usable

Gates*

4,800—11,000

6,900—15,900

9,400—21,600

12,300—28,300

15,600—35,800

19,200—44,200

27,600—63,600

43,200—99,400

# LUTs Registers

400

576

784

1024

1296

1600

2304

3600

400

576

724

1024

1296

1600

2304

3600

Max User

RAM Bits

6,400

9,216

12,544

16,384

20,736

25,600

36,864

57,600

User

I/Os

160

192

224

256

288

320

384

480

Array Size

10 x 10

12 x 12

14 x 14

16 x 16

18 x 18

20 x 20

24 x 24

30 x 30

* The first number in the usable gates column assumes 48 gates per PFU (12 gates per four-input LUT/FF pair) for logic-only designs. The

second number assumes 30% of a design is RAM. PFUs used as RAM are counted at four gates per bit, with each PFU capable of

implementing a 16 x 4 RAM (or 256 gates) per PFU.

1 page

Data Sheet

October 2003

ORCA Series 2 FPGAs

Table 4. ORCA Series 2TB System Performance

Function

16-bit loadable up/down

counter

16-bit accumulator

8 x 8 parallel multiplier:

— Multiplier mode,

unpipelined1

— ROM mode, unpipelined2

— Multiplier mode, pipelined3

32 x 16 RAM:

— Single port (read and write/

cycle)4

— Single port5

— Dual port6

36-bit parity check (internal)

32-bit address decode

(internal)

#

PFUs

4

Speed Grade

-7 -8

131.6 149.3

Unit

MHz

4 131.6 149.3 MHz

22 37.7 44.8 MHz

9 103.1 120.5 MHz

44 123.5 142.9 MHz

9 57.5 69.4 MHz

9 97.7 112.4 MHz

16 97.7 112.4 MHz

4 6.1 5.1 ns

3.25 4.8 4.0 ns

1.Implemented using 4 x 1 multiplier mode (unpipelined), register-to-register, two 8-bit inputs, one 16-bit output.

2. Implemented using two 16 x 12 ROMs and one 12-bit adder, one 8-bit input, one fixed operand, one 16-bit output.

3. Implemented using 4 x 1 multiplier mode (fully pipelined), two 8-bit inputs, one 16-bit output (28 of 44 PFUs contain only pipelining registers).

4. Implemented using 16 x 4 synchronous single-port RAM mode allowing both read and write per clock cycle, including write/read address

multiplexer.

5. Implemented using 16 x 4 synchronous single-port RAM mode allowing either read or write per clock cycle, including write/read address

multiplexer.

6. Implemented using 16 x 2 synchronous dual-port RAM mode.

Lattice Semiconductor

5

5 Page

Data Sheet

October 2003

ORCA Series 2 FPGAs

Programmable Logic Cells (continued)

F5M and F5X Modes—Special Function Modes

The PFU contains logic to implement two special func-

tion modes which are variations on the F5 mode. As

with the F5 mode, the LUT implements two indepen-

dent five-input functions. Figure 6 and Figure 7 show

the schematics for F5M and F5X modes, respectively.

The F5X and F5M functions differ from the basic F5A/

F5B functions in that there are three logic gates which

have inputs from the two 5-input LUT outputs. In some

cases, this can be used for faster and/or wider logic

functions.

As can be seen, two of the three inputs into the NAND,

XOR, and MUX gates, F0 and F3, are from the LUT.

The third input is from the C0 input into PFU. Since the

C0 input bypasses the LUTs, it has a much smaller

delay through the PFU than for all other inputs into the

special PFU gates. This allows multiple PFUs to be

cascaded together while reducing the delay of the criti-

cal path through the PFUs. The output of the first spe-

cial function (either XOR or MUX) is F1. Since the XOR

and MUX share the F1 output, the F5X and F5M

modes are mutually exclusive. The output of the NAND

PFU gate is F2 and is always available in either mode.

To use either the F5M or F5X functions, the LUT must

be in the F5A/F5B mode; i.e., only 5-input LUTs

allowed. In both the F5X and F5M functions, the out-

puts of the five-input combinatorial functions, F0 and

F3, are also usable simultaneously with the special

PFU gate outputs.

The output of the MUX is:

F1 = (HLUTA & C0) + (HLUTB & C0)

F1 = (F3 & C0) + (F0 & C0)

The output of the exclusive OR is:

F1 = HLUTA ⊕ HLUTB ⊕ C0

F1 = F3 ⊕ F0 ⊕ C0

The output of the NAND is:

F2 = HLUTA & HLUTB & C0

F2 = F3 & F0 & C0

C0

A4 A4

A3 A3 QLUT3

A2 A2

F3

A1 A1 QLUT2

A0 A0

F3

F2

B4 B4

B3 B3 QLUT1

B2 B2

F0

B1 B1 QLUT0

B0 B0

F1

F0

5-2754(F).r3

Figure 6. F5M Mode—Multiplexed Function of Two

Independent Five-Input Variable

Functions

C0

A4 A4 HLUTA

A3 A3

A2 A2

F3

A1 A1

A0 A0

F3

F2

B4 B4 HLUTB

B3 B3

B2 B2

F0

B1 B1

B0 B0

F1

F0

5-2755(F).r2

Figure 7. F5X Mode—Exclusive OR Function of Two

Independent Five-Input Variable

Functions

Lattice Semiconductor

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet OR2C15A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| OR2C15A | Field-Programmable Gate Arrays | Agere Systems |

| OR2C15A | Field-Programmable Gate Arrays | Lattice |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |