|

|

PDF NJU8725 Data sheet ( Hoja de datos )

| Número de pieza | NJU8725 | |

| Descripción | CLASS D AMPLIFIER FOR DIGITAL AUDIO | |

| Fabricantes | New Japan Radio | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NJU8725 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

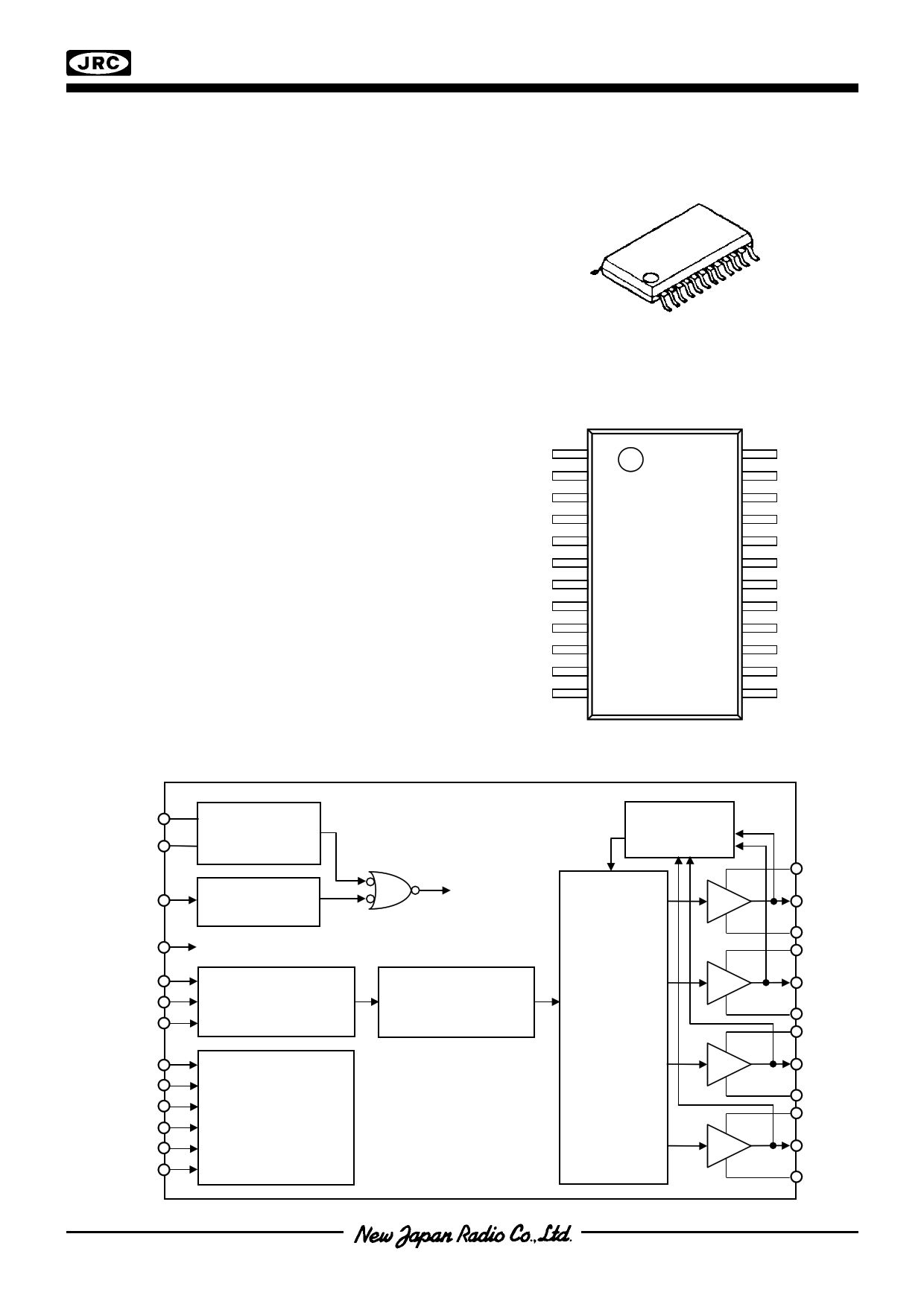

NJU8725

PRELIMINARY

CLASS D AMPLIFIER FOR DIGITAL AUDIO

! GENERAL DESCRIPTION

The NJU8725 is an 800mW-output class D

Amplifier featuring 6th ∆Σ modulation. It includes

Digital Attenuator, Mute, and De-emphasis circuits. It

converts Digital source input to PWM signal output

which is output PWM signal converted to analog

signal with simple external LC Filter. The NJU8725

realizes very high power-efficiency by class D

operation. Therefore, it is suitable for battery-powered

applications and others.

! PACKAGE OUTLINE

NJU8725V

! FEATURES

! PIN CONFIGURATION

# Stereo BTL Power Amplifier

# Sixth-order 32fS Over Sampling ∆Σ & PWM

# Internal 8fS Over Sampling Digital Filter

# Sampling Frequency : 96kHz (Max.)

# De-Emphasis

: 32kHz, 44.1kHz, 48kHz

# System Clock

: 256fS

# Digital Processing : Attenuator 107step, LOG Curve

VDD

STBY

TEST

MUTE

VDDL

: Mute

OUTLP

#

#

Digital Audio Interface : 16bit, 18bit

: I2S, LSB Justified, MSB Justified

Short Circuit Protection

VSSL

OUTLN

# Operating Voltage : 3.0 to 3.6V

VDDL

# Driving Voltage

: VDD to 5.25V

# C-MOS Technology

# Package Outline

: SSOP24

MODE

RST

VSS

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

F0/DATA

F1/REQ

F2/SCK

DIN

VDDR

OUTRP

VSSR

OUTRN

VDDR

LRCK

BCK

MCK

! BLOCK DIAGRAM

VDD

VSS

RST

MCK

LRCK

BCK

DIN

MUTE

STBY

MODE

F0/DATA

F1/REQ

F2/SCK

Power On

Reset Circuit

Synchronization

Circuit

Serial

Audio Data

Interface

System

Control

Short Circuit

Protection

8fS

Over Sampling

Digital Filter

32fS 6th ∆Σ

&

PWM

VDDL

OUTLP

VSSL

VDDL

OUTLN

VSSL

VDDR

OUTRP

VSSR

VDDR

OUTRN

VSSR

-1-

1 page

NJU8725

(8) Serial Audio Data Interface

(8-1) Input Data Format Selection

The digital audio interface format is selected out of I2S, MSB Justified or LSB Justified, and 16 bits or 18

bits data length.

(8-2) Input Timing

Digital audio signal data into DIN terminal is fetched into the internal shift register by BCK signal rising

edge. The fetched data in the shift register are transferred by rising edge or falling edge of LRCK as

shown below:

Data Format

I2S

MSB Justified

LSB Justified

Rising Edge

Lch Input Register

Rch Input Register

Rch Input Register

Falling Edge

Rch Input Register

Lch Input Register

Lch Input Register

BCK and LRCK must be synchronized with MCK.

LRCK

BCK

DIN

Left Channel

Right Channel

15 14 13

10

15 14 13

Figure 3.1. 16 bits I2S Data Format

10

LRCK

BCK

DIN

Left Channel

Right Channel

15 14 13

10

15 14 13

10

Figure 3.2. 16 bits MSB Justified Data Format

15

LRCK

BCK

DIN 0

Left Channel

Right Channel

15 14

3210

15 14

Figure 3.3. 16 bits LSB Justified Data Format

3210

-5-

5 Page

NJU8725

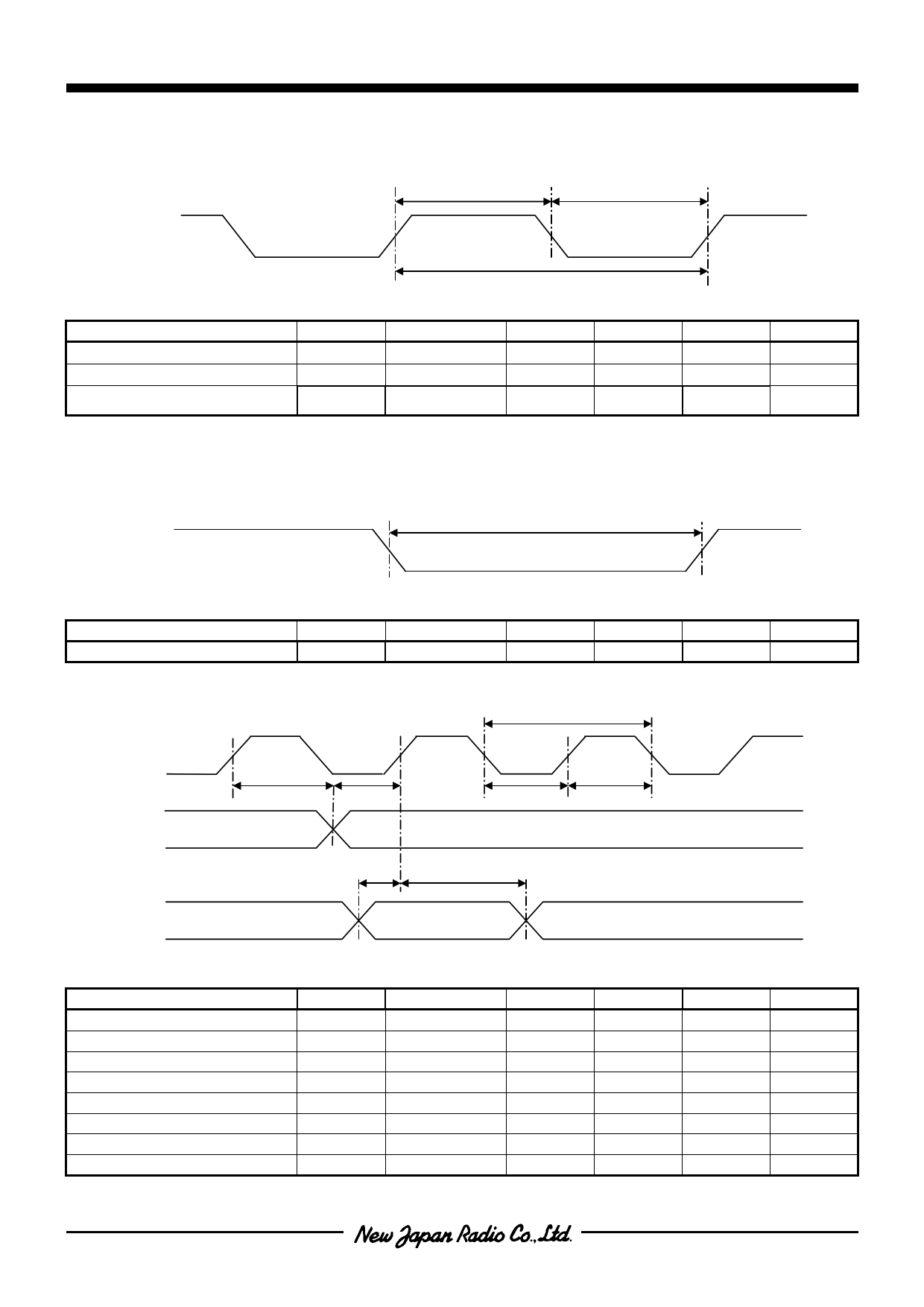

! TIMING CHARACTERISTICS

• Master Clock Input

MCK

tMCKH

tMCKL

PARAMETER

MCK Frequency

MCK Pulse Width (H)

MCK Pulse Width (L)

SYMBOL

fMCKI

tMCKH

tMCKL

(Ta=25°C, VDD=VDDL=VDDR=3.3V, unless otherwise noted)

CONDITIONS

MIN.

TYP.

MAX.

UNIT

256fS

7.28

-

27.648

MHz

12 -

- ns

12 -

- ns

Note 6) tMCKI shows the cycle of the MCK signal.

• Reset Input

RST

PARAMETER

Reset Low Level Width

tRST

SYMBOL

tRST

(Ta=25°C, VDD=VDDL=VDDR=3.3V, unless otherwise noted)

CONDITIONS

MIN.

TYP.

MAX.

UNIT

3 - - ms

• Digital Audio Signal Interface

BCK

LRCK

tBLR

tLRB

tDS

DIN

tBCLK

tBCKL

tBCKH

tDH

PARAMETER

Audio DAC Sampling Rate

DIN Setup Time

DIN Hold Time

BCK Period

BCK Pulse Width (H)

BCK Pulse Width (L)

LRCK Hold Time

LRCK Setup Time

SYMBOL

fS

tDS

tDH

tBCLK

tBCKH

tBCKL

tBLR

tLRB

(Ta=25°C, VDD=VDDL=VDDR=3.3V, unless otherwise noted)

CONDITIONS

MIN.

TYP.

MAX.

UNIT

28 - 100 KHz

20 -

- ns

20 -

- ns

1/(128fS)

20

-

-

- ns

- ns

20 -

- ns

20 -

- ns

20 -

- ns

- 11 -

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet NJU8725.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NJU8721 | Class D HeadPhone Amplifier for Digital Audio | New Japan Radio |

| NJU8725 | CLASS D AMPLIFIER FOR DIGITAL AUDIO | New Japan Radio |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |