|

|

PDF MAX3681EAG Data sheet ( Hoja de datos )

| Número de pieza | MAX3681EAG | |

| Descripción | +3.3V / 622Mbps / SDH/SONET 1:4 Deserializer with LVDS Outputs | |

| Fabricantes | Maxim Integrated | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX3681EAG (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

19-1091; Rev 0; 6/96

EVAALVUAAILTAIOBNLEKIT

+3.3V, 622Mbps, SDH/SONET

1:4 Deserializer with LVDS Outputs

_________________General Description

The MAX3681 deserializer is ideal for converting

622Mbps serial data to 4-bit-wide, 155Mbps parallel

data in ATM and SDH/SONET applications. Operating

from a single +3.3V supply, this device accepts PECL

serial clock and data inputs, and delivers low-voltage

differential-signal (LVDS) clock and data outputs for

interfacing with high-speed digital circuitry. It also pro-

vides an LVDS synchronization input that enables data

realignment and reframing.

The MAX3681 is available in the extended-industrial

temperature range (-40°C to +85°C), in a 24-pin SSOP

package.

__________________________Applications

622Mbps SDH/SONET Transmission Systems

622Mbps ATM/SONET Access Nodes

Add/Drop Multiplexers

Digital Cross Connects

______________________________Features

o Single +3.3V Supply

o 622Mbps Serial to 155Mbps Parallel Conversion

o 265mW Power

o LVDS Data Outputs and Synchronization Inputs

o Synchronization Input for Data Realignment and

Reframing

o Differential 3.3V PECL Clock and Data Inputs

________________Ordering Information

PART

MAX3681EAG

TEMP. RANGE

-40°C to +85°C

PIN-PACKAGE

24 SSOP

Pin Configuration appears at end of data sheet.

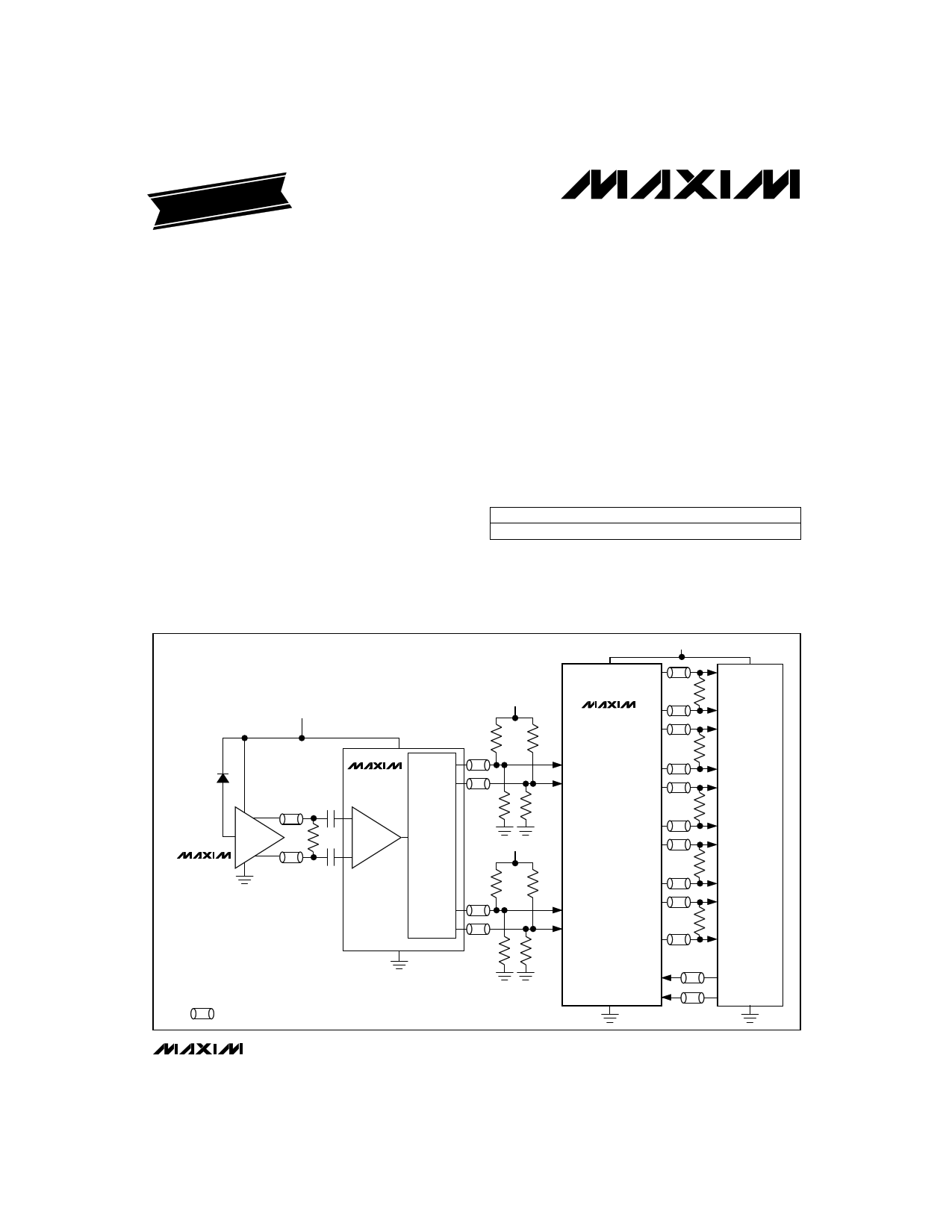

___________________________________________________________________Typical Operating Circuit

VCC = +3.3V

PHOTODIODE

VCC = +3.3V

MAX3675

PREAMP

MAX3664

100Ω LIMITING

AMP

DATA

AND

CLOCK

RECOVERY

VCC PD3+

VCC = +3.3V

130Ω

130Ω

MAX3681

SD+

SD-

100Ω*

PD3-

PD2+

100Ω*

PD2-

PD1+

82Ω 82Ω

100Ω*

PD1-

VCC = +3.3V

130Ω

130Ω

PD0+

100Ω*

PD0-

SCLK+

SCLK-

82Ω 82Ω

PCLK+

100Ω*

PCLK-

OVERHEAD

TERMINATION

*REQUIRED ONLY IF OVERHEAD CIRCUIT DOES NOT INCLUDE INTERNAL INPUT TERMINATION.

THIS SYMBOL REPRESENTS A TRANSMISSION LINE OF CHARACTERISTIC IMPEDANCE Z0 = 50Ω.

SYNC+

GND SYNC-

________________________________________________________________ Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

1 page

+3.3V, 622Mbps, SDH/SONET

1:4 Deserializer with LVDS Outputs

SCLK

SD D1-

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9 D10 D11

SYNC

PCLK

PD3 D4-

D0 D5

PD2 D3-

D1 D6

PD1 D2-

D2 D7

PD0 D1-

NOTE: SIGNALS SHOWN ARE DIFFERENTIAL. FOR EXAMPLE, SCLK = (SCLK+) - (SCLK-).

Figure 2. Functional Timing Diagram

SCLK

tSCLK = 1 / fSCLK

SD

PCLK

PD0–PD3

NOTE: SIGNALS SHOWN ARE DIFFERENTIAL. FOR EXAMPLE, SCLK = (SCLK+) - (SCLK-).

Figure 3. Timing Parameters

D3

tSU tH

tCLK-Q

D8

_______________________________________________________________________________________ 5

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet MAX3681EAG.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX3681EAG | +3.3V / 622Mbps / SDH/SONET 1:4 Deserializer with LVDS Outputs | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |