|

|

PDF MAX3676 Data sheet ( Hoja de datos )

| Número de pieza | MAX3676 | |

| Descripción | 622Mbps / 3.3V Clock-Recovery and Data-Retiming IC with Limiting Amplifier | |

| Fabricantes | Maxim Integrated | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX3676 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

19-1537; Rev 0; 7/99

622Mbps, 3.3V Clock-Recovery and

Data-Retiming IC with Limiting Amplifier

_____________________General Description ____________________________Features

The MAX3676 is a complete clock-recovery and data-

retiming IC incorporating a limiting amplifier. It is intend-

ed for 622Mbps SDH/SONET applications and operates

from a single +3.3V supply.

The MAX3676 is designed for both section-regenerator

and terminal-receiver applications in OC12/STM-4 trans-

mission systems. Its jitter performance exceeds all

SONET/SDH specifications.

The MAX3676 has two differential input amplifiers: one

accepts positive-referenced emitter-coupled logic

(PECL) levels, while the other accepts small-signal ana-

log levels. The analog inputs access the limiting amplifi-

er stage, which provides both a received-signal-strength

indicator (RSSI) and a programmable-threshold loss-of-

power (LOP) monitor. Selecting the PECL amplifier dis-

ables the limiting amplifier, conserving power. A

loss-of-lock (LOL) monitor is also incorporated as part of

the fully integrated phase-locked loop (PLL).

________________________Applications

SDH/SONET Receivers and Regenerators

SDH/SONET Access Nodes

Add/Drop Multiplexers

ATM Switches

o Single +3.3V or +5.0V Power Supply

o Exceeds ITU/Bellcore SDH/SONET Regenerator

Specifications

o Low Power: 237mW at +3.3V

o Selectable Data Inputs, Differential PECL or

Analog

o Received-Signal-Strength Indicator

o Loss-of-Power and Loss-of-Lock Monitors

o Differential PECL Clock and Data Outputs

o No External Reference Clock Required

_________________Ordering Information

PART

TEMP. RANGE PIN-PACKAGE

MAX3676EHJ

-40°C to +85°C 5mm 32 TQFP

MAX3676E/D

-40°C to +85°C Dice*

*Contact factory for availability. Dice are designed to operate

over a -40°C to +140°C junction temperature (Tj) range, but are

tested and guaranteed at Tj = +45°C.

Pin Configuration appears at end of data sheet.

Digital Cross-Connects

___________________________________________________ Typical Operating Circuit

100pF

PHOTO-

DIODE

+3.3V

+3.3V

2.2µF

0.01µF

0.1µF

INSEL PHADJ+ PHADJ- FIL+ FIL- LOL

VCC

FILT

DDI+

DDI-

MAX3664

INREF

OUT+

IN

OUT-

GND COMP

220pF

ZO = 50Ω

CIN

0.01µF

ADI+

100Ω

MAX3676

ZO = 50Ω

+3.3V

CIN

0.01µF

ADI-

VCC

CFILT OLC+ OLC- GND RSSI

INV

SDO+

SDO-

SCLKO+

SCLKO-

VTH LOP

CF

47nF

COLC

33nF

R2

R1

20k

CLOL

0.01µF

+3.3V

130Ω

130Ω

ZO = 50Ω

ZO = 50Ω

82Ω 82Ω

+3.3V

130Ω

ZO = 50Ω

ZO = 50Ω

82Ω

130Ω

82Ω

________________________________________________________________ Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800.

For small orders, phone 1-800-835-8769.

1 page

622Mbps, 3.3V Clock-Recovery and

Data-Retiming IC with Limiting Amplifier

Typical Operating Characteristics (continued)

(VCC = +3.3V, TA = +25°C, unless otherwise noted.)

LOSS-OF-POWER

HYSTERESIS vs. TEMPERATURE

5.0

223 -1 PATTERN

4.5 VCC = +3.3V OR +5.0V

4.0

3.5

3.0

2.5

2.0

-40 -20 0 20 40 60 80

AMBIENT TEMPERATURE (°C)

100

RECEIVED-SIGNAL-STRENGTH INDICATOR

vs. INPUT VOLTAGE

2.7

2.5

2.3 223 -1 PATTERN

2.1

1.9

1.7 1010 PATTERN

1.5

1.3

1.1

0.1

1.0 10 100

INPUT VOLTAGE (mVp-p)

1000

LOSS-OF-POWER

ASSERT AND RELEASE LEVEL

vs. DETECTOR THRESHOLD VOLTAGE

100

223 -1 PATTERN

LOP RELEASE

10

LOP ASSERT

1

1.2 1.3 1.4 1.5 1.6 1.7 1.8 1.9 2.0 2.1 2.2 2.3 2.4

DETECTOR THRESHOLD VOLTAGE, VTH (V)

RECEIVED-SIGNAL-STRENGTH INDICATOR

vs. INPUT VOLTAGE

2.7

223 -1 PATTERN

2.5 VCC = +3.3V OR +5.0V

2.3

2.1

1.9

1.7

1.5

1.3

1.1

0.1

1.0 10 100

INPUT VOLTAGE (mVp-p)

1000

SUPPLY CURRENT

vs. TEMPERATURE

100

90

VCC = +5.0V

80

70

60

50

VCC = +3.3V

40

30

-40 -20

0 20 40 60 80 100

TEMPERATURE (°C)

_______________________________________________________________________________________ 5

5 Page

622Mbps, 3.3V Clock-Recovery and

Data-Retiming IC with Limiting Amplifier

Reduced Power Consumption

Without the Limiting Amplifier

The limiting amplifier is biased independently from the

clock recovery circuitry. Grounding INSEL turns off the

limiting amplifier and selects the PECL DDI inputs.

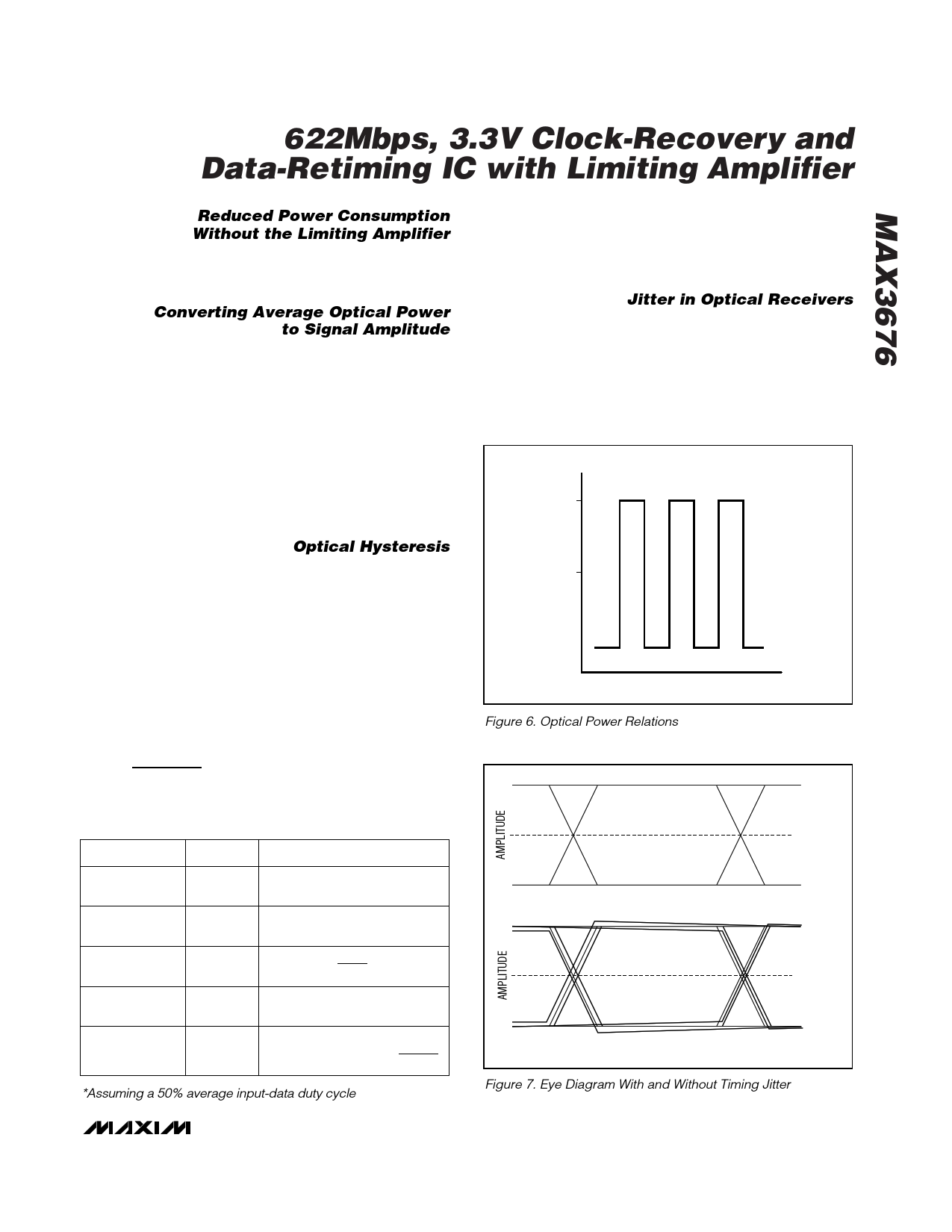

Converting Average Optical Power

to Signal Amplitude

Many of the MAX3676’s specifications relate to input-

signal amplitude. When working with fiber optic

receivers, the input is usually expressed in terms of

average optical power and extinction ratio. The rela-

tions given in Table 2 and Figure 6 are helpful for con-

verting optical power to input signal when designing

with the MAX3676.

In an optical receiver, the input voltage to the limiting

amplifier can be found by multiplying the relationship in

Table 2 by the photodiode responsivity and transim-

pedance amplifier gain.

Optical Hysteresis

Power and hysteresis are often expressed in decibels.

By definition, decibels are always 10log (power). At the

inputs to the MAX3676 limiting amplifier, the power is

VIN2/R. If a receiver’s optical input power (x) increases

by a factor of two, and the preamplifier is linear, then the

voltage at the input to the MAX3676 also increases by a

factor of two.

The optical power increase is:

10log(2x / x) = 10log(2) = +3dB

At the MAX3676, the voltage increase is:

( )10log 2VIN 2 / R = 10log(22) = 20log(2) = + 6dB

VIN2/ R

In an optical receiver, the decibel change at the

MAX3676 always equals 2x the optical decibel change.

The MAX3676’s typical voltage hysteresis is 3.0dB. This

provides an optical hysteresis of 1.5dB.

Jitter in Optical Receivers

Timing jitter, edge speeds, aberrations, optical disper-

sion, and attenuation all impact the performance of

high-speed clock recovery for SDH/SONET receivers

(Figure 7). These effects decrease the time available

for error-free data recovery by reducing the received

“eye opening” of nonreturn-to-zero (NRZ) transmitted

signals.

P1

PAVE

P0

Figure 6. Optical Power Relations

TIME

Table 2. Optical-Power Relations*

PARAMETER

Average

Power

Extinction

Ratio

Optical Power

of a “1”

Optical Power

of a “0”

Signal

Amplitude

SYMBOL

PAVG

re

P1

P0

PIN

RELATION

( )PAVG = P0 + P1 / 2

re = P1 / P0

P1 =

2PAVG

re

re +

1

( )P0 = 2PAVG / re +1

( )PIN = P1− P0 = 2PAVG

re − 1

re + 1

*Assuming a 50% average input-data duty cycle

EYE DIAGRAM WITH NO TIMING JITTER

MIDPOINT

TIME

MIDPOINT

EFFECTS OF TIMING JITTER ON EYE DIAGRAM

TIME

Figure 7. Eye Diagram With and Without Timing Jitter

______________________________________________________________________________________ 11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet MAX3676.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX3670 | Low-Jitter 155MHz/622MHz Clock Generator | Maxim Integrated |

| MAX3670EGJ | Low-Jitter 155MHz/622MHz Clock Generator | Maxim Integrated |

| MAX3671 | Low-Jitter Frequency Synthesizer | Maxim Integrated Products |

| MAX3672 | Low-Jitter 155MHz/622MHz Clock Generator | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |