|

|

PDF MAX3672 Data sheet ( Hoja de datos )

| Número de pieza | MAX3672 | |

| Descripción | Low-Jitter 155MHz/622MHz Clock Generator | |

| Fabricantes | Maxim Integrated | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX3672 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

19-2697; Rev 0; 12/02

Low-Jitter 155MHz/622MHz Clock Generator

General Description

The MAX3672 is a low-jitter 155MHz/622MHz reference

clock generator IC designed for system clock distribution

and frequency synchronization in OC-48 and OC-192

SONET/SDH and WDM transmission systems. The

MAX3672 integrates a phase/frequency detector, an

operational amplifier (op amp), prescaler dividers, and

input/output buffers. Using an external VCO, the

MAX3672 can be configured easily as a phase-lock loop

with bandwidth programmable from 30Hz to 10kHz.

The MAX3672 operates from a single +3.3V or +5.0V

supply and dissipates 150mW (typ) at 3.3V. The operat-

ing temperature range is -40°C to +85°C.

Applications

OC-12 to OC-192 SONET/WDM Transport

Systems

Clock Jitter Clean-Up and Frequency

Synchronization

Frequency Conversion

System Clock Distribution

Features

o Single +3.3V or +5.0V Supply

o Power Dissipation: 150mW at +3.3V Supply

o External VCO Center Frequencies (fVCO): 155MHz

to 700MHz

o Reference Clock Frequencies: fVCO, fVCO/2,

fVCO/4, fVCO/8, fVCO/32

o Main Clock Output Frequency: fVCO

o Optional Output Clock Frequencies: fVCO, fVCO/2,

fVCO/4, fVCO/8

o Low Intrinsic Jitter: <0.4psRMS

o Loss-of-Lock Indicator

o PECL Clock Output Interface

Ordering Information

PART

TEMP RANGE

PIN-PACKAGE

MAX3672E/D

-40°C to +85°C

Dice*

*Dice are designed to operate from -40° to +85°C, but are test-

ed and guaranteed at TA = +25° only.

Typical Application Circuit

+3.3V 142Ω

VCO

KVCO = 25kHz/V

155MHz

142Ω

155MHz

100Ω

+3.3V

REFCLK+

REFCLK-

VCOIN+

VCCD

VCOIN- MAX3672

0.01µF

332Ω

4700pF

4700pF

REPRESENTS A

CONTROLLED-IMPEDANCE

TRANSMISSION LINE.

500kΩ

500kΩ

VC

OPAMP-

OPAMP+

VFILTER

1000pF

POLAR

142Ω

MOUT+

MOUT-

142Ω

RSEL

VSEL

NSEL1

NSEL2

GSEL

N.C.

N.C.

GND 3.3V

SETUP FOR 10kHz LOOP

BANDWIDTH

MAX3892

16:1

SERIALIZER

________________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

1 page

Low-Jitter 155MHz/622MHz Clock Generator

(TA = +25°C, unless otherwise noted.)

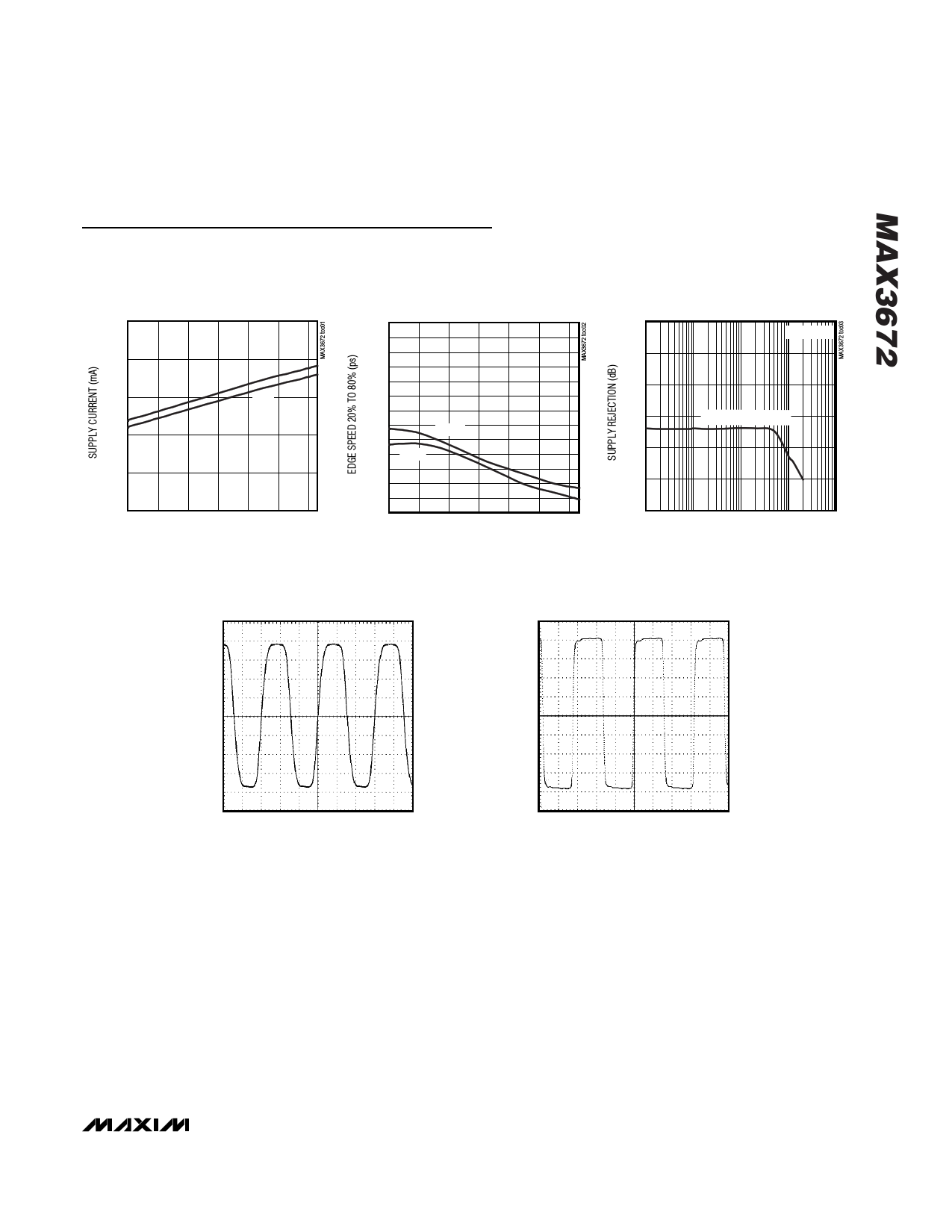

SUPPLY CURRENT

vs. TEMPERATURE

70

60

5.0V

50 3.3V

40

30

20

-40 -20

0 20 40 60

TEMPERATURE (°C)

80

Typical Operating Characteristics

270

260

250

240

230

220

210

200

190

180

170

160

150

140

-40

OUTPUT CLOCK EDGE SPEED

vs. TEMPERATURE

155.52

667

-20 0 20 40 60

TEMPERATURE (°C)

80

POWER-SUPPLY REJECTION

vs. FREQUENCY

0

BW = 1kHz

-10

-20

-30 LOOP FILTER OUTPUT

-40

-50

-60

1k

10k 100k 1M

FREQUENCY (Hz)

10M

667MHz CLOCK OUTPUT

MAX3672 toc04

155MHz CLOCK OUTPUT

MAX3672 toc05

200mV/div

200mV/div

500ps/div

2ns/div

_______________________________________________________________________________________ 5

5 Page

Low-Jitter 155MHz/622MHz Clock Generator

Bond Pad Coordinates

LOL Setup

The LOL output indicates if the PLL has locked onto the

PAD

PAD COORDINATES (µm)

XY

reference clock using an XOR gate and comparator. The

comparator threshold can be adjusted with THADJ, and

1 50.8

2 50.8

1557.3

1408.8

the XOR gate output can be filtered with a capacitor

between CTH and ground (Figure 3). When the voltage

at pin CTH exceeds the voltage at pin THADJ, then the

3 50.8

1179.3

LOL output goes low and indicates that the PLL is not

4 50.8

1028.1

locked. Note that excessive jitter on the reference clock

5 50.8

6 50.8

7 50.8

8 50.8

874.2

720.4

566.5

412.6

input at frequencies above the loop bandwidth may

degrade LOL functionality.

The user can set the amount of frequency or phase dif-

ference between VCO and reference clock at which

LOL indicates an out-of-lock condition. The frequency

9 50.8

258.7

difference is called the beat frequency. The CTH pin

10 266.8

11 420.7

50.8 can be connected to an external capacitor, which sets

50.8 the lowpass filter frequency to approximately

12 574.6

13 728.5

14 882.4

15 1036.2

16 1190.1

17 1344

18 1549.2

19 1792.2

20 1792.2

21 1792.2

22 1792.2

23 1792.2

24 1792.2

25 1792.2

26 1792.2

27 1792.2

50.8

50.8

50.8

50.8

50.8

50.8

50.8

256

409.9

563.8

717.7

871.6

1025.4

1179.3

1333.2

1530.3

fL

=

1

2πC TH 60kΩ

This lowpass filter frequency should be set about 10

times lower then the beat frequency to ensure that the

filtered signal at CTH does not drop below the THADJ

threshold voltage. Internal comparisons occur at the

pre-divider output frequency (see Table 1 for VCO and

reference clock setup). For example, assume the pre-

divider output frequency is 19.44MHz. For a 1ppm sen-

sitivity, the minimum beat frequency is 19Hz, and the

filter should be set to 1.9Hz. Set CTH to 1.36uF.

The voltage at THADJ will determine the level at which

the LOL output flags. THADJ is set to a default value of

0.6V which corresponds to a 45° phase difference. This

value can be overridden by applying the desired

threshold voltage to the THADJ input. The range of

THADJ is 0V (0°) to 2.4V (180°).

28 1792.2

1692.3

29 1565.4

1692.3

30 1411.5

1692.3

31 1257.6

1692.3

32 1103.7

1692.3

33 893.2

1692.3

34 685.3

1692.3

35 531.4

1692.3

36 377.5

1692.3

37 223.6

1692.3

______________________________________________________________________________________ 11

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet MAX3672.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX3670 | Low-Jitter 155MHz/622MHz Clock Generator | Maxim Integrated |

| MAX3670EGJ | Low-Jitter 155MHz/622MHz Clock Generator | Maxim Integrated |

| MAX3671 | Low-Jitter Frequency Synthesizer | Maxim Integrated Products |

| MAX3672 | Low-Jitter 155MHz/622MHz Clock Generator | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |