|

|

PDF SAA2501 Data sheet ( Hoja de datos )

| Número de pieza | SAA2501 | |

| Descripción | Digital Audio Broadcast DAB decoder | |

| Fabricantes | Philips | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de SAA2501 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

SAA2501

Digital Audio Broadcast (DAB)

decoder

Preliminary specification

File under Integrated Circuits, IC01

January 1995

Philips Semiconductors

1 page

Philips Semiconductors

Digital Audio Broadcast (DAB) decoder

Preliminary specification

SAA2501

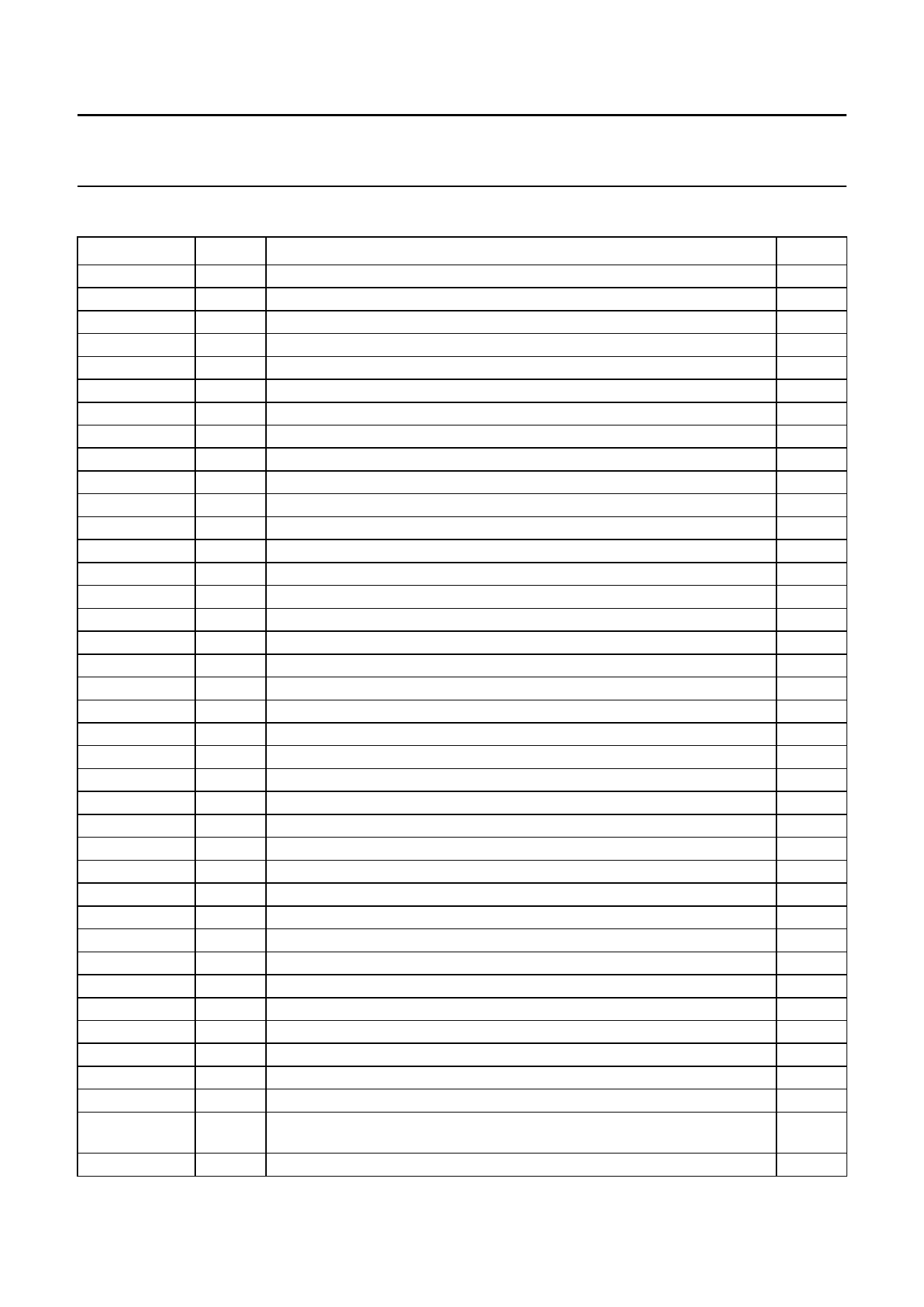

6 PINNING

SYMBOL

RESET

FSCLK

FSCLKIN

MCLK

VDD1

GND1

MCLKOUT

MCLKIN

X22OUT

X22IN

STOP

URDA

CDMWS

CDMEF

CDM

CDMCL

GND2

CDSCL

CDS

CDSEF

CDSWA

CDSSY

L3CLK

L3DATA

L3MODE

SD

FDEF

GND3

SCK

WS

FDAO

FDAI

FDFSY

VDD2

TC1

TC0

TDO

TRST

TCK

January 1995

PIN

DESCRIPTION

TYPE

1 master reset input

I

2 sample rate clock output; buffered signal

O

3 sample rate clock signal input (see Table 1)

I

4 master clock output; buffered signal

5 supply voltage 1

6 ground 1

O

−

−

7 master clock oscillator output

O

8 master clock oscillator input or signal input

I

9 22.579 MHz clock oscillator output

O

10 22.579 MHz clock oscillator input or signal input

I

11 stop decoding input

I

12 unreliable data input; interrupt decoding

I

13 coded data (master input) word select output

O

14 coded data (master input) error flag input

I

15 ISO/MPEG coded data (master input)

I

16 coded data (master input) bit clock output

O

17 ground 2

−

18 coded data (slave input) bit clock

I

19 ISO/MPEG or EU147 (see Table 8) coded data (slave input)

I

20 coded data (slave input) error flag

I

21 coded data (slave input) burst window signal

I

22 coded data (slave input) frame sync

I

23 L3 interface bit clock input

I

24 L3 interface serial data input/output

I/O

25 L3 interface address/data select input

26 baseband audio I2S data output

I

O

27 filter data error flag output

O

28 ground 3

29 baseband audio data I2S clock output

30 baseband audio data I2S word select output

−

O

O

31 filter data output

O

32 filter data input

I

33 filter data output frame sync

O

34 supply voltage 2

35 do not connect; factory test control 1 input, with integrated pull-down resistor

−

I

36 do not connect; factory test control 0 input, with integrated pull-down resistor

I

37 boundary scan test data output

O

38 boundary scan test reset input; this pin should be connected to ground for

normal operation

I

39 boundary scan test clock input

I

5

5 Page

Philips Semiconductors

Digital Audio Broadcast (DAB) decoder

Preliminary specification

SAA2501

Table 3 Muted frames

CRC

MINIMUM NUMBER OF MUTED FRAMES

DURING SYNCHRONIZATION

FREE FORMAT BIT NON-FREE-FORMAT

RATE

BIT RATE

No CRC

2

1

CRC

1

0

Table 4 Defaults master input bit rate

FSCLKM

0

1

Note

1. X = don’t care.

FSCLK384

0

0

1

0

1

0

1

7.11 Master input bit rate selection

As explained in Section 7.10, the SAA2501 can be used to

alternate between two applications: one with the slave

input, and one with the master input. When using the

master input, the SAA2501 should fetch data with the

effective bit rate, but cannot know what the bit rate of the

input data is until it has established synchronization. To

overcome this paradox, the input requesting is done at the

last selected bit rate.

After a device reset, the master input bit rate selection

defaults to the value indicated in Table 4.

FSCLKIN

X(1)

256 × 32 kHz

384 × 32 kHz

256 × 44.1 kHz

384 × 44.1 kHz

256 × 48 kHz

384 × 48 kHz

DEFAULT MASTER INPUT

BIT RATE (kbits/s)

384

278.64

384

417.96

When FSCLKM = 0, the default master input bit rate is

384 kbits/s. When FSCLKM = 1, the SAA2501 uses signal

FSCLKIN to derive the selected bit rate, but it has no

indication concerning the sample rate corresponding to

FSCLKIN. Therefore, a bit rate of 384 kbits/s is selected at

an assumed sample rate of 44.1 kHz; with other sample

rates, the bit rate changes proportionally.

The consequence is that while the SAA2501 synchronises

(e.g. after a device reset), the application must at least be

able to supply at the given default bit rate the required

number of frames plus one additional frame (because of

the random decoding start point in the input bitstream).

Buffers in the application must thus be chosen sufficiently

large to prevent under or overflows.

The speed with which input data is requested by the

master input is changed by the SAA2501 in each of the

following cases:

1. When input synchronization is established after

checking a number of frames and the bit rate index of

the newly decoded bitstream indicates a different bit

rate than that currently selected. In this event, the bit

rate is adapted to the newly decoded index.

2. When the active input interface is changed from the

master to the slave input, or the signal STOP is

activated; in these events input requesting stops.

3. When the active input interface is changed from the

slave to the master input, or the signal STOP is

deactivated; the bit rate is set to the last selected

master input bit rate (the last selected master input bit

rate is memorised while using the slave input).

In all other events (e.g. when the SAA2501 goes and stays

out of synchronization), the data requesting speed of the

master input is maintained.

7.12 Sample rate selection

When using the slave input, or when using the master

input with FSCLKM = 1, the application must know the

sample rate: FSCLKIN must be applied, which has a

frequency which is a multiple of the sample rate; the

(sample rate dependent) I2S timing signals SCK and WS

are generated from FSCLKIN. These configurations will

normally be used in applications with a fixed sample rate.

Should the sample rate change, then the SAA2501 must

be reset.

January 1995

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SAA2501.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SAA2500 | MPEG Audio Source Decoder | Philips |

| SAA2500H | MPEG Audio Source Decoder | Philips |

| SAA2501 | Digital Audio Broadcast DAB decoder | Philips |

| SAA2501H | Digital Audio Broadcast DAB decoder | Philips |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |