|

|

PDF OP176 Data sheet ( Hoja de datos )

| Número de pieza | OP176 | |

| Descripción | Bipolar/JFET / Audio Operational Amplifier | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de OP176 (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

a

Bipolar/JFET,

Audio Operational Amplifier

OP176*

FEATURES

Low Noise: 6 nV/√Hz

High Slew Rate: 25 V/µs

Wide Bandwidth: 10 MHz

Low Supply Current: 2.5 mA

Low Offset Voltage: 1 mV

Unity Gain Stable

SO-8 Package

APPLICATIONS

Line Driver

Active Filters

Fast Amplifiers

Integrators

GENERAL DESCRIPTION

The OP176 is a low noise, high output drive op amp that

features the Butler Amplifier front-end. This new front-end

design combines both bipolar and JFET transistors to attain

amplifiers with the accuracy and low noise performance of

bipolar transistors, and the speed and sound quality of JFETs.

Total Harmonic Distortion plus Noise equals previous audio

amplifiers, but at much lower supply currents.

Improved dc performance is also provided with bias and offset

currents greatly reduced over purely bipolar designs. Input

offset voltage is guaranteed at 1 mV and is typically less than

*Protected by U.S. Patent No. 5101126.

PIN CONNECTIONS

8-Lead Narrow-Body SO

(S Suffix)

8-Lead Epoxy DIP

(P Suffix)

NULL 1

–IN 2

+IN 3

V– 4

OP176

8 NC

7 V+

6 OUT

5 NULL

NULL 1

–IN 2

+IN 3

V– 4

OP176

OP-482

8 NC

7 V+

6 OUT

5 NULL

200 µV. This allows the OP176 to be used in many dc coupled

or summing applications without the need for special selections

or the added noise of additional offset adjustment circuitry.

The output is capable of driving 600 Ω loads to 10 V rms while

maintaining low distortion. THD + Noise at 3 V rms is a low

0.0006%.

The OP176 is specified over the extended industrial (–40°C to

+85°C) temperature range. OP176s are available in both plastic

DIP and SO-8 packages. SO-8 packages are available in 2500

piece reels. Many audio amplifiers are not offered in SO-8

surface mount packages for a variety of reasons, however, the

OP176 was designed so that it would offer full performance in

surface mount packaging.

7

RB2

QB4

RB4

RB3

QB5

RB5

QB6

RB7

RB6

QB7

CB1

QB3

J1

Q1

2

Z2

J2

Q2

3

JB1

QB2

RB1

Q3

Q5

QB1

Z1

R1L R1P1

QB8

CC1

R1A R1P2

R1S R2S

Q4 QS3

R2P1 R2L

R2P2 R2A

CCB

Q6

CF

R3

QB9

R4

Q9

CC2

Q8

Q10

RS1

Q11

QS1

R5

RS2

QS2

6

Q7

15

4

REV. 0

Simplified Schematic

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A.

Tel: 617/329-4700

Fax: 617/326-8703

1 page

80

70

SINK

60

±VS = ±15V

50 SOURCE

40

30

20

10

0

–50

–25

0 25 50

TEMPERATURE – °C

75 100

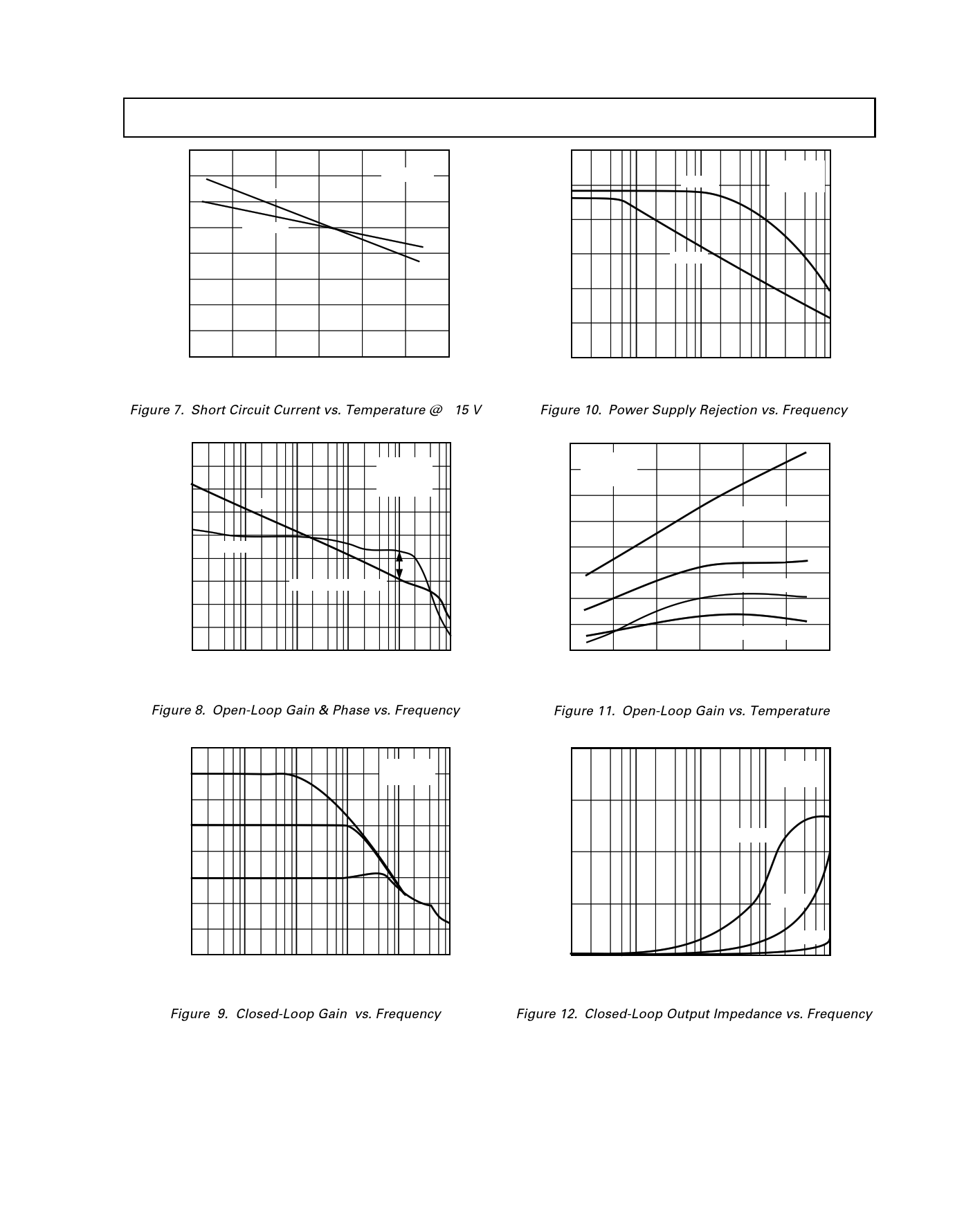

Figure 7. Short Circuit Current vs. Temperature @ ±15 V

120

100

80

60

40

20

0

–20

–40

–60

1k

GAIN

TA = +25°C

VS = ±15V

RL = >600Ω

PHASE

PHASE MARGIN = 60°

90

135

180

225

10k 100k

1M

10M

100M

FREQUENCY – Hz

Figure 8. Open-Loop Gain & Phase vs. Frequency

50

40

30

20

10

0

–10

–20

–30

1k

TA = +25°C

VS = ±15V

10k 100k

1M

FREQUENCY – Hz

10M

100M

Figure 9. Closed-Loop Gain vs. Frequency

OP176

120

TA = +25°C

100

+PSRR

±VS = ±15V

80

60 –PSRR

40

20

0

100

1k 10k 100k

FREQUENCY – Hz

1M

Figure 10. Power Supply Rejection vs. Frequency

2000

1750

1500

±VS = ±15V

±VO = ±10V

1250

1000

750

500

250

0

–50

–25

Ω–GAIN, RL = 2kΩ

+GAIN, RL = 2kΩ

–GAIN, RL = 600Ω

+GAIN, RL = 600Ω

0 25 50

TEMPERATURE – °C

75

100

Figure 11. Open-Loop Gain vs. Temperature

40

TA = +25°C

VS = ±15V

30

AV = +100

20

10 AV = +10

0

100

AV = +1

1k 10k 100k

FREQUENCY – Hz

1M

Figure 12. Closed-Loop Output Impedance vs. Frequency

REV. 0

–5–

5 Page

OP176

Attention to Source Impedances Minimizes Distortion

Since the OP176 is a very low distortion amplifier, careful

attention should be given to source impedances seen by both

inputs. As with many FET-type amplifiers, the p-channel

JFETs in the OP176’s input stage exhibit a gate-to-source

capacitance that varies with the applied input voltage. In an

inverting configuration, the inverting input is held at a virtual

ground and, as such, does not vary with input voltage. Thus,

since the gate-to-source voltage is constant, there is no distor-

tion due to input capacitance modulation. In noninverting

applications, however, the gate-to-source voltage is not

constant. The resulting capacitance modulation can cause

distortion above 1 kHz if the input impedance is > 2 kΩ and

unbalanced.

Figure 36 shows some guidelines for maximizing the distortion

performance of the OP176 in noninverting applications. The

best way to prevent unwanted distortion is to ensure that the

parallel combination of the feedback and gain setting resistors

(RF and RG) is less than 2 kΩ. Keeping the values of these

resistors small has the added benefits of reducing the thermal

noise of the circuit and dc offset errors. If the parallel combina-

tion of RF and RG is larger than 2 kΩ, then an additional

resistor, RS, should be used in series with the noninverting

RG RF

RS* OP176

VOUT

VIN

* RS = RG//RF IF RG//RF > 2kΩ

FOR MINIMUM DISTORTION

Figure 36. Balanced Input Impedance to Mininize

Distortion in Noninverting Amplifier Circuits

input. The value of RS is determined by the parallel combina-

tion of RF and RG to maintain the low distortion performance of

the OP176. For a more generalized treatment on circuit

impedances and their effects on circuit distortion, please review

the section on Active Filters at the end of the Applications

section.

Driving Capacitive Loads

As with any high speed amplifier, care must be taken when

driving capacitive loads. The graph in Figure 14 shows the

OP176’s overshoot versus capacitive load. The test circuit is a

standard noninverting voltage follower; it is this configuration

that places the most demand on an amplifier’s stability. For

capacitive loads greater than 400 pF, overshoot exceeds 40%

and is roughly equivalent to a 45° phase margin. If the applica-

tion requires the OP176 to drive loads larger than 400 pF, then

external compensation should be used.

Figure 37 shows a simple circuit which uses an in-the-loop

compensation technique that allows the OP176 to drive any

capacitive load. The equations in the figure allow optimization

of the output resistor, RX, and the feedback capacitor, CF, for

optimal circuit stability. One important note is that the circuit

bandwidth is reduced by the feedback capacitor, CF, and is

given by:

BW = 1

2 π R F CF

RG

VIN

RF

CF

OP176

RX

VOUT

CL

RX = RO RG WHERE RO = OPEN-LOOP OUTPUT RESISTANCE

RF

[ ]( )I

CF =

I+

| ACL|

( )RF + RG

RF

CL RO

Figure 37. In-the-Loop Compensation Technique for

Driving Capacitive Loads

APPLICATIONS USING THE OP176

A High Speed, Low Noise Differential Line Driver

The circuit of Figure 38 is a unique line driver widely used in

many applications. With ± 18 V supplies, this line driver can

deliver a differential signal of 30 V p-p into a 2.5 kΩ load. The

high slew rate and wide bandwidth of the OP176 combine to

yield a full power bandwidth of 130 kHz while the low noise

front end produces a referred-to-input noise voltage spectral

density of 15 nV/√Hz. The circuit is capable of driving lower

impedance loads as well. For example, with a reduced output

level of 5 V rms (14 V p-p), the circuit exhibits a full-power

bandwidth of 190 kHz while driving a differential load of 249 Ω!

The design is a transformerless, balanced transmission system

where output common-mode rejection of noise is of paramount

importance. Like the transformer-based design, either output

can be shorted to ground for unbalanced line driver applications

without changing the circuit gain of 1. Other circuit gains can

be set according to the equation in the diagram. This allows the

design to be easily set for noninverting, inverting, or differential

operation.

R1

2kΩ

VIN 3

6

2 A1

R2

2kΩ

R3

2kΩ

2

3 A2

6

R7

2kΩ

R4

2kΩ

R9

50Ω

R5

2kΩ R6

2kΩ

2

3 A3

6

R8

2kΩ

R10

50Ω

VO1

R11

1kΩ

P1

10kΩ

VO2 – VO1 = VIN

R12

1kΩ

VO2

A1, A2, A3 = OP176

GAIN = R3

R1

SET R2, R4, R5 = R1 AND R6, R7, R8 = R3

Figure 38. A High Speed, Low Noise Differential Line

Driver

REV. 0

–11–

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet OP176.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| OP176 | Bipolar/JFET / Audio Operational Amplifier | Analog Devices |

| OP177 | Ultraprecision Operational Amplifier | Analog Devices |

| OP179 | Rail-to-Rail High Output Current Operational Amplifiers | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |