|

|

PDF MX98L715BEC Data sheet ( Hoja de datos )

| Número de pieza | MX98L715BEC | |

| Descripción | 3.3V SINGLE CHIP FAST ETHERNET NIC CONTROLLER | |

| Fabricantes | Macronix International | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MX98L715BEC (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

PRELIMINARY

MX98L715BEC

1. FEATURES10/100M

3.3V SINGLE CHIP FAST ETHERNET NIC CONTROLLER

Ethernet Interface

• A single chip solution integrates 100/10 Base-T fast

Ethernet MAC, PHY and PMD

• Fully comply to IEEE 802.3u specification

• Operates over 100 meters of STP and cat 5 UTP cable

• Support full and half duplex operations in both 100

Base-TX and 10 Base-T mode

• Supports IEEE802.3x Frame Based Flow Control

scheme in full duplex mode.

• Supports transmission and reception of IEEE802.1Q

tagged frames.

• Supports QoS with prioritized traffic.

• Supports network and communication device class

OnNow requirements for Microsoft's PC99 specifica-

tions, including 3 wake up events :

- Link Change (link-on)

- Wake Up Frames

- Magic Packet

• 100/10 Base-T NWAY auto-negotiation function

• Support up to 5 LEDs for various network activities

• Supports early interrupt on both transmit and receive

operations.

• Support a variety of flexible address filtering modes

with 16 CAM address and 64 bits hash table

Home PNA interface

• Support 7-wire general purpose serial interface to link

with 1M8 PHY for home networking

PCI/MiniPCI interface

• Fully comply to PCI spec. 2.2 and Mini PCI spec. 0.73

up to 33MHz

• Fully comply to Advanced Configuration and Power

Interface (ACPI) Rev 1.1

• Fully comply to PCI Bus Power Management Interface

spec. Rev 1.1

• Bus master architecture with linked host buffers deliv-

ers the most optimized performance

• 32-bit bus master DMA channel provides ultra low

CPU utilization suitable for server and windows appli-

cations.

• Proprietary Adaptive Network Throughput Control

(ANTC) technology to optimize data integrity and

throughput

Other features

• Large on-chip FIFOs for both transmit and receive

operations without external local memory

• Support up to 128K bytes boot ROM/Flash interface

• MicroWire interface to EEPROM for customer's IDs

and configuration data

• Single 3.3V power supply, CMOS technology, 128-pin

PQFP package

( Magic Packet Technology is a trademark of Advanced Micro De-

vice Corp. )

2. GENERAL DESCRIPTIONS

The MX98L715BEC controller is an IEEE802.3u com-

pliant single chip 32-bit full duplex, 10/100Mbps highly

integrated Fast Ethernet combo solution, designed to

address high performance local area networking (LAN)

system application requirements.

MX98L715BEC's PCI bus master architecture delivers

the optimized performance for future high speed and pow-

erful processor technologies. In other words, the

MX98L715BEC not only keeps CPU utilization low while

maximizing data throughput, but it also optimizes the

PCI bandwidth providing the highest PCI bandwidth uti-

lization. To further reduce maintenance costs the

MX98L715BEC uses drivers that are backward compat-

ible with the original MXIC MX98715 series controllers.

The MX98L715BEC contains a PCI local bus glueless

interface, a Direct Memory Access (DMA) buffer man-

agement unit, an IEEE802.3u-compliant Media Access

Controller (MAC), large Transmit and Receive FIFOs, and

an on-chip 10 Base-T and 100 Base-TX transceiver sim-

plifying system design and improving high speed signal

quality. Full-duplex operation are supported in both 10

Base-T and 100 Base-TX modes that increases the

controller's operating bandwidth up to 200Mbps.

Equipped with intelligent IEEE802.3u-compliant auto-ne-

gotiation, the MX98L715BEC-based adapter allows a

single RJ-45 connector to link with the other IEEE802.3u-

compliant device without re-configuration.

P/N:PM0695

REV. 0.3, MAR. 30, 2001

1

1 page

MX98L715BEC

Pin Name Type Pin No

PAR T/S 24

STOPB S/T/S 20

REQB

GNTB

T/S 115

I 114

EECS O 59

BPA1

O 61

(EEDI)

BPA0

(EECK)

O

60

BPA[12:0] O

BPA13

(LED4)

BPA14

( LED0)

BPA15

( LED1)

BPA16

( LED2)

BPD0

(EEDO)

O

O

O

O

T/S

74-71,

68-60

77

78

79

80

58

BPD[7:0]

FWEB

( HLINKB)

FCSB

( VAUX)

FOEB

( LED3 )

RTX

PMEB

T/S

T/S

T/S

O

O

O/D

51-58

69

70

81

102

110

128 Pin Function and Driver

PCI bus parity bit: shared PCI bus even parity bit for 32 bits AD bus and CBE

bus.

PCI Target requested transfer stop signal: as bus master, assertion of STOPB

cause MX98L715BEC either to retry, disconnect, or abort.

PCI bus request signal: to initiate a bus master cycle request

PCI bus grant acknowledge signal: host asserts to inform MX98L715BEC

that access to the bus is granted

EEPROM Chip Select pin.

Boot PROM address bit 1(EECS=0): together with BPA[15:0] to access

external boot PROM up to 256KB.

EEPROM data in(EECS=1): EEPROM serial data input pin.

Boot PROM address bit 0(EECS=0): together with BPA[15:0] to access

external boot PROM up to 256KB.

EEPROM clock(EECS=1): EEPROM clock input pin

Boot PROM address line.

Boot PROM address line 13 ( LED4 )

Boot PROM address line 14 (LED0)

Boot PROM address line 15 ( LED1)

Boot PROM address line 16 ( LED2)

Boot PROM data line 0(EECS=0): boot PROM or flash data line 0.

EEPROM data out(EECS=1): EEPROM serial data outpin(during reset

initialization).

Boot PROM data lines: boot PROM or flash data lines 7-0.

Flash Write Enable Output ( or Home PNA Link active low input )

Boot PROM Chip Select Output or Auxiliary Vdd input with 10k external

resistor pull-up. (Internal pull-down)

Boot PROM Output Enable ( LED3 )

Connecting an external resistor to ground, Resistor value=1K ohms

Power Management Event Status Output

P/N:PM0695

REV. 0.3, MAR. 30, 2001

5

5 Page

MX98L715BEC

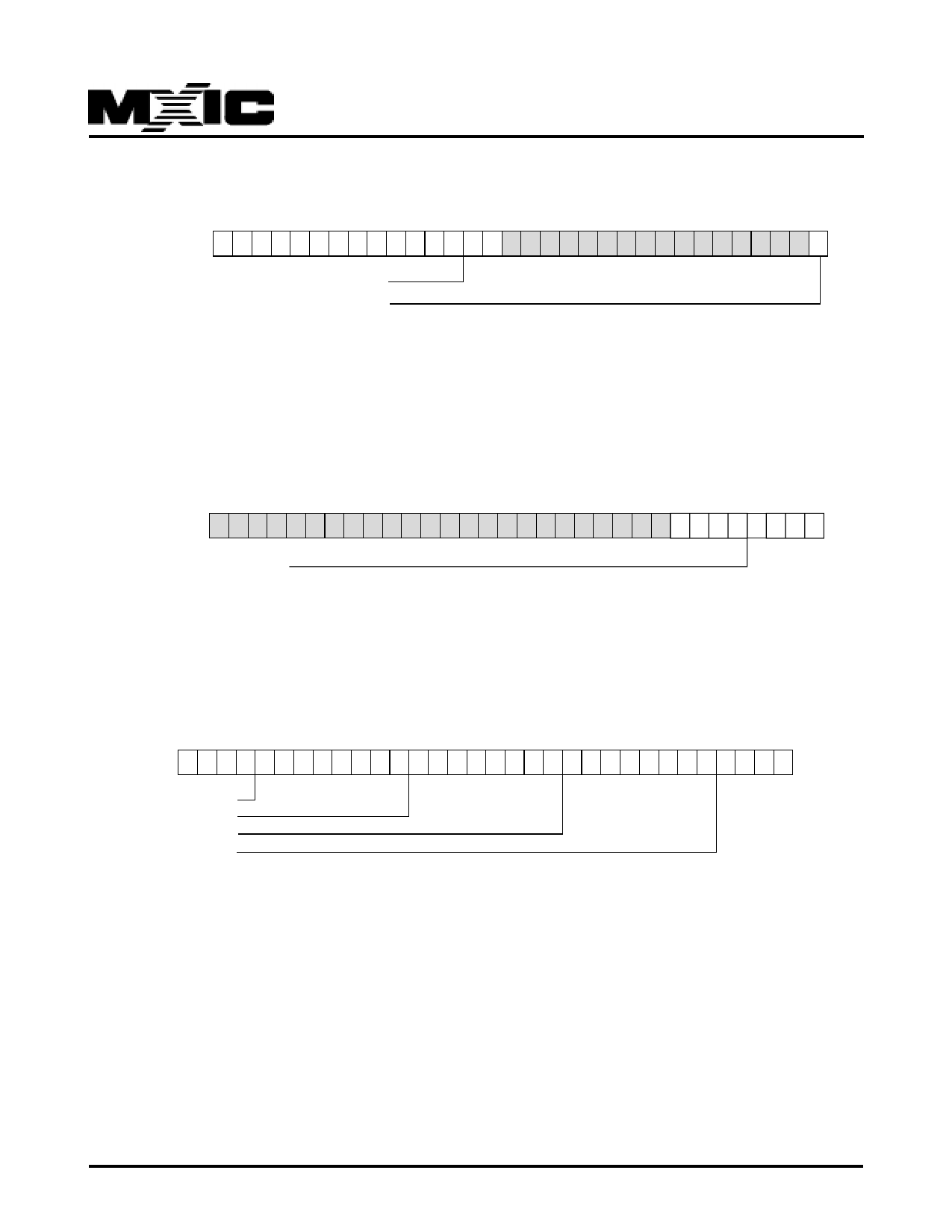

5.1.8 PCI BASE EXPANSION ROM ADDRESS REGISTER ( PBER ) ( Offset 33h-30h )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Expansion ROM Base Address (upper 21 bit)

Address Decode Enable

bit 0 : Address Decode Enable, decoding will be enabled if only both enable bit in PFCS<1> and this expansion ROM

register are 1.

bit 16 - 1 : not use

bit 31 - 17 : Defines the upper 21 bits of expansion ROM base address.

5.1.9 PCI CAPABILITY POINTER REGISTER ( PFCP ) ( Offset 37h-34h )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Capability Pointer (Set to 44h)

bit 7- 0 : Capability pointer (Cap_Ptr) is set to 44h.

bit 31- 8 : reserved

5.1.10 INTERRUPT REGISTER ( PFIT ) ( Offset 3Fh-3Ch )

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0111 000 000 01 00 0

Max_Lat

Min-Gnt

Interrupt Pin

Interrupt Line

bit 7 - 0 : Interrupt Line, system BIOS will writes the routing information into this field, driver can use this information

to determine priority and interrupt vector.

bit 15 - 8 : Interrupt Pin, fixed to 01h which use INTA#.

bit 31 - 24 : Max_Lat which is a maximum period for a access to PCI bus.

bit 23 - 16 : Min_Gnt which is the maximum period that MX98L715BEC needs to finish a burst PCI cycle.

P/N:PM0695

REV. 0.3, MAR. 30, 2001

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet MX98L715BEC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MX98L715BEC | 3.3V SINGLE CHIP FAST ETHERNET NIC CONTROLLER | Macronix International |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |