|

|

PDF M48Z18 Data sheet ( Hoja de datos )

| Número de pieza | M48Z18 | |

| Descripción | 64 Kbit (8 Kb x 8) ZEROPOWER SRAM | |

| Fabricantes | ST Microelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de M48Z18 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

M48Z08

M48Z18

5 V, 64 Kbit (8 Kb x 8) ZEROPOWER® SRAM

Features

■ Integrated, ultra low power SRAM and power-

fail control circuit

■ Unlimited WRITE cycles

■ READ cycle time equals WRITE cycle time

■ Automatic power-fail chip deselect and WRITE

protection

■ WRITE protect voltages

(VPFD = power-fail deselect voltage):

– M48Z08: VCC = 4.75 to 5.5 V;

4.5 V ≤ VPFD ≤ 4.75 V

– M48Z18: VCC = 4.5 to 5.5 V;

4.2 V ≤ VPFD ≤ 4.5 V

■ Self-contained battery in the CAPHAT™ DIP

package

■ Pin and function compatible with JEDEC

standard 8 K x 8 SRAMs

■ RoHS compliant

– Lead-free second level interconnect

28

1

PCDIP28

Battery CAPHAT™

June 2011

Doc ID 2424 Rev 8

1/20

www.st.com

1

1 page

M48Z08, M48Z18

1 Description

Description

The M48Z08/18 ZEROPOWER® RAM is an 8 K x 8 non-volatile static RAM which is pin and

function compatible with the DS1225.

The monolithic chip provides a highly integrated battery-backed memory solution.

The M48Z08/18 is a non-volatile pin and function equivalent to any JEDEC standard 8 K x 8

SRAM. It also easily fits into many ROM, EPROM, and EEPROM sockets, providing the

non-volatility of PROMs without any requirement for special write timing or limitations on the

number of writes that can be performed.

The 28-pin, 600 mil DIP CAPHAT™ houses the M48Z08/18 silicon with a long-life lithium

button cell in a single package.

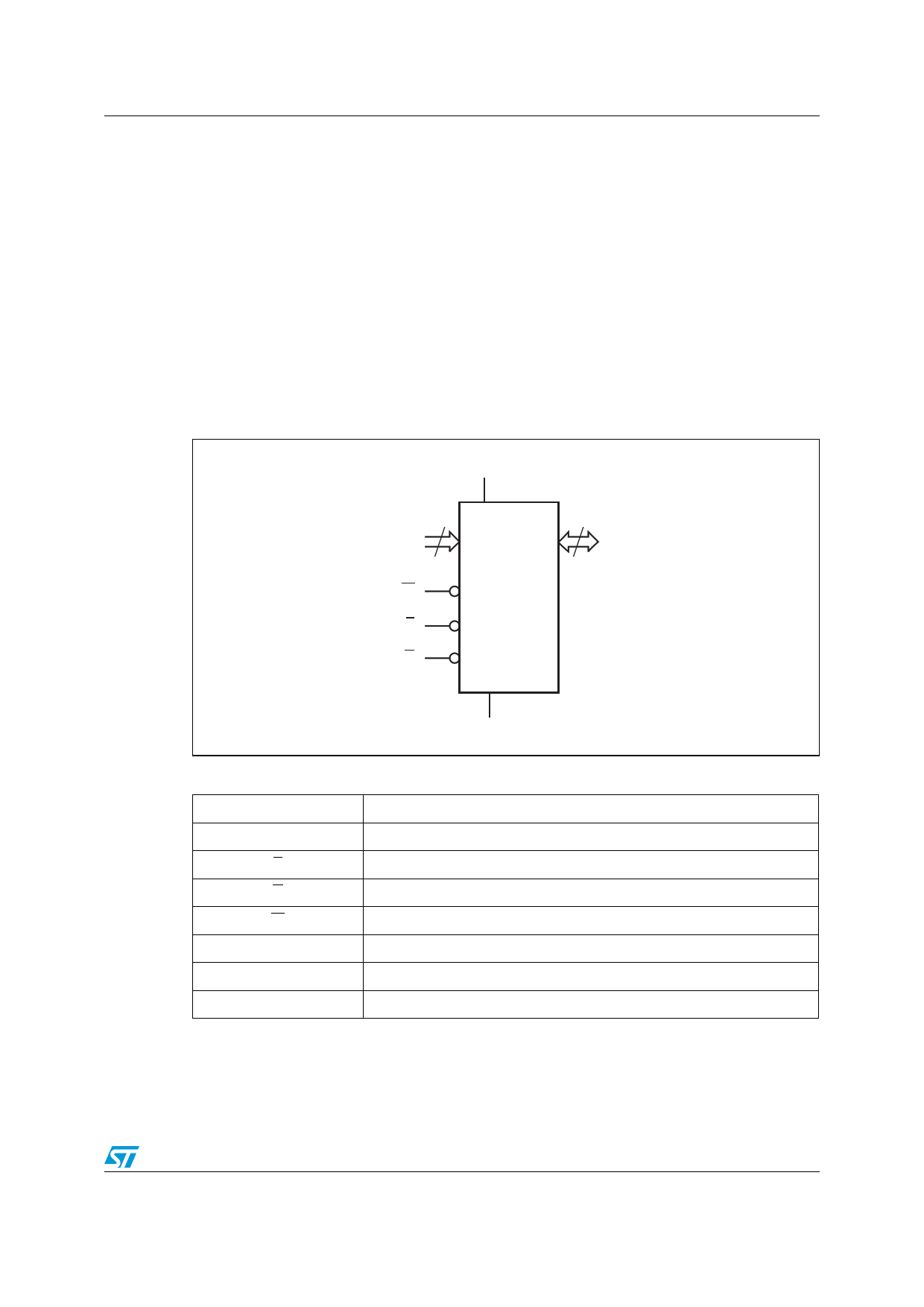

Figure 1. Logic diagram

VCC

13

A0-A12

W

E

G

M48Z08

M48Z18

8

DQ0-DQ7

VSS

Table 1. Signal names

A0-A12

Address inputs

DQ0-DQ7

Data inputs / outputs

E Chip enable

G Output enable

W WRITE enable

VCC Supply voltage

VSS Ground

NC Not connected internally

AI01022

Doc ID 2424 Rev 8

5/20

5 Page

M48Z08, M48Z18

Operation modes

2.4 VCC noise and negative going transients

ICC transients, including those produced by output switching, can produce voltage

fluctuations, resulting in spikes on the VCC bus. These transients can be reduced if

capacitors are used to store energy which stabilizes the VCC bus. The energy stored in the

bypass capacitors will be released as low going spikes are generated or energy will be

absorbed when overshoots occur. A ceramic bypass capacitor value of 0.1 µF (as shown in

Figure 7) is recommended in order to provide the needed filtering.

In addition to transients that are caused by normal SRAM operation, power cycling can

generate negative voltage spikes on VCC that drive it to values below VSS by as much as

one volt. These negative spikes can cause data corruption in the SRAM while in battery

backup mode. To protect from these voltage spikes, STMicroelectronics recommends

connecting a Schottky diode from VCC to VSS (cathode connected to VCC, anode to VSS).

Schottky diode 1N5817 is recommended for through hole and MBRS120T3 is

recommended for surface mount.

Figure 7. Supply voltage protection

VCC

VCC

0.1µF

DEVICE

VSS

AI02169

Doc ID 2424 Rev 8

11/20

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet M48Z18.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M48Z12 | 16 Kbit (2 Kb x 8) ZEROPOWER SRAM | ST Microelectronics |

| M48Z128 | 1 Mbit (128 Kbit x 8) ZEROPOWER SRAM | ST Microelectronics |

| M48Z128V | 5.0V OR 3.3V / 1 Mbit (128 Kbit x 8) ZEROPOWER SRAM | ST Microelectronics |

| M48Z128Y | 1 Mbit (128 Kbit x 8) ZEROPOWER SRAM | ST Microelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |