|

|

PDF IDT49C465 Data sheet ( Hoja de datos )

| Número de pieza | IDT49C465 | |

| Descripción | 32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT | |

| Fabricantes | Integrated Device | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT49C465 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Integrated Device Technology, Inc.

32-BIT FLOW-THRU

ERROR DETECTION

AND CORRECTION UNIT

IDT49C465

IDT49C465A

FEATURES

• 32-bit wide Flow-thruEDC™ unit, cascadable to 64 bits

• Single-chip 64-bit Generate Mode

• Separate system and memory buses

• On-chip pipeline latch with external control

• Supports bidirectional and common I/O memories

• Corrects all single-bit errors

• Detects all double-bit errors, some multiple-bit errors

• Error Detection Time — 12ns

• Error Correction Time — 14ns

• On chip diagnostic registers.

• Parity generation and checking on system data bus

• Low power CMOS — 100mA typical at 20MHZ

• 144-pin PGA and PQFP packages

• Military product compliant to MIL-STD 883, Class B

DESCRIPTION

The IDT49C465/A is a 32-bit, two-data bus, Flow-thruEDC

unit. The chip provides single-error correction and two and

three bit error detection of both hard and soft memory errors.

It can be expanded to 64-bit widths by cascading 2 units,

without the need for additional external logic. The Flow-

thruEDC has been optimized for speed and simplicity of

control.

The EDC unit has been designed to be used in either of two

configurations in an error correcting memory system. The

bidirectional configuration is most appropriate for systems

using bidirectional memory buses. A second system

configuration utilizes external octal buffers, and is well suited

for systems using memory with separate I/O buses.

The IDT49C465/A supports partial word writes, pipelining

and error diagnostics. It also provides parity protection for

data on the system side.

SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM

MD0–31

MLE

CBI0–7

PCBI0–7

SD0–31

SLE

PLE

MD

Latch

Memory

Checkbit

Generator

Checkbit

Latch

Mux

CONTROL

SD

Latch

Byte

Mux

CONTROL

Correct

Logic

Detect

Logic

ERR

MERR

CONTROL

System

Checkbit

Generator

Mux

CONTROL

CBO0–7

2552 drw 01

The IDT logo is a registered trademark and Flow-thruEDC is a trademarkof Integrated Device Technology Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

©1995 Integrated Device Technology, Inc.

11.7

AUGUST 1995

DSC-9028/7

1

1 page

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

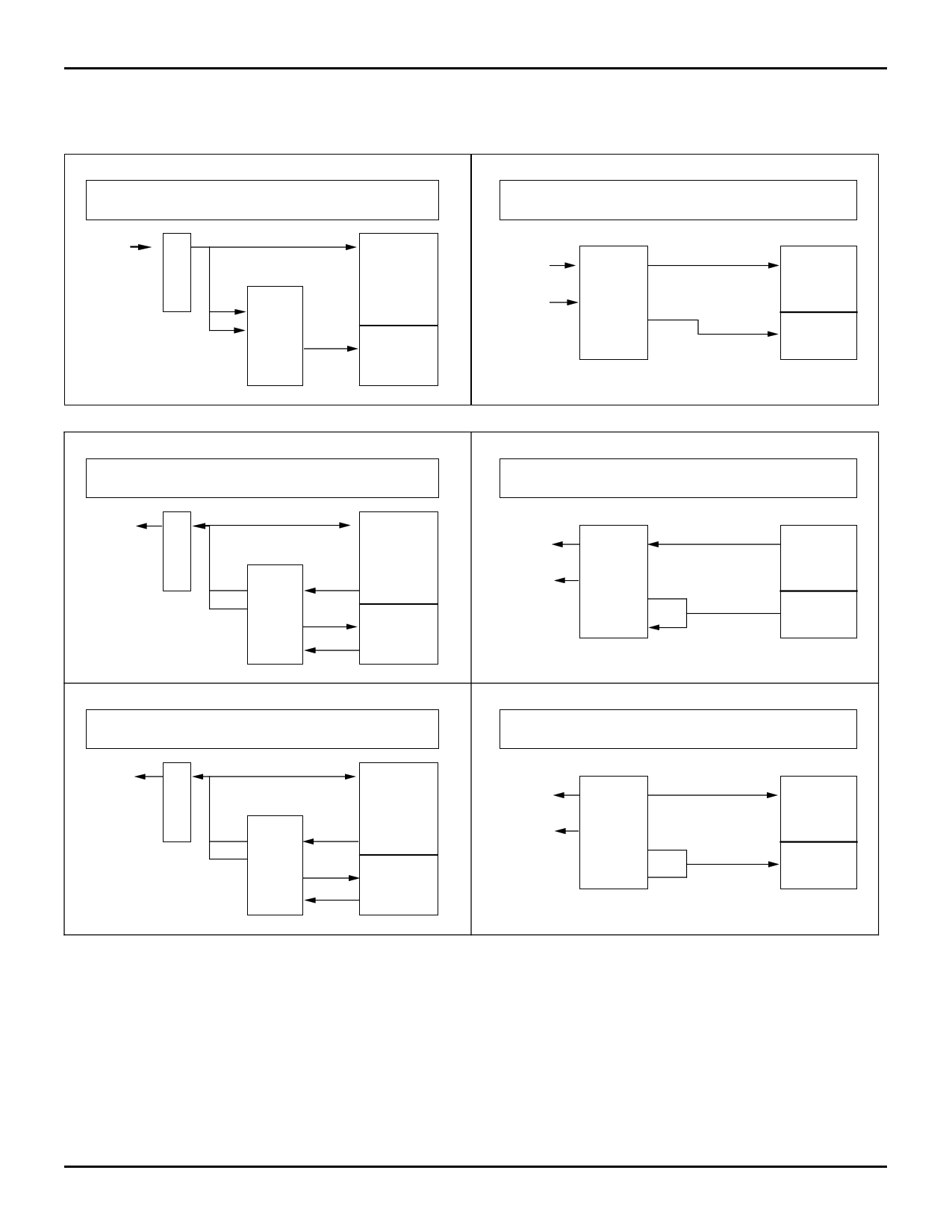

SYSTEM CONFIGURATIONS

The IDT49C465 EDC unit can be used in various

configurations in an EDC system. The basic configurations

are shown below.

Figure 1 illustrates a bidirectional configuration, which is

most appropriate for systems using bidirectional memory

buses. It is the simplest configuration to understand and use.

During a correction cycle, the corrected data word can be

simultaneously output on both the system bus and memory

bus. Logically, no other parts are required for the correction

function. During partial-word-write operations, the new bytes

are internally combined with the corrected old bytes for

checkbit generation and writing to memory.

CPU

I/O

SD MD

MEMORY

I/O

Figure 3 illustrates a third configuration which utilizes

external buffers and is also well suited for systems using

memory with separate I/O buses. Since data from memory

does not need to pass through the part on every cycle, the

EDC system may operate in “bus-watch” mode. As in the

separate I/O configuration, corrected data is output on the SD

outputs.

MEMORY

INPUT BUS

CHECKBIT

I/O

MEMORY

OUTPUT BUS

CBO

CBI

SD MD

EDC

EDC

EEXXTT.B. UBFUFFEFRER

EXT. BUFFER

CBI

CBO

CHECKBITS

CPU BUS

2552 drw 07

Figure 1. Common I/O Configuration

2552 drw 05

Figure 3. Bypassed Separate I/O Configuration

Figure 2 illustrates a separate I/O configuration. This is

appropriate for systems using separate I/O memory buses.

This configuration allows separate input and output memory

buses to be used. Corrected data is output on the SD outputs

for the system and for re-write to memory. Partial word-write

bytes are combined externally for writing and checkbit

generation.

Figure 4 illustrates the single-chip generate-only mode for

very fast 64-bit checkbit generation in systems that use

separate checkbit-generate and detect-correct units. If this is

not desired, 64-bit checkbit generation and correction can be

done with just 2 EDC units. 64-bit correction is also straight-

forward, fast and requires no extra hardware for the

expansion.

CPU

MEMORY

INPUTS

SD

MD

EDC

MEMORY

OUTPUTS

CBI

CBO

CHECKBITS

2552 drw 06

Figure 2. Separate I/O Configuration

MEMORY

INPUT BUS

CHECK

BITS OUT

CHECK

BITS IN

MEMORY

INPUT BUS

MEMORY

OUTPUT BUS

CBO

64-BIT

GEN.

ONLY

CBI

LOWER UPPER

DATA

DATA

EDC

EDC

EDC

BUFFER

BUFFER

BUFFER BUFFER

CPU BUS

2552 drw 08

Figure 4. Separate Generate/Correction Units

with 64-Bit Checkbit Generation

11.7 5

5 Page

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

PRIMARY DATA PATH vs. MEMORY CONFIGURATION

SEPARATE I/O MEMORIES:

COMMON I/O MEMORIES:

1. Checkbit Generation

Write New Word to Memory

CPU

SD MD

P

CBO

IDT49C465

CBI

DIN

MAIN

MEMORY

DOUT

CHECKBIT

MEMORY

1. Checkbit Generation

Write New Word to Memory

CPU

SD MD

P

IDT49C465

CBO

CBI

I/O

MAIN

MEMORY

CHECKBIT

MEMORY

2. Data Correction

Read Memory Word

CPU

CORRECTED

SD MD

P

CBO

IDT49C465

CBI

DIN

MAIN

MEMORY

DOUT

CHECKBIT

MEMORY

2. Data Correction

Read Memory Word

CORRECTED

CPU

SD MD

P

IDT49C465

CBO

CBI

I/O

MAIN

MEMORY

CHECKBIT

MEMORY

3. Memory Generation

Re-write Corrected Word to Memory

CPU

CORRECTED

SD MD

P

CBO

IDT49C465

CBI

DIN

MAIN

MEMORY

DOUT

CHECKBIT

MEMORY

3. Memory Generation

Re-write Corrected Word to Memory

CORRECTED

CPU

SD MD

P

IDT49C465

CBO

CBI

CORRECTED

I/O

MAIN

MEMORY

CHECKBIT

MEMORY

2552 drw 13

11.7 11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet IDT49C465.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT49C460 | 32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT | Integrated Device |

| IDT49C465 | 32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT | Integrated Device |

| IDT49C466 | 64-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT | Integrated Device |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |