|

|

PDF ICL7134 Data sheet ( Hoja de datos )

| Número de pieza | ICL7134 | |

| Descripción | 14-Bit Multiplying Microprocessor-Compatible D/A Converter | |

| Fabricantes | Intersil | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICL7134 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

December 1997

ICL7134®

NOT

RECOMMENDED

FOR NEW DESIGNS

14-Bit Multiplying

Microprocessor-Compatible D/A Converter

Features

• 14-Bit Linearity (0.003% FSR)

• No Gain Adjustment Necessary

• Microprocessor-Compatible with Double Buffered

Inputs

• Bipolar Application Requires No Extra Adjustments or

External Resistors

• Low Linearity and Gain Temperature Coefficients

• Low Power Dissipation

• Full Four-Quadrant Multiplication

• 883B Processed Versions Available

Description

The ICL7134 combines a four-quadrant multiplying DAC

using thin film resistor and CMOS circuitry with an on-chip

PROM-controlled correction circuit to achieve true 14-bit

linearity without laser trimming.

Microprocessor bus interfacing is eased using standard

memory WRITE cycle timing and control signal use. Two

input buffer registers are separately loaded with the 8 least

significant bits (LS register) and the 6 most significant bits

(MS register). Their contents are then transferred to the

14-bit DAC register, which controls the current switches. The

DAC register can also be loaded directly from the data

inputs, in which case the MS and LS registers are

transparent.

The ICL7134 is available in two versions. The ICL7134U is

programmed for unipolar operation while the ICL7134B is

programmed for bipolar applications. The VREF input to the

most significant bit of the DAC is separated from the

reference input to the remainder of the ladder. For unipolar

use, the two reference inputs are tied together, while for

bipolar operation, the polarity of the MSB reference is

reversed, giving the DAC a true 2’s complement input

transfer function. Two resistors which facilitate the reference

inversion are included on the chip, so only an external

op-amp is needed. The PROM is coded to correct for errors

in these resistors as well as the inversion of the MSB.

Ordering Information

NON-LINEARITY AT 25oC

BIPOLAR VERSIONS

0.01% (12-bit)

0.006% (13-bit)

0.003% (14-bit)

UNIPLAR VERSIONS

0.01% (12-bit)

0.006% (13-bit)

0.003% (14-bit)

0 to 70

TEMPERATURE RANGE (oC)

-25 to 85

-55 to 125

ICL7134BJCJI

ICL7134BKCJI

ICL7134BLCJI

ICL7134BJIJI

ICL7134BKIJI

ICL7134BLIJI

ICL7134BJMJI

ICL7134BKMJI

ICL7134BLMJI

ICL7134UJCJI

ICL7134UKCJI

ICL7134ULCJI

ICL7134UJIJI

ICL7134UKIJI

ICL7134ULIJI

ICL7134UJMJI

ICL7134UKMJI

ICL7134ULMJI

PACKAGE

28 Ld CERDIP

28 Ld CERDIP

28 Ld CERDIP

28 Ld CERDIP

28 Ld CERDIP

28 Ld CERDIP

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2002. All Rights Reserved

1

File Number 3113.1

1 page

ICL7134

Electrical Specification V+ = +5V, VREF = +10V, TA = 25oC, AGND = DGND, IOUT at Ground Potential,

Unless Otherwise Specified. (Continued)

PARAMETER

TEST CONDITIONS

REFERENCE INPUT

Input Resistance

ANALOG OUTPUT

VRFL = VRFM, IOUT at Ground

Output Capacitance

(IOUT Terminal)

DAC Register Outputs All LOW

DAC Register Outputs All HIGH

DIGITAL INPUTS

Low State Threshold

Operating Temperature Range

High State Threshold

Input Current

Inputs between DGND to V+

Input Capacitance

(Note 5)

POWER SUPPLY

Supply Voltage Range

Functional Operation, (Note 6)

Supply Current

Excluding Ladder Network (Note 7)

NOTES:

3. Full-Scale Range (FSR) is 10V for unipolar mode, 20V (±10V) for bipolar mode.

4. Using internal feedback and reference inverting resistors.

5. Guaranteed by design, not production tested.

6. Gain error tested to 0.040% FSR, Specifications are not guaranteed.

7. D0 - D13 connected to 2.4V.

MIN

4

-

-

-

2.4

-

-

3.5

-

TYP

7

160

235

-

-

-

15

-

1.0

MAX

10

-

-

0.8

-

±1

-

6.0

2.5

Switching Specifications V+ = 5V, TA = 25oC, See Timing Diagram

PARAMETER

SYMBOL TEST CONDITIONS

Address-WRITE Set-Up Time

Address-WRITE Hold Time

CHIP SELECT-WRITE Set-Up Time

CHIP SELECT-WRITE Hold Time

WRITE Pulse Width Low

Data-WRITE Set-Up Time

Data-WRITE Hold Time

tAWs

tAWh

tCWs

tCWh

tWR

tDWs

tDWh

Note 5

Note 5

Note 5

Note 5

MIN

150

0

0

0

200

200

0

TYP

-

-

-

-

-

-

-

MAX

-

-

-

-

-

-

-

UNITS

kΩ

pF

pF

V

V

µA

pF

V

mA

UNITS

ns

ns

ns

ns

ns

ns

ns

5

5 Page

ICL7134

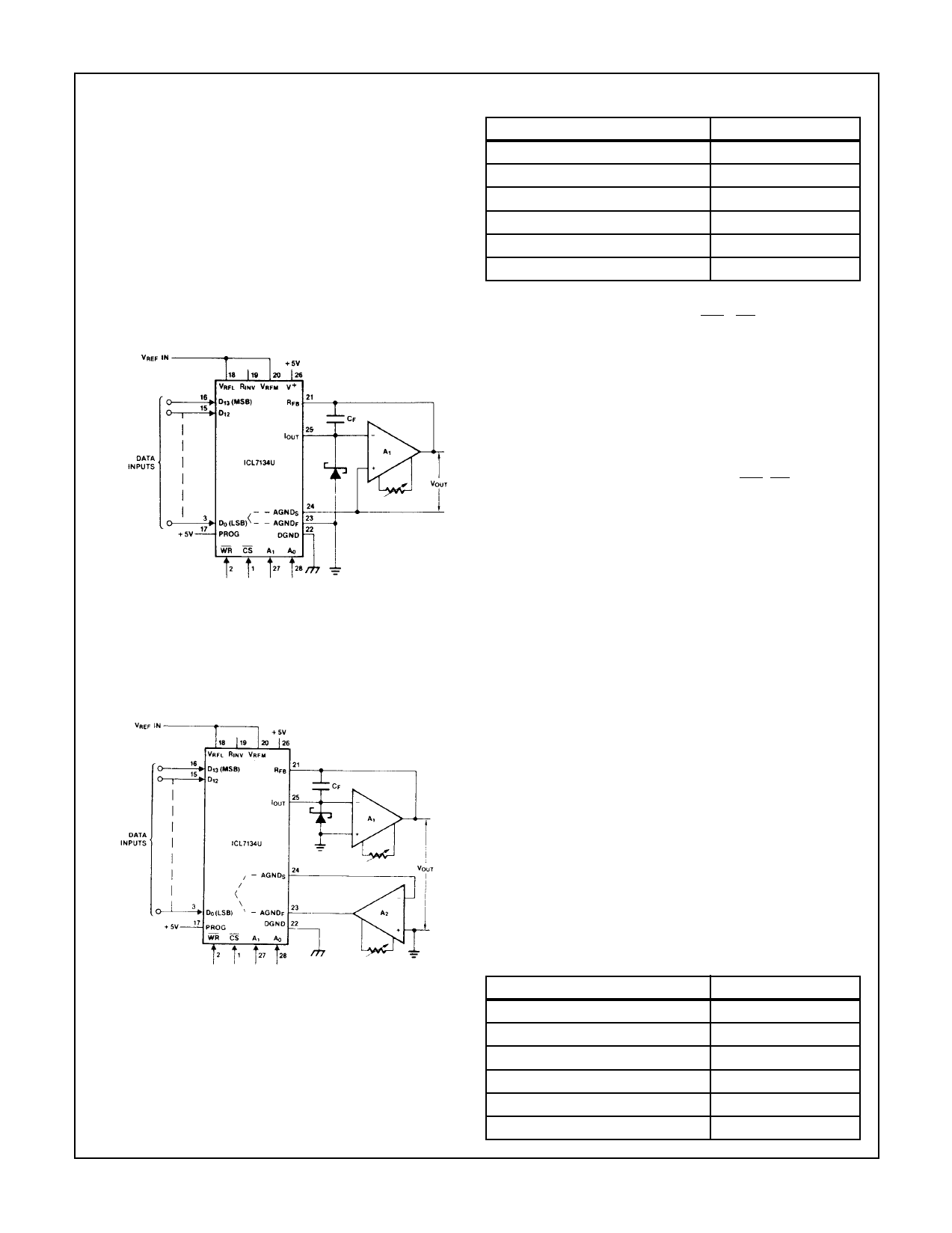

negative excursions which could damage the device, and is

only necessary with certain high spped amplifiers. For

applications where the output reference ground point is

established somewhere other than at the DAC, the circuit of

Figure 9 can be used. Here, op-amp A2 removes the slight

error due to IR voltage drop between the internal Analog

GrouND node and the external ground connection. For

13-bit or lower accuracy, omit A2 and connect AGNDF and

AGNDS directly to ground through as low a resistance as

possible.

TABLE 2. CODE TABLE - UNIPOLAR BINARY OPERATION

DIGITAL INPUT

11111111111111

10000000000001

10000000000000

01111111111111

00000000000001

00000000000000

ANALOG OUTPUT

-VREF (1 - 1/214)

-VREF (1/2 + 1/214)

-VREF/2

-VREF (1/2 - 1/214)

-VREF (1/214)

0

FIGURE 8. UNIPOLAR BINARY, TWO-QUADRANT

MULTIPLYING CIRCUIT

Zero Offset Adjustment

1. Connect all data inputs and WR, CS, A0 and A1 to

DGND.

2. Adjust offset zero-adjust trim-pot of the operational ampli-

fier A2, if used, for a maximum of 0V ±50µV at AGNDS.

3. Adjust the offset zero-adjust trim-pot of the output

op-amp, A1, for a maximum of 0V ±50µV at VOUT .

Gain Adjustment (Optional)

1. Connect all data inputs to V+, connect WR, CS, A0 and A1

to DGND.

2. Monitor VOUT for a -VREF (1 - 1/214) reading.

3. To decrease VOUT, connect a series resistor of 5Ω or less

between the reference voltage and the VRFM and VRFL

terminals (pins 20 and 18).

4. To increase VOUT, connect a series resistor of 5Ω or less

between A1 output and the RFB terminal (pin 21).

Bipolar (2’s Complement) Operation (ICL7134B)

The circuit configuration for bipolar mode operation

(ICL7134B) is shown in Figure 10. Using 2’s complement

digital input codes and positive and negative reference

voltage values, four-quadrant multiplication is obtained. The

“digital input code/analog output value” table for bipolar

mode is given in Table 3. Amplifier A3, together with internal

resistors RINV1 and RINV2 , forms a simple voltage inverter

circuit. The MSB ladder leg sees a reference input of

approximately -VREF, so the MSB’s weight is reversed from

the polarity of the other bits. In addition, the ICL7134B’s

feedback resistance is switched to 2R under PROM control,

1so/21th3a).tAtghaeinb,itphoelagrroouuntpduintgraanrrgaengiesm+eVnRt EoFf Ftiogu-rVeR9EcFan(1be-

used if necessary.

TABLE 3. CODE TABLE - BIPOLAR (2’S COMPLEMENT)

OPERATION

FIGURE 9. UNIPOLAR BINARY OPERATION WITH FORCED

GROUND

DIGITIAL INPUT

01111111111111

00000000000001

00000000000000

11111111111111

10000000000001

10000000000000

ANALOG OUTPUT

-VREF (1 - 1/213)

-VREF (1/213)

0

VREF (1/213)

VREF (1 - 1/213)

VREF

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet ICL7134.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICL7134 | 14-Bit Multiplying Microprocessor-Compatible D/A Converter | Intersil |

| ICL7135 | 41/ Digit/ BCD Output/ A/D Converter | Intersil |

| ICL7135 | 4 Digit A/D Converter with Multiplexed BCD Outputs | Maxim Integrated |

| ICL7135C | 4 1/2-Digit Precision Analog-to-Digital Converters (Rev. D) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |