|

|

PDF HYB5117405BJ-60 Data sheet ( Hoja de datos )

| Número de pieza | HYB5117405BJ-60 | |

| Descripción | 4M x 4-Bit Dynamic RAM 2k & 4k Refresh | |

| Fabricantes | Siemens | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HYB5117405BJ-60 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

4M × 4-Bit Dynamic RAM

2k & 4k Refresh

(Hyper Page Mode - EDO)

Advanced Information

• 4 194 304 words by 4-bit organization

• 0 to 70 °C operating temperature

• Hyper Page Mode - EDO - operation

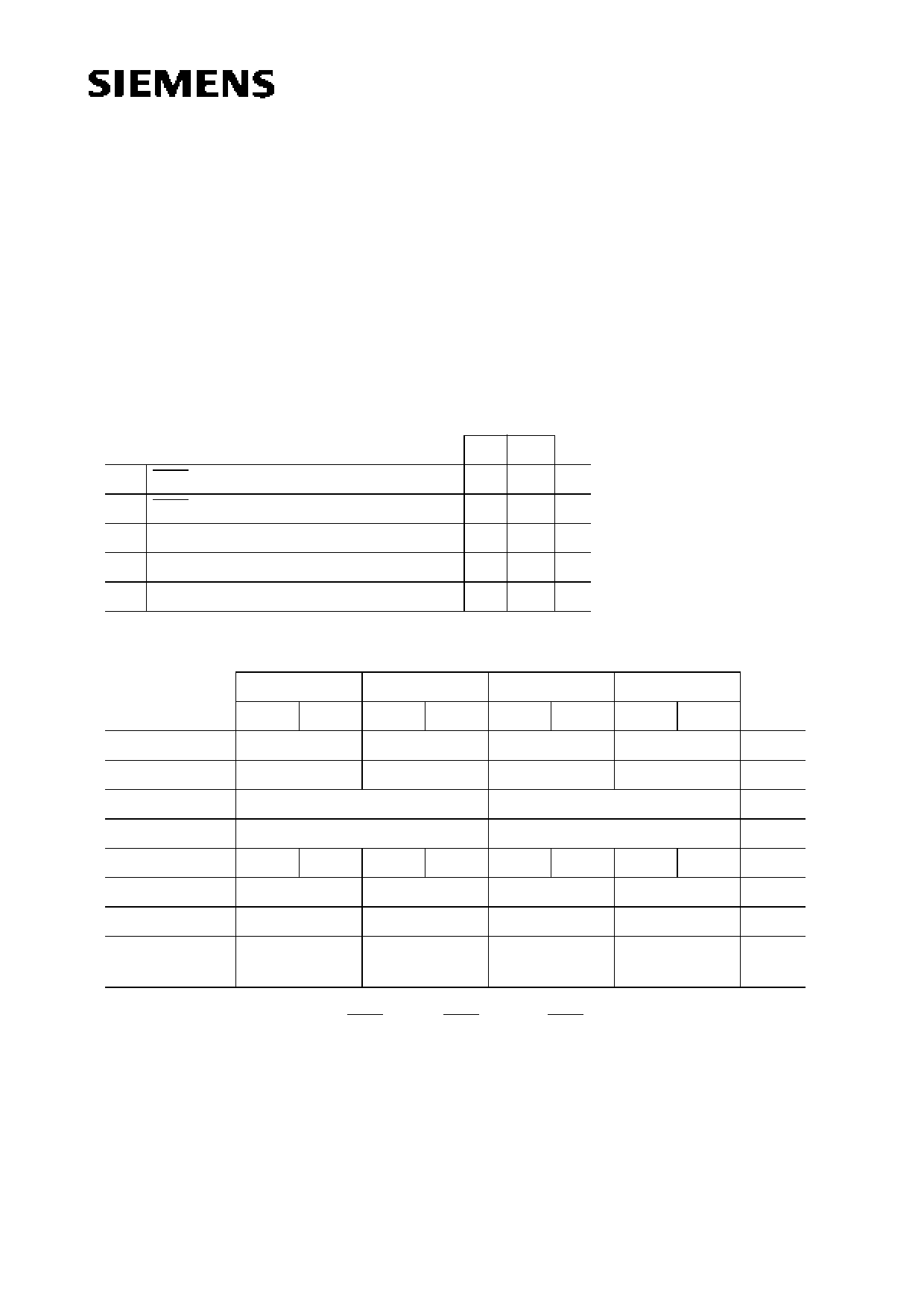

• Performance:

tRAC RAS access time

tCAC CAS access time

tAA Access time from address

tRC Read/Write cycle time

tHPC Hyper page mode (EDO) cycle time

HYB 5116405BJ-50/-60

HYB 5117405BJ-50/-60

HYB 3116405BJ/BT(L)-50/-60

HYB 3117405BJ/BT-50/-60

-50 -60

50 60 ns

13 15 ns

25 30 ns

84 104 ns

20 25 ns

• Power dissipation, refresh & addressing:

HYB 5116405 HYB 3116405 HYB 5117405 HYB 3117405

-50 -60 -50 -60 -50 -60 -50 -60

Power supply

5 V ± 10% 3.3 V ± 0.3 V 5 V ± 10% 3.3 V ± 0.3 V

Addressing

12/10

12/10

11/11

11/11

Refresh

4096 cylces / 64 ms

2048 cycles / 32 ms

L-version

4096 cycles / 128 ms

–

Active

275 220 180 144 440 385 288 252 mW

TTL Standby

11

7.2

11

7.2 mW

CMOS Standby

5.5

3.6

5.5

3.6 mW

CMOS Standby

(L-version)

–

0.72

–

– mW

• Read, write, read-modify-write, CAS-before-RAS refresh, RAS-only refresh, hidden refresh,

test mode and Self Refresh (on L-versions only)

• All inputs, outputs and clocks fully TTL (5 V versions) and LV-TTL (3.3 V version)-compatible

• Plastic Package:

P-SOJ-26/24-1 300 mil

P-TSOPII-26/24-1 300 mil

Semiconductor Group

1

1998-10-01

1 page

HYB 5116(7)405BJ-50/-60

HYB 3116(7)405BJ/BT(L)-50/-60

4M × 4 EDO-DRAM

I/O1 I/O2 I/O3 I/O4

WE &

CAS

Data In

Buffer

4

Data Out

Buffer

OE

4

No.2 Clock

Generator

11 Column

Address

A0 Buffers (11)

A1

A2 Refresh

A3 Controller

A4

A5

A6 Refresh

A7 Counter (11)

A8

11

A9

A10 11 Row

Address

Buffers (11)

RAS

No.1 Clock

Generator

11 Column

Decoder

Sense Amplifier

I/O Gating

2048

x4

4

11

Row

Decoder

...

2048

...

Memory Array

2048 x 2048 x 4

Voltage Down

Generator

V CC

V CC (internal)

SPB02823

Block Diagram for HYB 5(3)117405 (2k-refresh)

Semiconductor Group

5

1998-10-01

5 Page

HYB 5116(7)405BJ-50/-60

HYB 3116(7)405BJ/BT(L)-50/-60

4M × 4 EDO-DRAM

AC Characteristics (cont’d) 5, 6

TA = 0 to 70 °C, VCC = 5 V ± 10 % / VCC = 3.3 V ± 0.3 V, tT = 2 ns

Parameter

Symbol

Limit Values

Unit Note

-50 -60

min. max. min. max.

Test Mode

Write command setup time

Write command hold time

CAS hold time

RAS hold time in test mode

tWTS

tWTH

tCHRT

tRAHT

10 –

10 –

30 –

30 –

10 –

10 –

30 –

30 –

ns

ns

ns

ns

Semiconductor Group

11

1998-10-01

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet HYB5117405BJ-60.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HYB5117405BJ-60 | 4M x 4-Bit Dynamic RAM 2k & 4k Refresh | Siemens |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |