|

|

PDF PDC2 Data sheet ( Hoja de datos )

| Número de pieza | PDC2 | |

| Descripción | 32 bit Embedded ASIC Core Peripheral | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de PDC2 (archivo pdf) en la parte inferior de esta página. Total 25 Páginas | ||

|

No Preview Available !

Features

• Compatible with an Embedded ARM7TDMI™ Processor

• Generates Transfers to/from Serial Peripherals Such as UART, USART, SSC and SPI

• Supports Up to 12 Peripherals – Parameterizable on Request

• One ARM® Cycle Needed for a Transfer from Memory to Peripheral

• Two ARM Cycles Needed for a Transfer from Peripheral to Memory

• Fully Scan Testable up to 98% Fault Coverage

• Can be Directly Connected to the Atmel Implementation of the AMBA™ Bridge

• Not Fully Compatible with AMBA: Retract Response not Supported

Description

The Peripheral Data Controller 2 (PDC2) transfers data between on-chip peripherals

such as the UART, USART, SSC and SPI and the on- and off-chip memories. This

transfer is achieved via the AMBA Bridge using a simple arbitration mechanism

between the AMBA System Bus (ASB) and the PDC2 to control Bridge access. This

avoids processor intervention and removes the processor interrupt handling overhead.

This significantly reduces the number of clock cycles required for a data transfer and,

as a result, improves the performance of the microcontroller and makes it more power-

efficient.

The PDC2 channels are implemented in pairs, each pair being dedicated to a particu-

lar peripheral. One PDC2 channel in the pair is dedicated to the receiving channel and

one to the transmitting channel of each UART, USART, SSC and SPI.

The user interface of a PDC2 channel is integrated in the memory space of each

peripheral. It contains a 32-bit memory pointer register and a 16-bit transfer count reg-

ister plus a 32-bit register for next memory pointer and a 16-bit register for next

transfer count. The peripheral triggers PDC2 transfers using transmit and receive sig-

nals. When the programmed data is transferred, an end of transfer interrupt is

generated by the corresponding peripheral.

32-bit

Embedded ASIC

Core Peripheral

Peripheral Data

Controller 2

(PDC2)

Rev. 1734B–CASIC–02/02

1

1 page

Peripheral Data Controller 2 (PDC2)

Table 1. PDC2 Pin Description (Continued)

Name

periph_tx_rdy

[(per_n-1):0]

periph_rx_size

[(2*per_n)-1:0]

Definition

Peripheral Transmitter Ready

Peripheral Transfer Sizes for

Reception Side

Type

Input

Input

Active

Level

High

–

periph_tx_size

[(2*per_n)-1:0]

Peripheral Transfer Sizes for

Transmission Side

Input

–

periph_select

[(per_n-1):0]

periph_rx_end

[(per_n-1):0]

periph_tx_end

[(per_n-1):0]

rx_buffer_full

[(per_n-1):0]

tx_buffer_empty

[(per_n-1):0]

pdc_add[20:0]

pdc_sel

pdc_size[1:0]

pdc_write

Peripheral selects

Peripheral receive end

Input

Output

High

High

Peripheral Transmit End

Output

High

Peripheral Receive Buffer Full

Output

High

Peripheral Transmit Buffer

Empty

Output

High

PDC2 Address Bus

PDC2 Select

PDC2 Size of Transfer

Bridge Interface

Output

Output

Output

–

High

–

PDC2 Write

Output

High

Memory Management Unit/EBI

Comments

Once the holding transmit register is

available, one of these bits is set to 1

The per_n is the number of peripherals

connected to the PDC2. This value changes

the memory pointer. Two bits are reserved for

each peripheral, for example, with two

USARTs and one SPI, the size of transfer on

the receiver side for:

USART0 = periph_rx_size[1:0],

USART1 = periph_rx_size[3:2] and

SPI0 = periph_rx_size[5:4]

The per_n is the number of peripherals

connected to the PDC2. This value changes

the memory pointer. Two bits are reserved for

each peripheral, for example, with two

USARTs and one SPI, the size of transfer on

the transmit side for:

USART0 = periph_tx_size[1:0],

USART1 = periph_tx_size[3:2] and

SPI0 = periph_tx_size[5:4]

From host (Bridge) – also input of each

peripheral connected

End of receive transfer (each bit corresponds

to a peripheral) – the associated buffer for the

channel is full

End of transmit transfer (each bit

corresponds to a peripheral) – the associated

buffer for the channel is empty

End of receive transfer (each bit corresponds

to a peripheral) – the associated buffers for

the channel are full

End of transmit transfer (each bit

corresponds to a peripheral) – the associated

buffers for the channel are empty

Used by the Bridge to access the peripherals

Used by the Bridge to access the peripherals

Multiplex the spi_size inputs – used by the

Bridge to determine the size of the transfer

between memories and the SPI

Used by the Bridge to access the peripherals

1734B–CASIC–02/02

5

5 Page

Peripheral Data Controller 2 (PDC2)

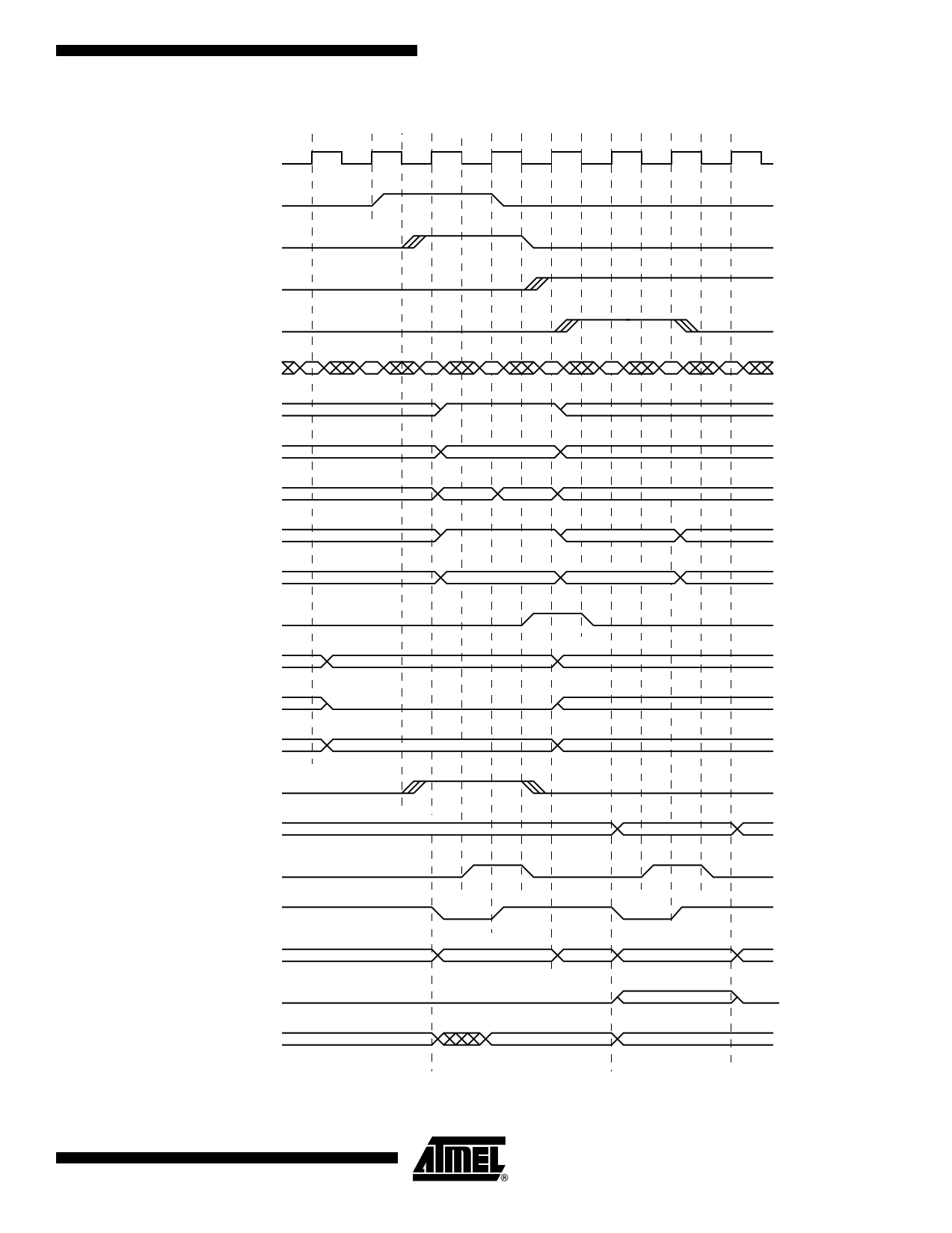

Figure 5. APB to ASB Transfer with Zero Wait States Memory Followed by an APB Access Made by Another Master

clock

areq (PDC2)

agnt (PDC2)

agnt (other master)

bridge_sel

bwait

bwrite

ba[31:0]

PDC2 status

bwrite (ASB)

ba[31:0] (ASB)

memory_write

pdc_size[1:0]

pdc_write

done

done

done

wait

done

NOT GRANTED

Memory Address

Locked Idle Cycle

Transfer

Memory Address

NOT GRANTED

bwrite from Master

ba from Master

pdc_add[20:0]

pdc_sel

brdata[31:0]

Peripheral Address

Data from Memories

Data from Bridge

periph_stb

pstb_rising

periph_add[13:0]

periph_write

data_to_master[31:0]

(output of the bridge)

14'h0000

Previous Data

Peripheral Address

14'h0000

Data for PDC Transfer

Address from Master

14'h0000

bwrite from Master

Data for Master

1734B–CASIC–02/02

11

11 Page | ||

| Páginas | Total 25 Páginas | |

| PDF Descargar | [ Datasheet PDC2.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PDC0302 | SMD POWER INDUCTORS | Superworld Electronics |

| PDC0403 | SMD POWER INDUCTORS | Superworld Electronics |

| PDC0502 | SMD POWER INDUCTORS | Superworld Electronics |

| PDC0504 | SMD POWER INDUCTORS | Superworld Electronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |