|

|

PDF W89C926 Data sheet ( Hoja de datos )

| Número de pieza | W89C926 | |

| Descripción | PCMCIA ETHERNET NETWORK TWISTED PAIR INTERFACE CONTROLLER | |

| Fabricantes | Winbond | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W89C926 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Preliminary W89C926 PENTIC+

PCMCIA ETHERNET NETWORK

TWISTED PAIR INTERFACE CONTROLLER

GENERAL DESCRIPTION

The W89C926 PENTIC+ is a CMOS device designed for easy implementation of PCMCIA R2.1

compatible CSMA/CD local area networks. The W89C926 combines a W89C902 Serial LAN

Coprocessor for Twisted-pair (SLCT) with a PCMCIA Bus Interface (PBI), thus integrating into

a single chip all the registers and logic necessary to connect the SLCT to buffer SRAMs, flash

memories (or an EEPROM), and the PCMCIA system bus.

The PCMCIA Bus Interface (PBI) is designed to provide a switchless setting architecture that allows

the card setting to be configured by software. It implements a full set of PCMCIA registers for

PCMCIA R2.1 compatibility and a set of configuration registers for switchless card setting. The card

can be configured quickly and easily by modifying the contents of the configuration registers. The

PENTIC+ can run with shared memory mode and NE2000TM I/O mode drivers on a 16-bit bus

interface. No extra effort is needed to ensure software compatibility.

The PENTIC+ provides a flexible flash memory (up to 128 KB)/EEPROM (up to 512 bytes)

architecture for PCMCIA nonvolatile storage and an ID/Configuration auto-load architecture for

power-on initialization. Vendors can store the Ethernet ID, configuration, and CIS in the flash

memory or EEPROM. The PENTIC+ will auto-load necessary information when power is switched on.

FEATURES

• Runs with NE2000 TM or shared memory drivers

• Supports up to 128 KB flash memory (8K/112K for attribute/common memory) or 512 bytes

EEPROM (for attribute memory only) for nonvolatile memory

• Uses one 16 KB SRAM or one 32 KB SRAM (if EEPROM is used) for 16 KB Ethernet ring buffer

• Auto-load algorithm provided for power-on initialization

• Supports necessary PCMCIA registers

• Configuration registers allow switchless card setting

• UTP/BNC auto media-switching function provided

• Drives necessary LEDs for network status display

• Single 5V power supply with low power consumption

• 100-pin thin package (TQFP) fits into PCMCIA Type II profile

Ethernet is a registered trademark of the Xerox Corporation.

NE2000TM is a trademark of Novell, Inc.

www.DataSheet4U.com

-1-

Publication Release Date: January 1996

Revision A1

1 page

www.DataSheet4U.com

W89C926 PENTIC+

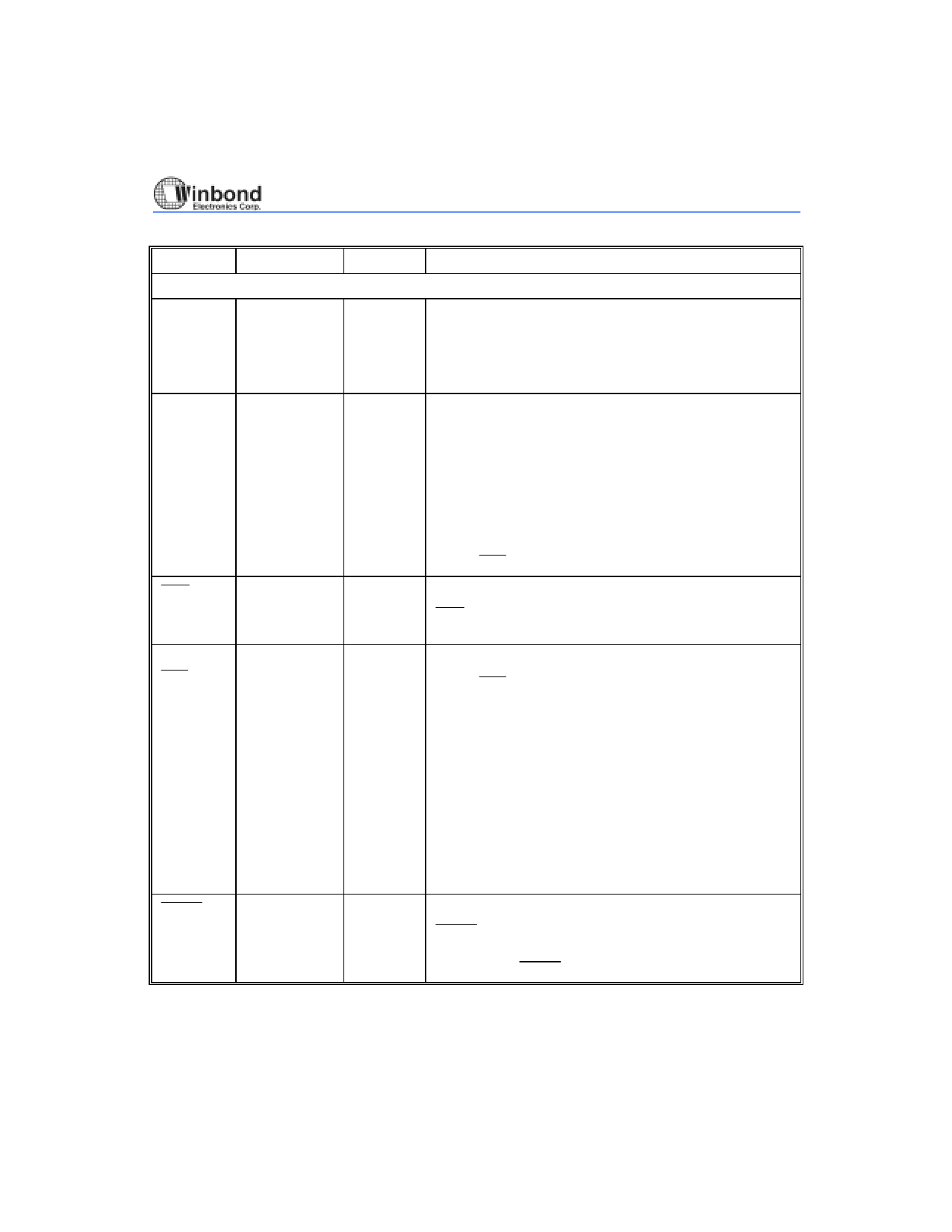

Pin Description, continued

NAME

NUMBER

Memory Support Interface

MSA0-7 90-97

MSA8-10 82, 81, 78

MSA11-13 80, 98, 84

MSA14-16 99, 69, 70

MSD0-2

89-87

MSD3-7

71-75

RCS

EECS/

FCS

77

76

MSRD

79

TYPE

O/TTL

IO/3SH

I/O/3SH

O/TTL

O/3SH

I/3SH

O/TTL

DESCRIPTION

Memory Support Address:

Latched address used to decode accesses to the on-

board memory.

Memory Support Data Bus:

Bidirectional on-board memory data bus.

EEPROM Interface:

During the EEPROM auto-load or read/write sequence,

MSD0 is used as a serial data input/output from/to

EEPROM, MSD1 outputs EEPROM commands to

EEPROM, and MSD2 sends a clock with a period of 1.2

microseconds. This function is available only when

EECS/ FCS is low during H/W reset.

SRAM Chip Select:

RCS is asserted by the PENTIC+ for SRAM chip

enable during buffer memory access.

Nonvolatile Memory Chip Select:

EECS/ FCS is asserted by the PENTIC+ for chip enable

during nonvolatile memory access. It is active low for

flash memory enable and active high for EEPROM chip

enable.

Nonvolatile Memory Detection:

During H/W reset, the PENTIC+ will determine the

existing nonvolatile memory type by sampling the

voltage level on this pin. If this pin is externally pulled

high with a 470K ohm resistor, the PENTIC+ will

determine that the memory is a flash memory; if the pin

is pulled low with a 470K ohm resistor, it will determine

that the memory is an EEPROM.

Memory Support Read:

MSRD is asserted by the PENTIC+ to strobe read data

from the on-board memory. Both SRAM and flash

memory use MSRD as the read command strobe.

www.DataSheet4U.com

Publication Release Date: January 1996

- 5 - Revision A1

5 Page

www.DataSheet4U.com

W89C926 PENTIC+

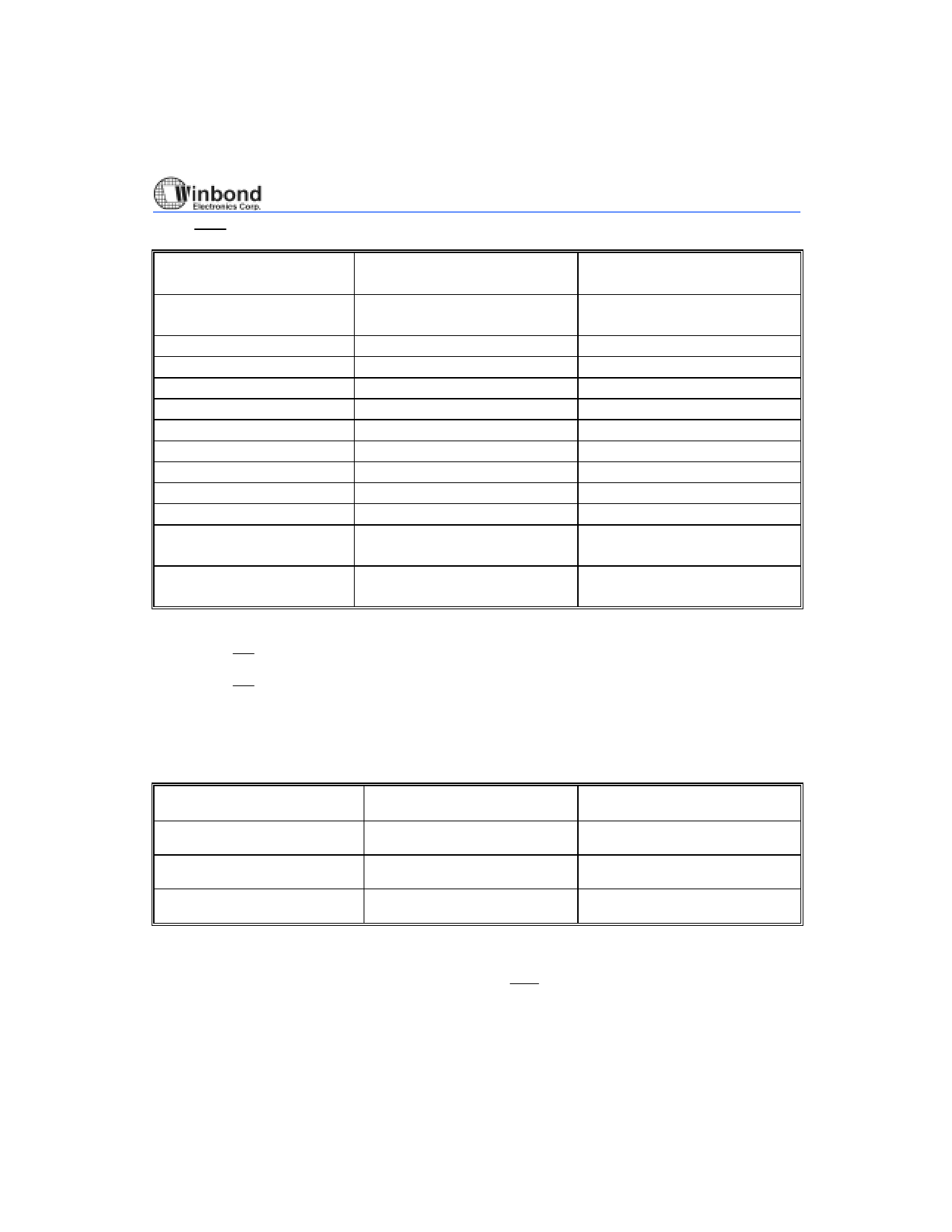

EECS/FCS Pull Low (EEPROM)

ATTRIBUTE MEMORY

TYPE

CONTENTS

OFFSET (HA0-16)

00000H

Memory (SRAM)

CIS

003D6H

- Unsued

-

00FD0H

Register

COR

00FD2H

Register

CCSR

00FD4H

Register

-

00FD6H

Register

SCR

-

Register

Reserved (see note)

00FF0H

Register

CFA

00FF2H

Register

CFB

00FF4H

Register

SR

00FF6H

Register

Reserved

00FFEH

01000H

Unused

-

03FFEH

Notes:

1.The reserved register space in the attribute space is left for future extension. Users should not place their application in this

area.

2. When EECS/ FCS is pulled high, address 00FA0H to 00FFEH is used for Ethernet ID, configuration, and registers.

Vendors should not put CIS in this region.

3. When EECS/ FCS is pulled low, Address 00000H to 003D6H is read-only. The PENTIC+ will ignore write accesses to this

area.

NE2000 Mode Mapping

I/O Mapping

SYSTEM I/O

OFFSET (HA0-4)

NAME

OPERATION

00H

LCE Core

Register

0FH

Registers

Read/Write

10H

Remote DMA Port

Remote DMA

17H Read/Write

18H

Reset Port

Software Reset

1FH

Notes:

1. The PENTIC+ decodes only HA0-4 for I/O access, so the IOBase address is left for the host adapter and the socket service

to determine.

2. To issue a S/W reset, simply issue an I/O read to the Reset Port. The PENTIC+ will assert a 600 nS internal reset pulse to

reset the core state machine. If the host tries to access the PENTIC+, WAIT will be asserted low until the reset is

completed.

www.DataSheet4U.com

- 11 -

Publication Release Date: January 1996

Revision A1

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet W89C926.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W89C92 | PCMCIA ETHERNET NETWORK TWISTED PAIR INTERFACE CONTROLLER | Winbond |

| W89C926 | PCMCIA ETHERNET NETWORK TWISTED PAIR INTERFACE CONTROLLER | Winbond |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |