|

|

PDF PC87410VLK Data sheet ( Hoja de datos )

| Número de pieza | PC87410VLK | |

| Descripción | PC87410 PCI-IDE Interface Controller | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PC87410VLK (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

October 1994

PC87410 PCI-IDE Interface Controller

General Description

The PCI-IDE Interface Controller is designed to interface the

IDE drive directly onto the PCI bus It provides write posting

and read pre-fetches allowing the CPU to run concurrently

with IDE cycles It connects IDE drIves ‘‘gluelessly’’ into the

PCI bus and supports faster ATA devices using modes 1 2

and 3 through PIO accesses It supports dual IDE channels

for up to four drives and works seamlessly with the National

Semiconductor’s SuperI OTM family of products

A full suite of software drives included with device are fully

tested with DOS 5 0–6 x Windows 3 x–4 x Windows NT

OS 2 2 x Novell Netware 3 1x–4 x and SCO UNIX 3 x

Key Features

Y Fully compatible with PCI specifications rev 2 0 (April

1993)

Y Programmable Base Address registers

Y Interfaces with the 32 bits PCI local bus to IDE drives

Y Support IDE PIO timing mode 0 1 2 of ANSI ATA

specifications

Y Support Mode 3 (11 MB s) timing proposal on en-

hanced IDE (IDE-2 or ATA-2) specifications

Y Two IDE-2 channel supported (each channel supports 2

devices)

Y Supports primary IDE or secondary IDE address

Y 16-Byte FIFO provide 4-level Posted Write and Read

ahead buffers per channel for concurrent system

operation

Y Programmable command and recovery timing for reads

and writes per channel

Y Independent timings for command registers and data

registers

Y Slew rate controlled output directly interface with IDE

devices

Y Supports either IRQ14 15 or INTA B

Y Hardware and Software chip enable disable capability

Y 100 pin PQFP package NO other glue logic needed

and 12 mA transceivers are built in

Block Diagram

TRI-STATE is a registered trademark of National Semiconductor Corporation

SuperI OTM is a trademark of National Semiconductor Corporation

C1995 National Semiconductor Corporation TL F 12073

TL F 12073 – 1

RRD-B30M75 Printed in U S A

1 page

Pin Description

Name

AD 31 0

Type

IO

C BE 3 0

PAR

I

IO

FRAME

I

TRDY

O TRI-STATE

IRDY

I

STOP

O TRI-STATE

DEVSEL

O TRI-STATE

IDSEL

I

PERR

O TRI-STATE

SERR

O TRI-STATE

INTA B O TRI-STATE

CLK

RST

I

I

PCI Interface

IOL

8 mA

8 mA

12 mA

8 mA

8 mA

8 mA

8 mA

8 mA Slew

Rate Control

Description

MULTIPLEXED ADDRESS AND DATA The direction of these pins are defined

below

Phase

Address Phase

Data Phase

Read

Write

input

output

input

COMMAND BYTE ENABLE are multiplexed Bus command and Byte enables

PARITY is even parity across AD 31 0 and C BE 3 0 PAR is an input during

writes and an output during reads

CYCLE FRAME is driven by the initiator to indicate the beginning and duration of

an access

TARGET READY indicates that the current data phase of the transaction is ready

to be completed

INITIATOR READY indicates that the initiator is ready to complete the current

data phase of the transaction

STOP indicates that the current target is requesting the initiator to stop the current

transaction

DEVICE SELECT when actively drive indicates the driving device has decoded

its adderss as the target of the current access

INITIALIZATION DEVICE SELECT is used as a chip select during configuration

read and write transactions

PARITY ERROR is used for reporting data parity errors during all PCI transactions

except a Special Cycle PERR is an output during writes and an input during

reads

SYSTEM ERROR is used for reporting address parity errors data parity errors on

the Special Cycle command or any other system error where the result will be

castrophic When reporting address parity errors SERR is an output When

reporting data parity errors for the Special Cycle command SERR is an output

during writes and an input during needs

INTERRUPT Interrupt request A and B

CLOCK Up to 33 MHz PCI Clock

RESET PCI Reset

Power and Ground

Name

Type

Description

GND

I VSS or GROUND

VCC I VDD or a5V Power to PCI buffers core and IDE buffers

Note All signals are TTL except CH0 INT (Pin 48) and CH1 INT (Pin 87) are CMOS

5

5 Page

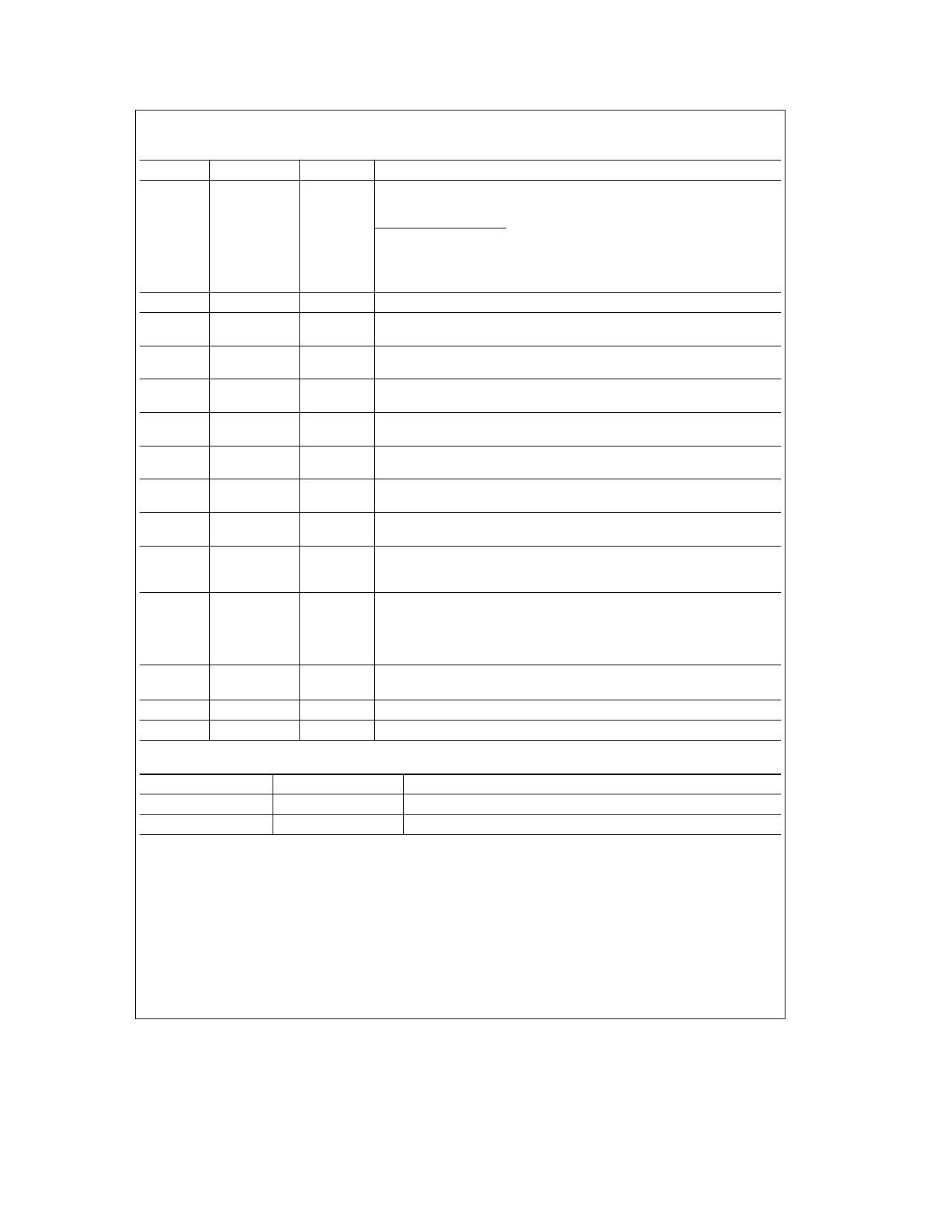

Relation Table for INTA INTB IRQ14 15 with HEADER and channel I O base registers

Condition

When chip is disabled (HEADER is ‘‘don’t care’’) and

the setting of channel 0 1 I O base register setting is

‘‘don’t care’’

HEADER is absent (Note 1) chip is enabled and

the setting of channel 0 1 I O base register setting is

‘‘don’t care’’

HEADER is present chip is enabled

Channel 0 I O is set at ‘‘primary IDE port’’

HEADER is present chip is enabled

Channel 0 I O is set at ‘‘other I O port’’

HEADER is present chip is enabled

Channel 1 I O is set at ‘‘secondary IDE port’’

HEADER is present chip is enabled

Channel 1 I O is set at ‘‘other I O port’’

HEADER is present chip is enabled

Channel 0 is not primary port and

Channel 1 is not secondary port

Outcome

IRQ14 off

IRQ15 off

INTA off

INTB off16

IRQ14 off

IRQ15 off

INTA inversion of CH0 INT if CH0

masked by the bit0 of register 43h

Otherwise it is at TRI-STATE

INTB inversion of CH1 INT if CH1

masked by the bit0 of register 47h

Otherwise it is at TRI-STATE

INT is not

INT is not

IRQ14 same value of CH0 INT if CH0 INT is not

masked by the bit0 of register 43h

Otherwise it is at TRI-STATE

INTA inversion of CH0 INT if CH0

masked by the bit0 of register 43h

Otherwise it is at TRI-STATE

IRQ14 off

INT is not

IRQ15 same value of CH1 INT if CH1 INT is not

masked by the bit0 of register 47h

Otherwise it is at TRI-STATE

INTA inversion of CH1 INT if CH1

masked by the bit0 of register 47h

Otherwise it is at TRI-STATE

IRQ15 TRI-STATE

INT is not

IRQ14 TRI-STATE

IRQ15 TRI-STATE

INTA Inversion of ORed value of CH0 INT and

CH1 INT if none of the CH0 INT and CH1 INT is

masked by the bit0 of their respective registers

Otherwise it is at TRI-STATE

Note INTB is always at TRI-STATE when HEADER is present

Note 1 HEADER absent means Logic Low

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet PC87410VLK.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PC87410VLK | PC87410 PCI-IDE Interface Controller | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |