|

|

PDF PC16552D Data sheet ( Hoja de datos )

| Número de pieza | PC16552D | |

| Descripción | Dual Universal Asynchronous Receiver/Transmitter with FIFOs | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PC16552D (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

June 1995

PC16552D

Dual Universal Asynchronous

Receiver Transmitter with FIFOs

General Description

The PC16552D is a dual version of the PC16550D Universal

Asynchronous Receiver Transmitter (UART) The two serial

channels are completely independent except for a common

CPU interface and crystal input On power-up both channels

are functionally identical to the 16450 Each channel can

operate with on-chip transmitter and receiver FIFOs (FIFO

mode) to relieve the CPU of excessive software overhead

In FIFO mode each channel is capable of buffering 16 bytes

(plus 3 bits of error data per byte in the RCVR FIFO) of data

in both the transmitter and receiver All the FIFO control

logic is on-chip to minimize system overhead and maximize

system efficiency

Signalling for DMA transfers is done through two pins per

channel (TXRDY and RXRDY) The RXRDY function is mul-

tiplexed on one pin with the OUT 2 and BAUDOUT func-

tions The CPU can select these functions through a new

register (Alternate Function Register)

Each channel performs serial-to-parallel conversion on data

characters received from a peripheral device or a MODEM

and parallel-to-serial conversion on data characters re-

ceived from the CPU The CPU can read the complete

status of each channel at any time Status information re-

ported includes the type and condition of the transfer opera-

tions being performed by the DUART as well as any error

conditions (parity overrun framing or break interrupt)

The DUART includes one programmable baud rate genera-

tor for each channel Each is capable of dividing the clock

input by divisors of 1 to (216 b 1) and producing a 16 c

clock for driving the internal transmitter logic Provisions are

also included to use this 16 c clock to drive the receiver

logic The DUART has complete MODEM-control capability

and a processor-interrupt system Interrupts can be pro-

grammed to the user’s requirements minimizing the com-

puting required to handle the communications link

The DUART is fabricated using National Semiconductor’s

advanced M2CMOSTM

Features

Y Dual independent UARTs

Y Capable of running all existing 16450 and PC16550D

software

Y After reset all registers are identical to the 16450 reg-

ister set

Y Read and write cycle times of 84 ns

Y In the FIFO mode transmitter and receiver are each

buffered with 16-byte FIFOs to reduce the number of

interrupts presented to the CPU

Y Holding and shift registers in the 16450 Mode eliminate

the need for precise synchronization between the CPU

and serial data

Y Adds or deletes standard asynchronous communication

bits (start stop and parity) to or from the serial data

Y Independently controlled transmit receive line status

and data set interrupts

Y Programmable baud generators divide any input clock

by 1 to (216 b 1) and generate the 16 c clock

Y MODEM control functions (CTS RTS DSR DTR RI

and DCD)

Y Fully programmable serial-interface characteristics

5- 6- 7- or 8-bit characters

Even odd or no-parity bit generation and detection

1- 1 - or 2-stop bit generation

Baud generation (DC to 1 5M baud) with 16 c clock

Y False start bit detection

Y Complete status reporting capabilities

Y TRI-STATE TTL drive for the data and control buses

Y Line break generation and detection

Y Internal diagnostic capabilities

Loopback controls for communications link

isolation

Break parity overrun framing error simulation

fault

Y Full prioritized interrupt system controls

Can also be reset to 16450 Mode under software control

Note This part is patented

TRI-STATE is a registered trademark of National Semiconductor Corporation

M2CMOSTM is a trademark of National Semiconductor Corporation

C1995 National Semiconductor Corporation TL C 9426

RRD-B30M75 Printed in U S A

1 page

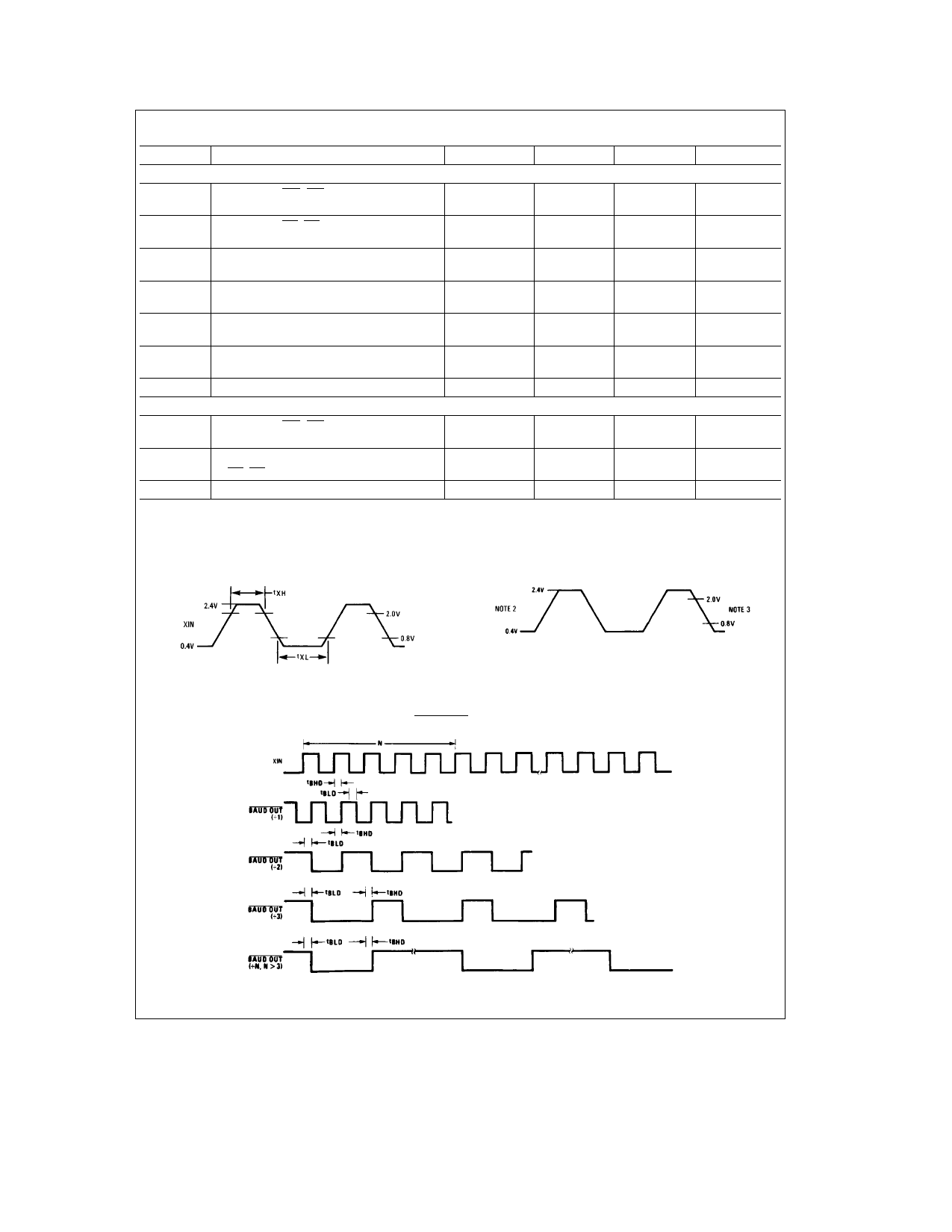

3 0 AC Electrical Characteristics TA e 0 C to a70 C VDD e a5V g10% (Continued)

Symbol

Parameter

Conditions

Min

Max

Units

TRANSMITTER

tHR Delay from WR (WR THR)

to Reset Interrupt

40 ns

tIR Delay from RD (RD IIR) to Reset

Interrupt (THRE)

40 ns

tIRS Delay from Initial INTR Reset

to Transmit Start

8

24

BAUDOUT

Cycles

tSI Delay from Initial Write to Interrupt

(Note 1)

16

24

BAUDOUT

Cycles

tSTI Delay from Start to Interrupt (THRE)

(Note 1)

8

BAUDOUT

Cycles

tSXA

Delay from Start to TXRDY Active

8

BAUDOUT

Cycles

tWXI Delay from Write to TXRDY Inactive

MODEM CONTROL

25 ns

tMDO

Delay from WR (WR MCR)

to Output

40 ns

tRIM Delay to Reset Interrupt from

RD (RD MSR)

78 ns

tSIM Delay to Set Interrupt from MODEM Input

40 ns

Note 1 This delay will be lengthened by 1 character time minus the last stop bit time if the transmitter interrupt delay circuit is active (See FIFO Interrupt Mode

Operation)

4 0 Timing Waveforms All timings are referenced to valid 0 and valid 1

External Clock Input (24 MHz Max)

AC Test Points

TL C 9426 – 2

Note 2 The 2 4V and 0 4V levels are the voltages that the inputs are driven to during AC testing

Note 3 The 2 0V and 0 8V levels are the voltages at which the timing tests are made

BAUDOUT Timing

TL C 9426 – 3

TL C 9426 – 4

5

5 Page

6 0 Pin Descriptions

The following describes the function of all DUART pins

Some of these descriptions reference internal circuits

In the following descriptions a low represents a logic 0 (0V

nominal) and a high represents a logic 1 (a2 4V nominal)

Serial channels are designated by a numerical suffix (1 or 2)

after each pin name If a numerical suffix is not associated

with the pin name then the information applies to both

channels

A0 A1 A2 (Register Select) pins 10 14 15 Address sig-

nals connected to these 3 inputs select a DUART register

for the CPU to read from or write to during data transfer

Table I shows the registers and their addresses Note that

the state of the Divisor Latch Access Bit (DLAB) which is

the most significant bit of the Line Control Register affects

the selection of certain DUART registers The DLAB must

be set high by the system software to access the Baud

Generator Divisor Latches and the Alternate Function Reg-

ister

CHSL (Channel Select) pin 16 This directs the address

and data information to the selected serial channel When

CHSL is high channel 1 is selected When CHSL is low

channel 2 is selected

CS (Chip Select) pin 18 When CS is low the chip is select-

ed This enables communication between the DUART and

the CPU Valid chip selects should stabilize according to the

tAW parameter

CTS1 CTS2 (Clear to Send) pins 40 28 When low this

indicates that the MODEM or data set is ready to exchange

data The CTS signal is a MODEM status input whose con-

dition the CPU can test by reading bit 4 (CTS) of the

MODEM Status Register for the appropriate channel Bit 4

is the complement of the CTS signal Bit 0 (DCTS) of the

MODEM Status Register indicates whether the CTS input

has changed state since the previous reading of the

MODEM Status Register CTS has no effect on the Trans-

mitter

Note Whenever the CTS bit of the MODEM Status Register changes state

an interrupt is generated if the MODEM Status Interrupt is enabled

D7 – D0 (Data Bus) pins 9 – 2 This bus comprises eight TRI-

STATE input output lines The bus provides bidirectional

communications between the UART and the CPU Data

control words and status information are transferred via the

D7 – D0 Data Bus

DCD1 DCD2 (Data Carrier Detect) pins 42 30 When low

indicates that the data carrier has been detected by the

MODEM or data set The DCD signal is a MODEM status

input whose condition the CPU can test by reading bit 7

(DCD) of the MODEM Status Register for the appropriate

channel Bit 7 is the complement of the DCD signal Bit 3

(DDCD) of the MODEM Status Register indicates whether

the DCD input has changed state since the previous reading

of the MODEM Status Register DCD has no effect on the

receiver

Note Whenever the DCD bit of the MODEM Status Register changes state

an interrupt is generated if the MODEM Status Interrupt is enabled

DSR1 DSR2 (Data Set Ready) pins 41 29 When low this

indicates that the MODEM or data set is ready to establish

the communications link with the DUART The DSR signal is

a MODEM status input whose condition the CPU can test by

reading bit 5 (DSR) of the MODEM Status Register for the

appropriate channel Bit 5 is the complement of the DSR

signal Bit 1 (DDSR) of the MODEM Status Register indi-

cates whether the DSR input has changed state since the

previous reading of the MODEM Status Register

Note Whenever the DSR bit of the MODEM Status Register changes state

an interrupt is generated if the MODEM Status Interrupt is enabled

DTR1 DTR2 (Data Terminal Ready) pins 37 27 When low

this informs the MODEM or data set that the DUART is

ready to establish a communications link The DTR output

signal can be set to an active low by programming bit 0

(DTR) of the MODEM Control Register to a high level A

Master Reset operation sets this signal to its inactive (high)

state Loop mode operation holds this signal in its inactive

state

INTR1 INTR2 (Interrupt) pins 34 17 This goes high when-

ever any one of the following interrupt types has an active

high condition and is enabled via the IER Receiver Error

Flag Received Data Available timeout (FIFO Mode only)

Transmitter Holding Register Empty and MODEM Status

The INTR signal is reset low upon the appropriate interrupt

service or a Master Reset operation

MF1 MF2 (Multi-Function) pins 35 19 This can be pro-

grammed for any one of three signal functions OUT 2

BAUDOUT or RXRDY Bits 2 and 1 of the Alternate Func-

tion Register select which output signal will be present on

this pin OUT 2 is the default signal and it is selected imme-

diately after master reset or power-up

The OUT 2 signal can be set active low by programming bit

3 (OUT 2) of the associated channel’s MODEM Control

Register to a 1 A Master Reset operation sets this signal to

its inactive (high) state Loop Mode holds this signal in its

inactive state

The BAUDOUT signal is the 16 c clock output that drives

the transmitter and receiver logic of the associated serial

channel This signal is the result of the XIN clock divided by

the value in the Division Latch Registers The BAUDOUT

signal for each channel is internally connected to provide

the receiver clock (formerly RCLK on the PC16550D)

The RXRDY signal can be used to request a DMA transfer

of data from the RCVR FIFO Details regarding the active

and inactive states of this signal are given in Section 8 5 Bit

3

MR (Master Reset) pin 21 When this input is high it clears

all the registers (except the Receiver Buffer Transmitter

Holding and Divisor Latches) and the control logic of the

DUART The states of various output signals (SOUT INTR

OUT 2 RTS DTR) are affected by an active MR input (Re-

fer to Table III ) This input is buffered with a TTL-compatible

Schmitt Trigger

RD (Read) pin 24 When RD is low while the chip is select-

ed the CPU can read status information or data from the

selected DUART register

RTS1 RTS2 (Request to Send) pins 36 23 When low this

informs the MODEM or data set that the UART is ready to

exchange data The RTS output signal can be set to an

active low by programming bit 1 (RTS) of the MODEM Con-

trol Register A Master Reset operation sets this signal to its

inactive (high) state Loop mode operation holds this signal

in its inactive state

11

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet PC16552D.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PC16552C | Dual Universal Asynchronous Receiver/Transmitter with FIFOs | National Semiconductor |

| PC16552CV | Dual Universal Asynchronous Receiver/Transmitter with FIFOs | National Semiconductor |

| PC16552D | Dual Universal Asynchronous Receiver/Transmitter with FIFOs | National Semiconductor |

| PC16552DV | Dual Universal Asynchronous Receiver/Transmitter with FIFOs | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |