|

|

PDF PA7024JNI-25 Data sheet ( Hoja de datos )

| Número de pieza | PA7024JNI-25 | |

| Descripción | Programmable Electrically Erasable Logic Array | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de PA7024JNI-25 (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

CPoAmInmd7ue0srct2riai4al/l

PA7024 PEELTM Array

Programmable Electrically Erasable Logic Array

Features

s CMOS Electrically Erasable Technology

- Reprogrammable in 24-pin DIP, SOIC and

28-pin PLCC packages

-Optional JN package for 22V10 power/ground

compatibility

s Most Powerful 24-pin PLD Available

- 20 I/Os, 2 inputs/clocks, 40 registers/latches

- 40 logic cell output functions

- PLA structure with true product-term sharing

- Logic functions and registers can be I/O-buried

s Flexible Logic Cell

- Multiple output functions per cell

- D,T and JK registers with special features

- Independent or global clocks, resets, presets,

clock polarity and output enables

-Sum of products logic for output enable

General Description

The PA7024 is a member of the Programmable Electrically

Erasable Logic (PEEL™) Array family based on ICT’s

CMOS EEPROM technology. PEEL™ Arrays free design-

ers from the limitations of ordinary PLDs by providing the

architectural flexibility and speed needed for today’s pro-

grammable logic designs. The PA7024 is by far the most

powerful 24-pin PLD available today with 20 I/O pins, 2

input/global-clocks and 40 registers/latches (20 buried logic

cells and 20 I/O registers/latches). Its logic array imple-

ments 84 sum-of-product logic functions that share 80

product terms. The PA7024’s logic and I/O cells (LCCs,

IOCs) are extremely flexible, offering two output functions

per logic cell (a total of 40 for all 20 logic cells). Logic cells

are configurable as D, T, and JK registers with independent

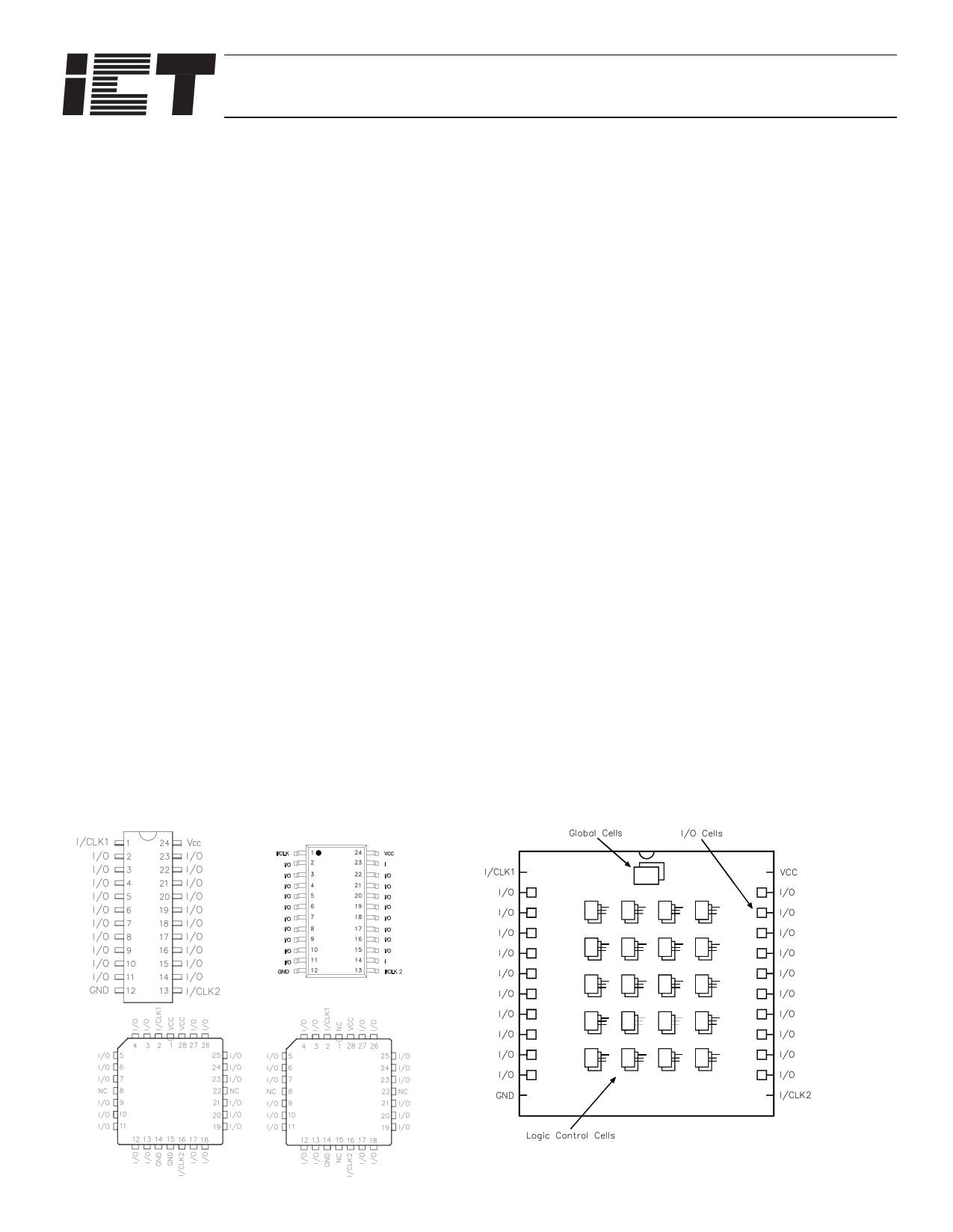

Figure 1: Pin Configuration

s High-Speed Commercial and Industrial Versions

- As fast as 10ns/15ns (tpdi/tpdx), 71.4MHz (fMAX)

- Industrial grade available for 4.5 to 5.5V Vcc

and -40 to +85°C temperatures

s Ideal for Combinatorial, Synchronous and

Asynchronous Logic Applications

- Integration of multiple PLDs and random logic

- Buried counters, complex state-machines

- Comparators, decoders, multiplexers and

other wide-gate functions

s Development and Programmer Support

- ICT PLACE Development Software

- Fitters for ABEL, CUPL and other software

-Programming support by ICT PDS-3 and popular third-

party programmers

or global clocks, resets, presets, clock polarity, and other

special features. This makes them suitable for a wide vari-

ety of combinatorial, synchronous and asynchronous logic

applications. With pin compatibility and super-set function-

ality to most 24-pin PLDs, (22V10, EP610/630, GAL6002),

the PA7024 can implement designs that exceed the archi-

tectures of such devices. The PA7024 supports speeds as

fast as 10ns/15ns (tpdi/tpdx) and 71.4MHz (fMAX) at mod-

erate power consumption 120mA (85mA typical). Packag-

ing includes 24-pin DIP, SOIC and 28-pin PLCC (see Figure

1). Development and programming support for the PA7024

is provided by ICT and popular third-party development tool

manufacturers.

Figure 2. Block Diagram

DIP

PLCC-J

SOIC

PLCC-JN

1 of 6

1 page

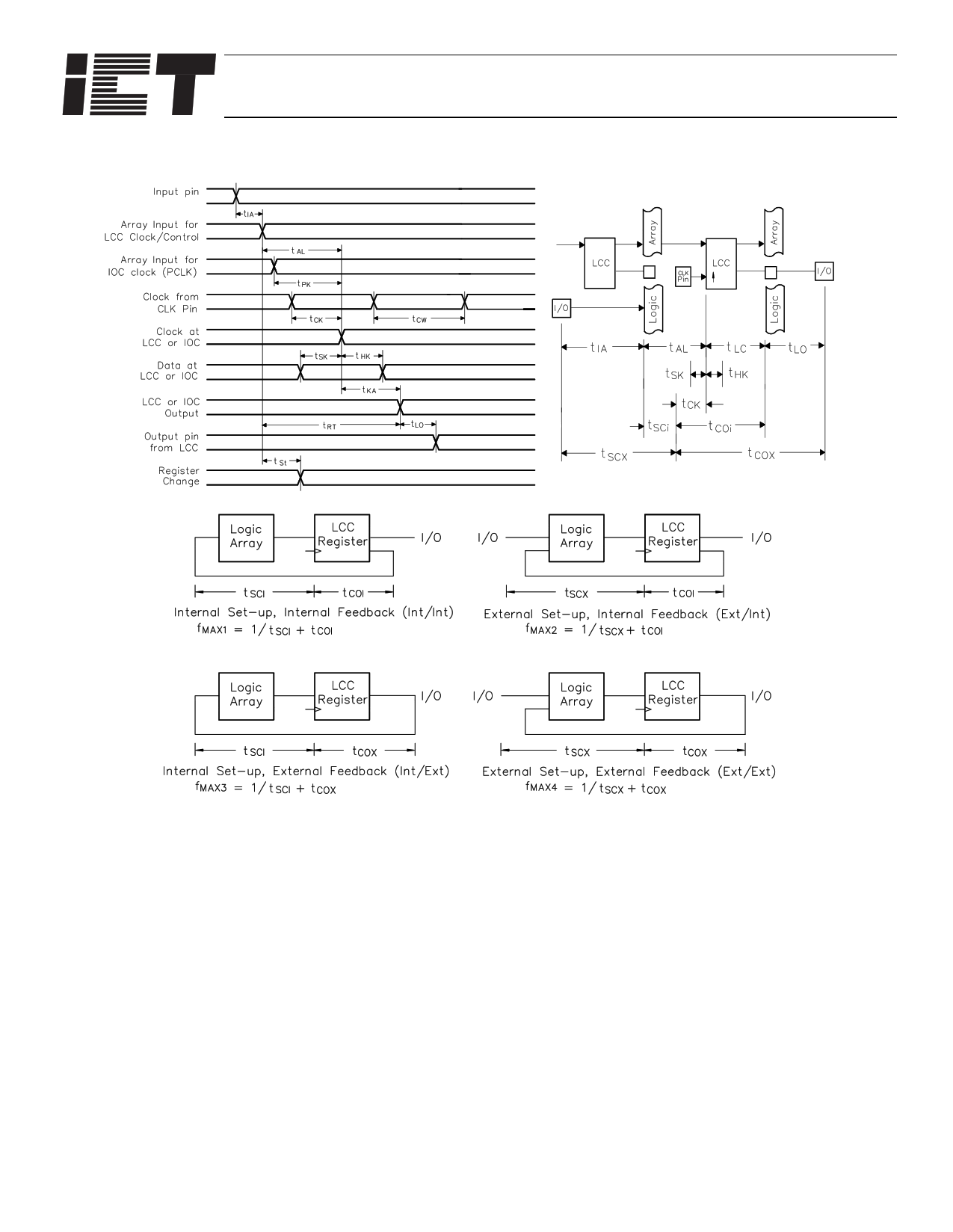

Sequential Timing - Waveforms and Block Diagram

PA7024

Notes

1. Minimum DC input is -0.5V, however inputs may undershoot to -2.0V for

periods less than 20ns.

2. Test points for Clock and VCC in tR,tF,tCL,tCH, and tRESET are referenced

at 10% and 90% levels.

3. I/O pins are 0V or VCC.

4. Test one output at a time for a duration of less than 1 sec.

5. Capacitances are tested on a sample basis.

6. Test conditions assume: signal transition times of 5ns or less from the

10% and 90% points, timing reference levels of 1.5V (unless otherwise

specified).

7. tOE is measured from input transition to VREF ±0.1V (See test loads for

VREF value). tOD is measured from input transition to VOH -0.1Vor VOL

+0.1V.

8. “System-clock” refers to pin 1 or 13 (2 or 16 PLCC) high speed clocks.

9. For T or JK registers in toggle (divide by 2) operation only.

10. For combinatorial and async-clock to LCC output delay.

11. ICC for a typical application: This parameter is tested with the device

programmed as a 10-bit D-type counter.

12. Test loads are specified in Section 5 of this Data Book.

13. “Async. clock” refers to the clock from the Sum term (OR gate).

14. The “LCC” term indicates that the timing parameter is applied to the

LCC register. The “IOC” term indicates that the timing parameter is

applied to the IOC register. The “LCC/IOC/INC” term indicates that the

timing parameter is applied to both the LCC, IOC and INC registers.

15. The term “Input” without any reference to another term refers to an

(external) input pin.

16. The parameter tSPI indicates that the PCLK signal to the IOC register is

always slower than the data from the pin or input by the absolute value

of (tSK -tPK -tIA). This means that no set-up time for the data from the

pin or input is required, i.e. the external data and clock can be sent to

the device simultaneously. Additionally, the data from the pin must

remain stable for tHPI time, i.e. to wait for the PCLK signal to arrive at

the IOC register.

17. Typical (typ) ICC is measured at TA =25°C, Freq = 25MHz, VCC =5V.

5 of 6

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet PA7024JNI-25.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PA7024JNI-25 | Programmable Electrically Erasable Logic Array | ETC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |