|

|

PDF TDA8755 Data sheet ( Hoja de datos )

| Número de pieza | TDA8755 | |

| Descripción | YUV 8-bit video low-power analog-to-digital interface | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TDA8755 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

TDA8755

YUV 8-bit video low-power

analog-to-digital interface

Product specification

Supersedes data of June 1994

File under Integrated Circuits, IC02

Philips Semiconductors

1995 Mar 09

1 page

Philips Semiconductors

YUV 8-bit video low-power

analog-to-digital interface

Product specification

TDA8755

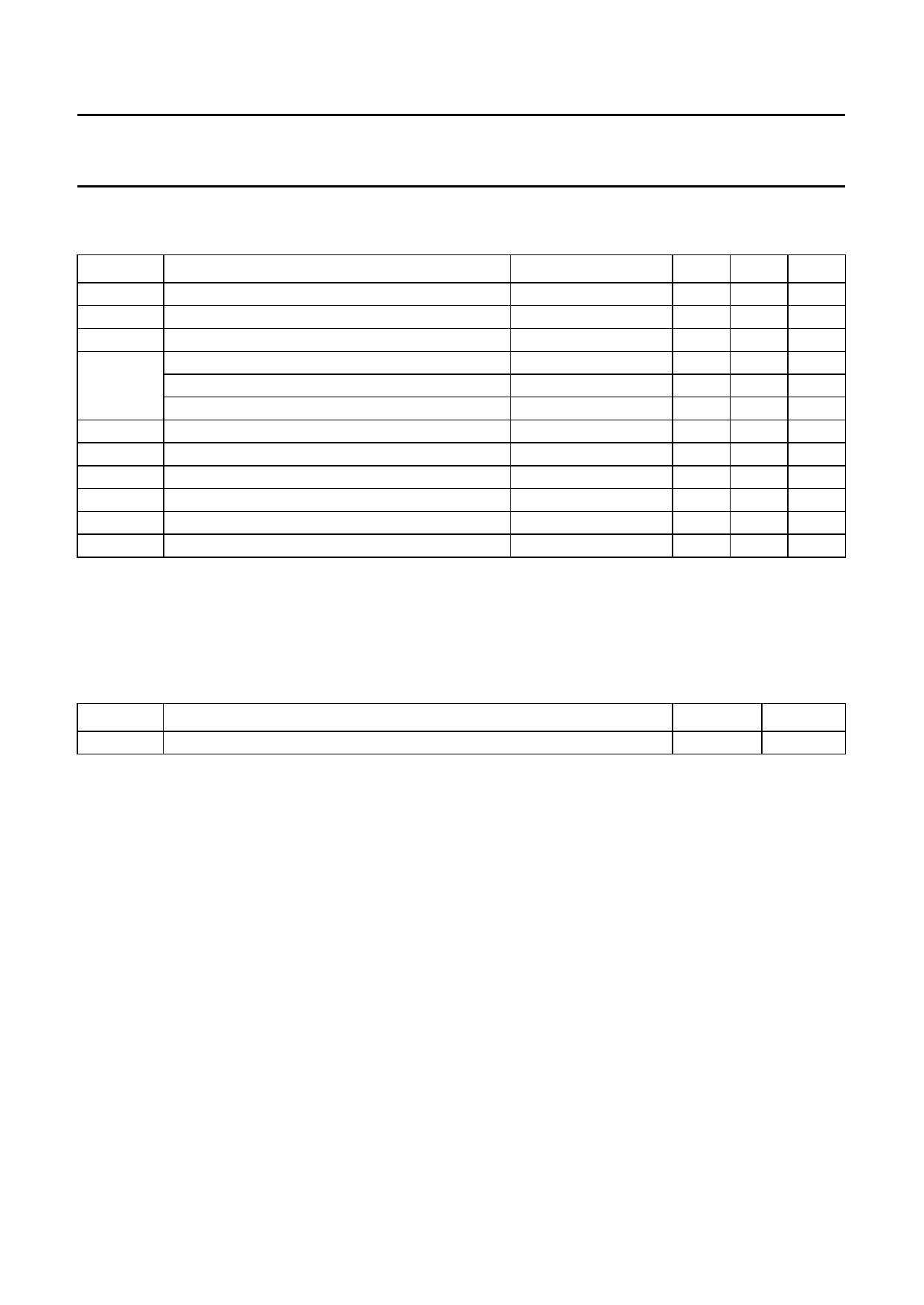

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC134).

SYMBOL

PARAMETER

CONDITIONS

VCCA

VCCD

VCCO

∆VCC

VI

Vclk(p-p)

IO

Tstg

Tamb

Tj

analog supply voltage

digital supply voltage

output stages supply voltage

supply voltage difference between VCCA and VCCD

supply voltage difference between VCCO and VCCD

supply voltage difference between VCCA and VCCO

input voltage

AC input voltage for switching (peak-to-peak value)

output current

storage temperature

operating ambient temperature

junction temperature

referenced to AGND

referenced to DGND

MIN.

−0.3

−0.3

−0.3

−1.0

−1.0

−1.0

−

−

−

−55

0

−

MAX.

+7.0

+7.0

+7.0

+1.0

+1.0

+1.0

+5.0

VCCD

+6

+150

+70

+150

UNIT

V

V

V

V

V

V

V

V

mA

°C

°C

°C

HANDLING

Inputs and outputs are protected against electrostatic discharges in normal handling. However, to be totally safe, it is

desirable to take normal precautions appropriate to handling integrated circuits.

THERMAL CHARACTERISTICS

SYMBOL

PARAMETER

Rth j-a

thermal resistance from junction to ambient in free air

VALUE

70

UNIT

K/W

1995 Mar 09

5

5 Page

Philips Semiconductors

YUV 8-bit video low-power

analog-to-digital interface

Product specification

TDA8755

handbook, full pagewidth

sample N

sample N 4

CLK

12 3 4 5

HREF

output

data

t su

N4

N3

N2

N1

sample N

output data valid

N

th

MLA732 - 1

The output data is valid 4 clock periods after HREF goes HIGH.

Fig.6 Timing definition for set-up and hold times (HREF signal).

handbook, full pagewidthsample N

CLK

4 clock periods (Tclk )

HREF

output

data

N4

N3

N3

sample N 4 x T clk

sample N 4 (Tclk 1)

output data valid

MLA731 - 1

When the HREF period is a multiple of 4 clock periods, the output data is valid without any clock delay.

The internal circuit always gives an internal delay of 4 clock periods as illustrated in Fig.6.

Fig.7 Timing diagram (HREF signal).

1995 Mar 09

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet TDA8755.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TDA8751T | QPSK receiver | NXP Semiconductors |

| TDA8752 | Triple high speed Analog-to-Digital Converter ADC | NXP Semiconductors |

| TDA8752A | Triple high-speed Analog-to-Digital Converter ADC | NXP Semiconductors |

| TDA8752AH | Triple high-speed Analog-to-Digital Converter ADC | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |