|

|

PDF TDA8376AH Data sheet ( Hoja de datos )

| Número de pieza | TDA8376AH | |

| Descripción | I2C-bus controlled PAL/NTSC TV processors | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TDA8376AH (archivo pdf) en la parte inferior de esta página. Total 44 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

TDA8376; TDA8376A

I2C-bus controlled PAL/NTSC TV

processors

Objective specification

File under Integrated Circuits, IC02

1996 Jan 26

1 page

VP2 (+8 V)

FBI

PH2LF

SCO

VP1 (+8 V)

8 37

SCL SDA

PH1LF

DECBG

DECDIG

HOUT

34

44 5 1 43 41 39 40

TDA8376(A)

I2C-BUS

TRANSCEIVER

CONTROL DACs

16 x 6 bits

2 x 4 bits

VIDEO

IDENTIFICATION

VCO

AND

CONTROL

ref

SYNC

SEPARATOR

AND 1st LOOP

VERTICAL

SYNC

SEPARATOR

ref

2nd LOOP AND

HORIZONTAL

OUTPUT

HORIZONTAL/

VERTICAL

DIVIDER

BLACK

STRETCHER

EW

GEOMETRY

46

49

VERTICAL

GEOMETRY

47

48

50

51

2

BLACK

WHITE CURRENT

POINT STABILIZER

BRI CONTR

18

22

SW

CVBS

SWITCH

TRAP BAND PASS

FILTER

TUNING

SW

S-VHS SWITCH

HUE

PAL/NTSC

DECODER

DELAY,

PEAKING AND

CORING

SAT

G-Y MATRIX

AND

SAT CONTROL

RGB MATRIX

AND

OUTPUT

21

20

19

RGB INPUT

AND

SWITCH

14

15

16

17

10 42 45

9 13

6 7 11 38

12 36

GND1 GND2 GND3

CVBSEXT

CVBSINT

CHROMA

DECFT

PIPO

CVBS/TXT

CVBS/Y

35 34

DET

33

4.4 3.6

MHz MHz

30 29 32

RYO BYO RYI

TDA4665

31 28 27

BYI

LUMIN

23 24 25 26

RI1 GI1 BI1

RGBIN1

EWD

EHTO

VDR(p)

VDR(n)

VSC

Iref

CBLK

BLKIN

BCLIN

RO

GO

BO

RGBIN2

RI2

GI2

BI2

MGE078

SECref

XTAL2 XTAL1

LUMOUT

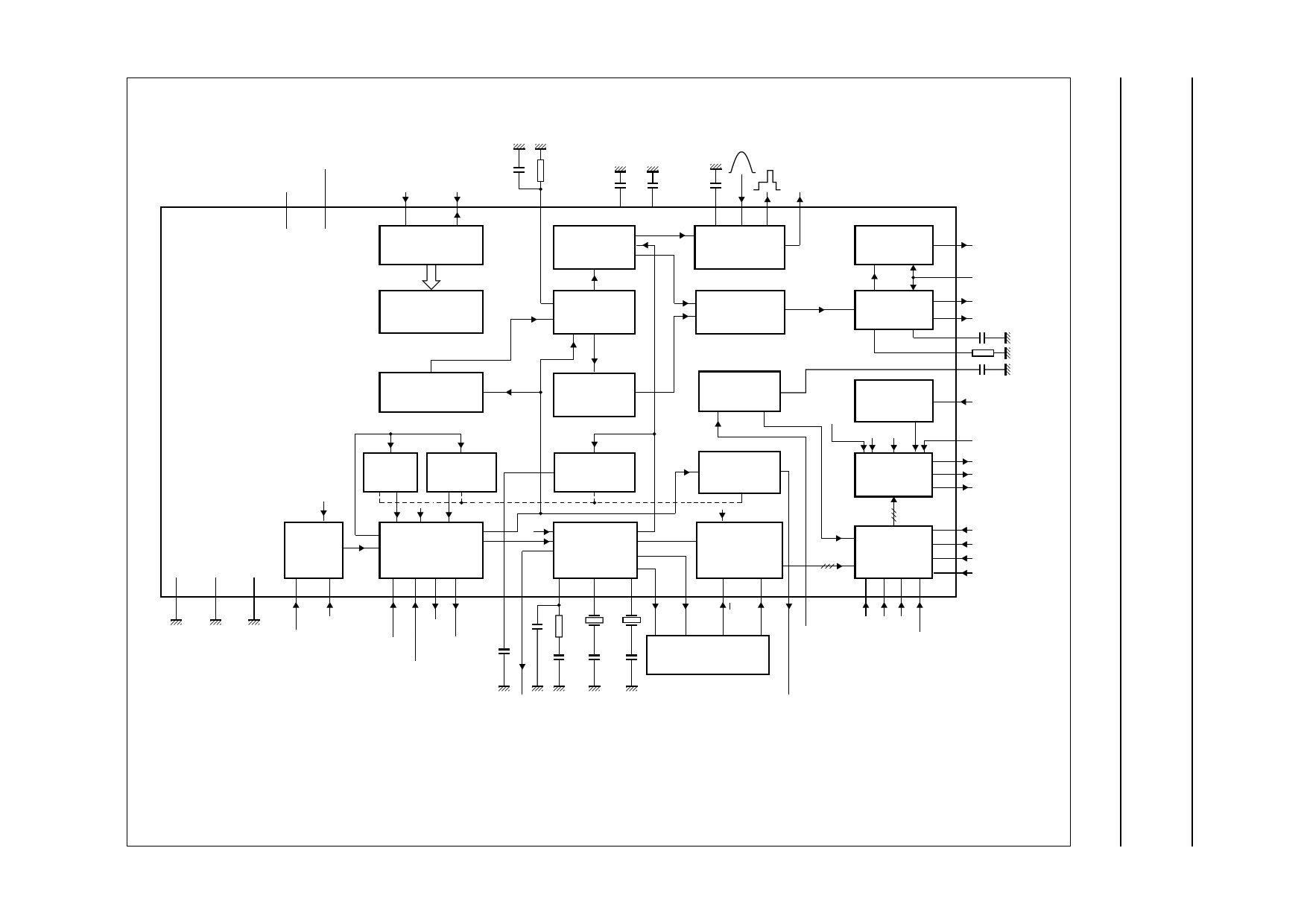

Fig.1 Block diagram (SDIP52; SOT247-1).

5 Page

Philips Semiconductors

I2C-bus controlled PAL/NTSC TV processors

Objective specification

TDA8376; TDA8376A

To obtain a smooth switching-on and switching-off

behaviour of the horizontal output stage the horizontal

output frequency is doubled during switch-on and

switch-off (slow start/stop). During that time the duty factor

of the output pulse has such a value that maximum safety

is obtained for the output stage

To protect the horizontal output transistor the horizontal

drive is switched off when a power-on reset is detected.

The drive signal is switched on again when the normal

switch-on procedure is followed, i.e. all sub-address bytes

must be sent and, after calibration, the horizontal drive

signal will be released again via the slow start procedure.

When the coincidence detector indicates an out-of-lock

situation the calibration procedure is repeated.

The circuit has a second control loop to generate the drive

pulses for the horizontal driver stage. To prevent the

horizontal output transistor being switched on during

flyback the horizontal drive output is gated with the flyback

pulse.

The vertical sawtooth generator drives the vertical output

and E-W correction drive circuits. The geometry

processing circuits provide control of horizontal shift, E-W

width, E-W parabola/width ratio, E-W corner/parabola

ratio, trapezium correction, vertical shift, vertical slope,

vertical amplitude, and the S-correction. All these controls

can be set via the I2C-bus. The geometry processor has a

differential current output for the vertical drive signal and a

single-ended output for the E-W drive. Both the vertical

drive and the E-W drive outputs can be modulated for EHT

compensation. The EHT compensation pin is also used for

overvoltage protection.

The TDA8376A geometry processor also offers the

possibility for a flexible vertical and horizontal zoom mode

for 16 : 9 applications. Because of this feature an

additional control can be added on the remote control so

that the viewer can adjust the picture.

In addition the de-interlace of the vertical output can be set

via the I2C-bus.

To avoid damage of the picture tube when the vertical

deflection fails, the guard output current of the TDA8350

can be supplied to the sandcastle output. When a failure is

detected the RGB-outputs are blanked and a bit is set

(NDF) in the status byte of the I2C-bus. When no vertical

deflection output stage is connected this guard circuit will

also blank the output signals. This can be overruled by the

EVG bit of subaddress 0A (see Table 1).

7.4 Colour decoder

The colour decoder contains an alignment-free crystal

oscillator, a killer circuit and the colour difference

demodulators. The 90° phase shift for the reference signal

is made internally. The demodulation angle and gain ratio

for the colour difference signals for PAL and NTSC are

adapted to the standard.

The colour decoder is very flexible. Together with the

SECAM decoder TDA8395 an automatic multistandard

decoder can be designed. In the automatic mode the

SECAM identification is accepted only when the vertical

frequency is 50 Hz. In the forced mode the system can

also identify signals with a vertical frequency of 60 Hz.

Which standard the IC can decode depends on the

external crystals. If a 4.4 MHz and a 3.5 MHz crystal are

used PAL 4.4, NTSC 4.4, NTSC 3.5 and PAL 3.5 can be

decoded. If two 3.5 MHz crystals are used PAL N and M

can be decoded. If one crystal is connected only

PAL/NTSC 4.4 or PAL/NTSC 3.5 can be decoded. The

crystal frequency of the decoder is used to tune the line

oscillator. Therefore the value of the crystal frequency

must be given to the IC via the I2C-bus. For a reliable

calibration of the horizontal oscillator it is very important

that the crystal indication bits (XA and XB) are not

corrupted (see Table 6). For this reason the crystal bits

(SXA and SXB) can be read in the output bytes so that the

software can check the I2C-bus transmissions

(see Table 38).

7.5 RGB output circuit and black-current

stabilization

The colour-difference signals are matrixed with the

luminance signal to obtain the RGB-signals. For the

RGB-inputs linear amplifiers have been chosen so that the

circuit is suited for signals coming from the SCART

connector. The RGB2 inputs (pins 14 to 17) have priority

over the RGB1 inputs (pins 23 to 26). Both fast blanking

inputs can be blocked by I2C-bus controls. The contrast

and brightness controls operate on internal and external

signals.

1996 Jan 26

11

11 Page | ||

| Páginas | Total 44 Páginas | |

| PDF Descargar | [ Datasheet TDA8376AH.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TDA8376A | I2C-bus controlled PAL/NTSC TV processors | NXP Semiconductors |

| TDA8376AH | I2C-bus controlled PAL/NTSC TV processors | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |