|

|

PDF TDA7503 Data sheet ( Hoja de datos )

| Número de pieza | TDA7503 | |

| Descripción | DUAL DSP PLUS MICRO FOR AUDIO APPLICATIONS | |

| Fabricantes | ST Microelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TDA7503 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

® TDA7503

DUAL DSP PLUS MICRO FOR AUDIO APPLICATIONS

Dual 24-bit 40 MIPS DSP Cores

8 bit Microcontroller

4 receive and 5 transmit stereo channels of

Serial Audio Interface

Synchronous Serial Interface for communica-

tion with external processor

FIFO based mailboxes for inter-processor

communications

External Memory Interface to 128Kb SRAM or

1Mb DRAM

CORDIC co-processor

Programmable PLL to suite wide range of ex-

ternal crystal oscillation frequencies

SPI control interface

Powerful debug interfaces

1280 words Program Memory for DSP1, 768

words Program Memory for DSP0

256 words X and Y Data RAM and Data ROM

for each DSP

256 byte Data RAM for Microcontroller

768 byte Auxiliary RAM for Microcontroller

BLOCK DIAGRAM

PRODUCT PREVIEW

TQFP100

DESCRIPTION

The device is a high-performance Digital Signal

Processing IC particularly suited to Audio applica-

tions. The device contains two 24-bit 40 MIPS

DSP cores delivering a total of 80 MIPS of DSP

processing power. There is also an embedded 8-

bit Microcontroller to handle all control functions.

All data and program memories for both DSP

cores are on-chip. A variety of highly programma-

ble and flexible peripheral blocks for both the Mi-

crocontroller and the DSPs have been integrated

to form a powerful audio processing system on a

single chip.

M8051

CORE

Host

Interface 0

Host

Interface 1

AUX-RAM

768 Bytes

Mi cro

Memory

Interface

AUX-RAM

256 Bytes

Watchdog

Timer

PLL

Clock

Oscillator

DCLK

Serial

Audio

Interface

Synchronous

Audio

Interface

XDB0

XAB0

XDB1

XAB1

SRAM/

D RAM

Interface

XCHG

Interface

C ordic

Ari thmetic

U nit

X-RAM0

X-ROM0

Y-RAM0

Y-ROM0

P-RAM0

P-ROM0

DSP0

CORE

X-RAM1

X-ROM1

Y-RAM1

Y-ROM1

P-RAM1

P-ROM1

DSP1

CORE

DEBUG

Interface

July 1999

This is preliminary information on a new product now in development. Details are subject to change without notice.

1/26

1 page

TDA7503

PIN DESCRIPTION (continued)

N.

Name

Type

Reset

Status (1)

Function

75 RA10(P2.2) I/O

I Microcontroller High Byte Address Lines. This pin is the address line 10

of a 16 bit address, for external EPROM and memory mapped devices. It

can also act as GPIO using the P2 and P2DIR registers.

69 RA11(P2.3) I/O

I Microcontroller High Byte Address Lines. This pin is the address line 11

of a 16 bit address, for external EPROM and memory mapped devices. It

can also act as GPIO using the P2 and P2DIR registers.

63 RA12(P2.4) I/O

I Microcontroller High Byte Address Lines. This pin is the address line 12

of a 16 bit address, for external EPROM and memory mapped devices. It

can also act as GPIO using the P2 and P2DIR registers.

66 RA13(P2.5) I/O

I Microcontroller High Byte Address Lines. This pin is the address line 13

of a 16 bit address, for external EPROM and memory mapped devices. It

can also act as GPIO using the P2 and P2DIR registers.

65 RA14(P2.6) I/O

I Microcontroller High Byte Address Lines. This pin is the address line 14

of a 16 bit address, for external EPROM and memory mapped devices. It

can also act as GPIO using the P2 and P2DIR registers.

64 RA15(P2.7) I/O

I Microcontroller High Byte Address Lines. This pin is the address line 15

of a 16 bit address, for external EPROM and memory mapped devices. It

can also act as GPIO using the P2 and P2DIR registers.

83 RAD0(P0.0) I/O

I Microcontroller Address/Data Pins. This pin is the multiplexed address

and data line bit 0 for external EPROM and memory mapped peripherals.

It can also act as GPIO using the P0 and P0DIR registers.

82 RAD1(P0.1) I/O

I Microcontroller Address/Data Pins. This pin is the multiplexed address

and data line bit 1 for external EPROM and memory mapped peripherals.

It can also act as GPIO using the P0 and P0DIR registers.

81 RAD2(P0.2) I/O

I Microcontroller Address/Data Pins. This pin is the multiplexed address

and data line bit 2 for external EPROM and memory mapped peripherals.

It can also act as GPIO using the P0 and P0DIR registers.

80 RAD3(P0.3) I/O

I Microcontroller Address/Data Pins. This pin is the multiplexed address

and data line bit 3 for external EPROM and memory mapped peripherals.

It can also act as GPIO using the P0 and P0DIR registers.

79 RAD4(P0.4) I/O

I Microcontroller Address/Data Pins. This pin is the multiplexed address

and data line bit 4 for external EPROM and memory mapped peripherals.

It can also act as GPIO using the P0 and P0DIR registers.

78 RAD5(P0.5) I/O

I Microcontroller Address/Data Pins. This pin is the multiplexed address

and data line bit 5 for external EPROM and memory mapped peripherals.

It can also act as GPIO using the P0 and P0DIR registers.

77 RAD6(P0.6) I/O

I Microcontroller Address/Data Pins. This pin is the multiplexed address

and data line bit 6 for external EPROM and memory mapped peripherals.

It can also act as GPIO using the P0 and P0DIR registers.

76 RAD7(P0.7) I/O

I Microcontroller Address/Data Pins. This pin is the multiplexed address

and data line bit 7 for external EPROM and memory mapped peripherals.

It can also act as GPIO using the P0 and P0DIR registers.

84 xALE I/O I Microcontroller External Address Latch Enable. This pin is the address

latch enable. A logic high indicates that address/data lines 7 through 0

represent an address. Inactive for Program/Data fetches from internal

AUX.

85 WR(P3.6)

I/O

I Microcontroller Write Strobe. External data memory write strobe. This pin

can also act as GPIO using the P3 and P3DIR registers.

86 RD(P3.7)

I/O

I Microcontroller Read Strobe. External data memory read strobe. Active

Low, or GPIO. This pin can also act as GPIO using the P3 and P3DIR

registers. Disabled by setting the RDSEL bit in the PINCTL register.

70 XPSEN

I/O

I Microcontroller External Program Memory Enable. External program

memory enable pin. Active Low. Changes functionality to RD when

Microcontroller is fetching instructions out of internal AUX ram.

Controlled by the PSSEL and PSBIT bits in the PINCTL register.

5/26

5 Page

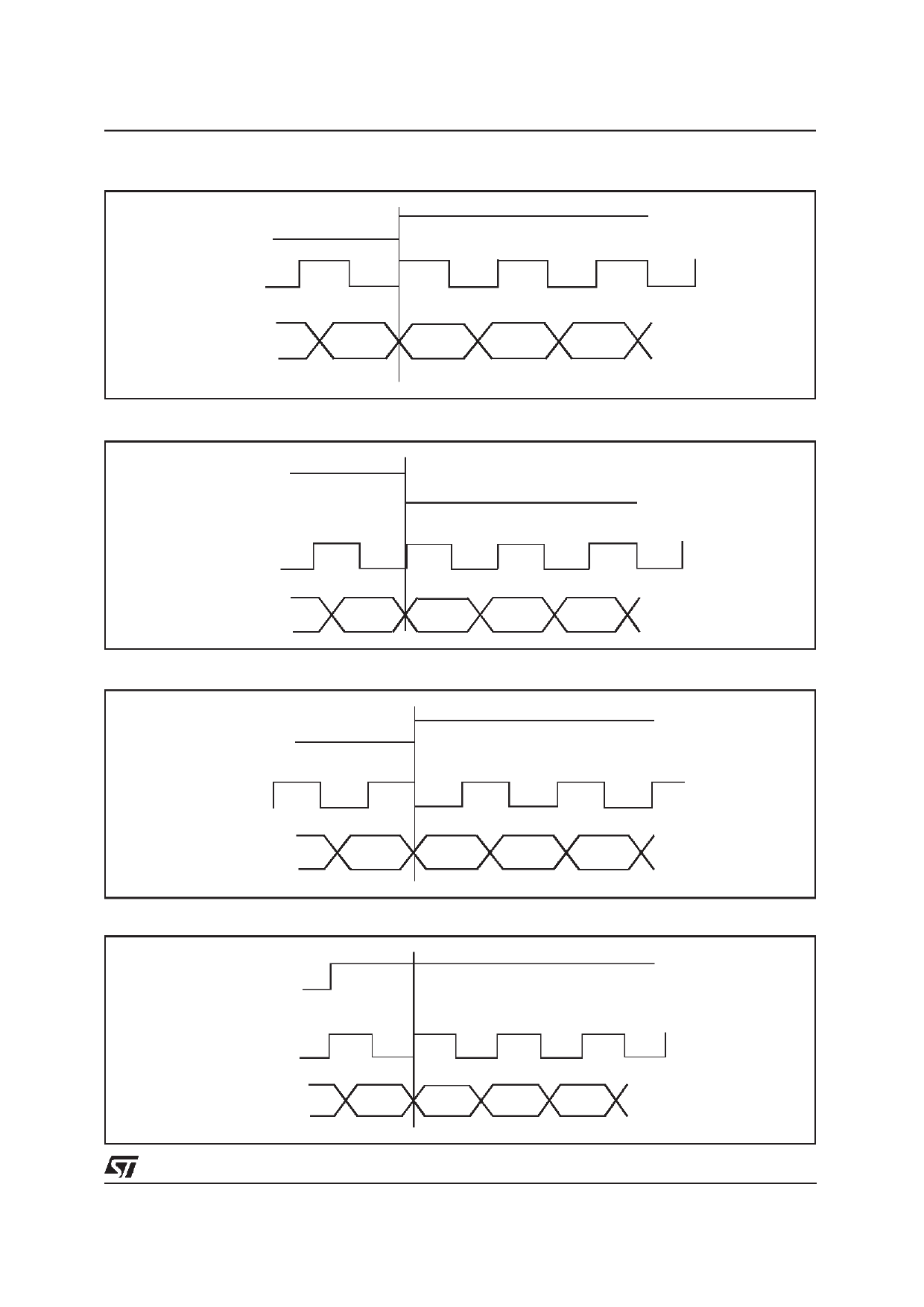

Figure 3. SAI protocol when RLRS=0; RREL=0; RCKP=1; RDIR=0.

LRCKR

LEFT

RIGHT

SCKR

SDI0

LSB(n-1) MSB(word n) MSB-1 (n) MSB-2 (n)

Figure 4. SAI protocol when RLRS=1; RREL=0; RCKP=1; RDIR=1.

LRCKR

LEFT

RIGHT

SCKR

SDI0

MSB(n-1) LSB(word n) LSB+1 (n) LSB+2 (n)

Figure 5. SAI protocol when RLRS=0; RREL=0; RCKP=0; RDIR=0.

LRCKR

SCKR

LEFT

RIG HT

SDI0

LSB(n-1) MSB(word n) MSB-1 (n)

MSB-2 (n)

Figure 6. SAI protocol when RLRS=0; RREL=1; RCKP=1; RDIR=0.

LEFT

LRCKR

SCKR

RIGHT

SDI0

LSB(n-1) MSB(word n) MSB-1 (n) MSB-2 (n)

TDA7503

11/26

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet TDA7503.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TDA7500 | DIGITAL AM/FM SIGNAL PROCESSOR | ST Microelectronics |

| TDA7501 | LINE-DRIVER FOR DIGITAL CARRADIO SIGNAL PROCESSOR | ST Microelectronics |

| TDA7502 | IN-CAR REMOTE AMPLIFIER DSP | ST Microelectronics |

| TDA7503 | DUAL DSP PLUS MICRO FOR AUDIO APPLICATIONS | ST Microelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |