|

|

PDF VG36128801A Data sheet ( Hoja de datos )

| Número de pieza | VG36128801A | |

| Descripción | CMOS Synchronous Dynamic RAM | |

| Fabricantes | Vanguard International Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de VG36128801A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

VIS

Preliminary

VG36128401A

VG36128801A

VG36128161A

CMOS Synchronous Dynamic RAM

Description

The device is CMOS Synchronous Dynamic RAM organized as 8,388,608 - word x 4 -bit x 4 - bank,

4,194,304 - word x 8 - bit x 4 - bank, or 2,097,152 - word x 16 - bit x 4 - bank. These various organizations

provide wide choice for different applications. It is designed with the state-of-the-art technology to meet stan-

dard PC100 or high speed PC133 requirement. Four internal independent banks greatly increase the perfor-

mance efficiency. It is packaged in JEDEC standard pinout and standard plastic 54-pin TSOP package.

Features

• Single 3.3V ( ±0.3V) power supply

• High speed clock cycle time : 7.5ns/10ns

• Fully synchronous with all signals referenced to a positive clock edge

• Programmable CAS Iatency (2,3)

• Programmable burst length (1,2,4,8,& Full page)

• Programmable wrap sequence (Sequential/Interleave)

• Automatic precharge and controlled precharge

• Auto refresh and self refresh modes

• Quad Internal banks controlled by BA0 & BA1 (Bank select)

• Each Bank can be operated simultaneously and independently

• I/O level : LVTTL compatible

• Random column access in every cycle

• x4, x8, x16 organization

• Input/Output controlled by DQM ( LDQM, UDQM )

• 4,096 refresh cycles/64ms

• Burst termination by burst stop and precharge command

• Burst read/single write option

The information shown is subject to change without notice.

Document : 1G5-0154

Rev.1

Page 1

1 page

VIS

Preliminary

VG36128401A

VG36128801A

VG36128161A

CMOS Synchronous Dynamic RAM

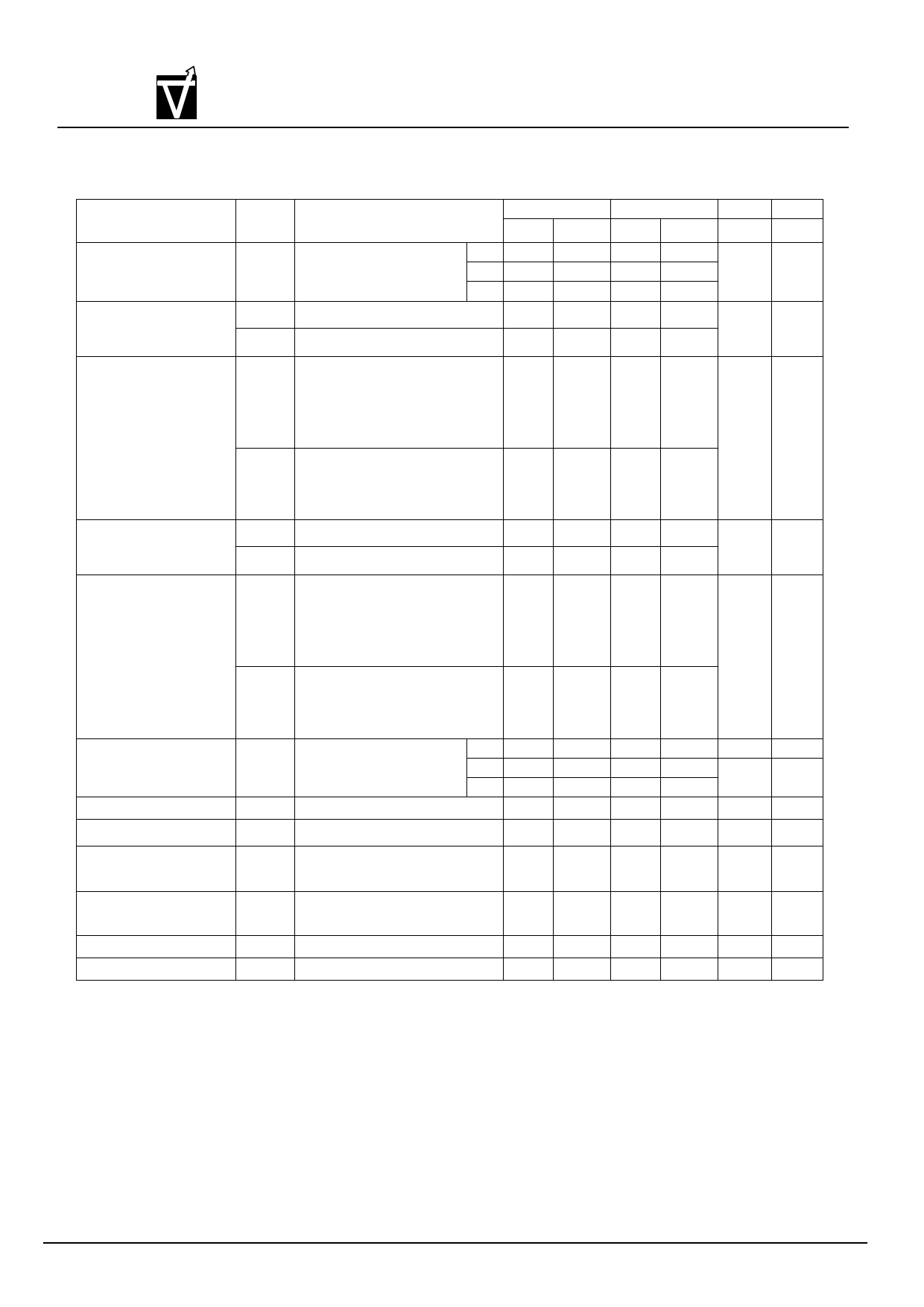

DC Characteristics (Recommended Operating Conditions unless otherwise noted)

Parameter

Symbol

Test Conditions

Operating current

Precharge standby

current in Power

down mode

Precharge standby

current in Nonpower

down mode

Active standby current

in Power

down mode

Active standby

current in Nonpower

down mode

Operating current

(Burst mode)

Refresh current

Self refresh Current

Input Ieakage current

(Inputs)

Intput leakage current

(I/O pins)

Output Low Voltage

Output High Voltage

ICC1

ICC2P

ICC2PS

ICC2N

ICC2NS

ICC3P

ICC3PS

ICC3N

ICC3NS

ICC4

ICC5

ICC6

lLI

lLO

VOL

VOH

Burst length = 1

x4

One bank active

x8

tRC ≥ tRC(MIN.), Io = 0mA x16

CKE ≤ VIL(MAX.) tCK = min.

CKE ≤ VIL(MAX.) tCK = ∞

CKE ≥ VIH(MIN.) tCK = min.

CS ≥ VIH(MIN.)

Input signals are changed one

time during 2 CLK cycles.

CKE ≥ VIH(MIN.) tCK = ∞

CLK ≤ VIL(MAX.)

Input signals are stable.

CKE ≤ VIL(MAX.) tCK = min.

CKE ≤ VIL(MAX.) tCK = ∞

CKE ≥ VIH(MIN.) tCK = min.

CS ≥ VIH(MIN.)

Input signals are changed one

time during 2CLKs

CKE ≥ VIH(MIN.) tCK = ∞

CLK ≤ VIL(MAX.)

Input signals are stable.

tCK ≥ tCK(MIN.) Io = 0mA

All banks Active

tRC = 4 x tRC(MIN)

CKE≤ 0.2V

x4

x8

x16

VIN ≥ 0, VIN ≤ VDD(MAX.)

Pins not under test = 0V

VOUT ≥ 0, VOUT ≤ VDD(MAX.)

DQ# in H - Z., Dout Disabled

IOL = 2mA

IOH = -2mA

-75

Min Max

120

125

135

2

2

20

7

7

5

30

20

115

130

160

190

1

-1 1

-1.5 1.5

0.4

2.4

-8H

Min Max

100

105

115

2

2

20

7

7

5

30

20

105

120

150

190

1

-1 1

-1.5 1.5

0.4

2.4

Unit Notes

mA 1

mA

mA

mA

mA

mA 2

mA 3

mA

uA

uA

V4

V4

Notes : 1. ICC1 depends on output loading and cycle rates. Specified values are obtained with the output open.

In addition to this, ICC1 is measured on condition that addresses are changed only one time during tCK(MIN.).

2. ICC4 depends on output loading and cycle rates. Specified values are obtained with the output open.

In addition to this, ICC4 is measured on condition that addresses are changed only one time during tCK(MIN.).

3. ICC5 is measured on condition that addresses are changed only one time during tCK(MIN.).

4. For LVTTL compatible.

Document : 1G5-0154

Rev.1

Page 5

5 Page

VIS

Preliminary

VG36128401A

VG36128801A

VG36128161A

CMOS Synchronous Dynamic RAM

(2/3)

Current state CS RAS CA WE Address

Command

Action

Notes

Read with auto H X X X X

precharge

L H H HX

DESL

NOP

Continue burst to end → Prcharging

Continue burst to end → Prcharging

L H H LX

BST Illegal for single bank, but legal for

multibanks interleave

L H L H BA, CA, A10 READ/READA Illegal for single bank, but legal for

multibanks interleave

L H L L BA, CA, A10 WRIT/WRITA ILLEGAL

L L H H BA, RA

ACT

ILLEGAL

3

L L H L BA, A10

PRE/PALL

ILLEGAL

3

L L L HX

PEF/SELF

ILLEGAL

L L L L Op - Code MRS

ILLEGAL

Write with auto H X X X X

precharge

L H H HX

L H H LX

DESL

NOP

BST

Continue burst to end → Write

recovering with auto precharge

Continue burst to end → Write

recovering with auto precharge

ILLEGAL

L H L H BA, CA, A10 READ/READA Illegal for single bank, but legal for

multibanks interleave

L H L L BA, CA, A10 WRIT/WRITA Illegal for single bank, but legal for

multibanks interleave

L L H H BA, RA

ACT

ILLEGAL

3

L L H L BA, A10

PRE/PALL

ILLEGAL

3

L L L HX

PEF/SELF

ILLEGAL

L L L L Op - Code MRS

ILLEGAL

precharging

H X X XX

L H H HX

L H H LX

DESL

NOP

BST

Nop → Enter idle after tRP

Nop →Enter idle after tRP

Nop →Enter idle after tRP

L H L H BA, CA, A10 READ/READA ILLEGAL

3

L H L L BA, CA, A10 WRIT/WRITA ILLEGAL

3

L L H H BA, RA

ACT

ILLEGAL

3

L L H L BA, A10

PRE/PALL

Nop → Enter idle after tRP

L L L HX

PEF/SELF

ILLEGAL

L L L L Op - Code MRS

ILLEGAL

Row activating H X X X X

L H H HX

L H H LX

DESL

NOP

BST

Nop → Enter row active idle after tRCD

Nop →Enter row active idle after tRCD

Nop →Enter row active idle after tRCD

L H L H BA, CA, A10 READ/READA ILLEGAL

3

L H L L BA, CA, A10 WRIT/WRITA ILLEGAL

3

L L H H BA, RA

ACT

ILLEGAL

3,9

L L H L BA, A10

PRE/PALL

ILLEGAL

3

L L L HX

PEF/SELF

ILLEGAL

L L L L Op - Code MRS

ILLEGAL

Document : 1G5-0154

Rev.1

Page 11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet VG36128801A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| VG36128801A | CMOS Synchronous Dynamic RAM | Vanguard International Semiconductor |

| VG36128801BT | CMOS Synchronous Dynamic RAM | Vanguard International Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |