|

|

PDF VSP3000Y Data sheet ( Hoja de datos )

| Número de pieza | VSP3000Y | |

| Descripción | 12-Bit/ 6MHz CCD/CIS SIGNAL PROCESSOR | |

| Fabricantes | Burr-Brown Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de VSP3000Y (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

®

VSP3000

VSP3000

TM 12-Bit, 6MHz

CCD/CIS SIGNAL PROCESSOR

FEATURES

q 12-BIT, 6MHZ A/D CONVERTER

q GUARANTEED NO MISSING CODES

q 3 CHANNEL, 2MHz COLOR SCAN MODE:

Correlated Double Samplers

8-Bit Offset Adjustment DACs

0dB to +13dB PGAs

q A/D INPUT MONITOR

q INTERNAL VOLTAGE REFERENCE

q SINGLE +5V SUPPLY

q 3V OR 5V DIGITAL OUTPUT

q LOW POWER: 475mW typ (3-CH Mode)

APPLICATIONS

q CCD AND CIS COLOR SCANNERS

q FAX AND MULTI-FUNCTION MACHINES

q INDUSTRIAL /MEDICAL IMAGING SYSTEMS

DESCRIPTION

The VSP3000 is a complete, three-channel image

signal processor for Charge Coupled Device (CCD)

or Contact Image Sensor (CIS) systems. Each chan-

nel contains sensor signal sampling, Black Level

adjustment and a programmable gain amplifier. The

three inputs are multiplexed into a high speed, 12-bit

analog-to-digital converter. Input circuitry can be

configured, by digital command, for CCD or CIS

sensors. A Black Clamp and Correlated Double

Samplers (CDS) are provided for CCD sensors. For

CIS devices, the VSP3000 provides a single-ended

sampler and a reference input. The VSP3000 is

available in a 48-lead LQFP package and operates

from 0°C to +85°C with a single +5V supply.

CLP

RINP

RINN

Clamp

GINP

GINN

Clamp

BINP

BINN

Clamp

Offset

Register

R

G

B

8 8-Bit

DAC

8 8-Bit

DAC

8 8-Bit

DAC

8

CK1 CK2

CDS

PGA

5

STRT ADCCK TP0

VREF

Timing

M1

M2

M3

Bandgap

Reference

CDS

PGA

5

MUX

CDS

PGA

5

VSP3000

Configuration

Register

Gain

Adjust

Register

R

G

B

5

8

12-Bit

A/D

12

Register

Port

3

8

CM

REFT

REFB

VDRV

B0-B11

(D0-D7, A0-A2)

OE

P/S

WRT

RD

SCLK

SD

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©1998 Burr-Brown Corporation

PDS-1444B

Printed in U.S.A. August, 1999

1 page

TIMING SPECIFICATIONS

Timing Specifications = tMIN to tMAX with +5V power supply.

SYMBOL

Clock Parameters

tCK1AP

tCK1BP

tCK1A

tCK1B

tCK2A

tCK2B

tCCK

tCKP

tS

tCK12A

tCK12B

tCK21A

tCK21B

tCNV

tST

tSET

tADCCK2

tADCCK1

Read/Write Register

tW

tRW

tDA

tWD

tSD

tSCK

tSCKP

tSS

tSW

tPR

tRD

tRH

Data Output

tOES

tOEW

tOER

t3E

tACKD

tOEP

PARAMETER

3-Channel Conversion Rate

1-Channel Conversion Rate

CK1 Pulse Width

CK1 Pulse Width

CK2 Pulse Width

CK2 Pulse Width

ADCCK Pulse Width

ADCCK Period

Sampling Delay

CK1 Falling Edge to CK2 Rising Edge

CK1 Falling Edge to CK2 Rising Edge

CK2 Falling Edge to CK1 Rising Edge

CK2 Falling Edge to CK1 Rising Edge

Conversion Delay

Start Conversion Time

ADCCK Falling Edge to CK1 Rising Edge

ADCCK Falling Edge to CK2 Falling Edge

ADCCK Falling Edge to CK1 Falling Edge

WRT Pulse Width

Address Setup Time

Data Setup Time

Data Valid Time

Data Ready Time

Serial Clock Pulse Width

Serial Clock Period

Serial Ready Time

WRT Pulse Setup Time

Parallel Ready Time

Read Out Delay

Read Out Hold Time

A/D Converter Output Enable Setup Time

OE Pulse Width

Output Enable Time

3-State Enable Time

Data Output Delay

Parallel Port Setup Time

MIN

TYP

MAX

UNITS

300 500

100 166

20 125

20 40

20 125

20 40

40 83

100 166

10

15

15

70

40

40

20 100

10

5

5

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

30 50

20 50

30 50

15 50

30 50

60 100

100 200

50

20

30

20

1

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

20 ns

100 ns

20 40 ns

2 10 ns

12 ns

10 ns

®

5 VSP3000

5 Page

high performance 12-bit A/D converter. The analog MUX is

not cycling between channels in this mode. Instead, the

analog MUX is connected to a specific channel, depending on

the data in the Configuration Register.

As specified in the “1-Channel CIS Mode” timing diagram,

the active period of CK1 (tCK1B) must be in the LOW period

of ADCCK. If it is in the HIGH period of ADCCK, the

VSP3000 will not function properly.

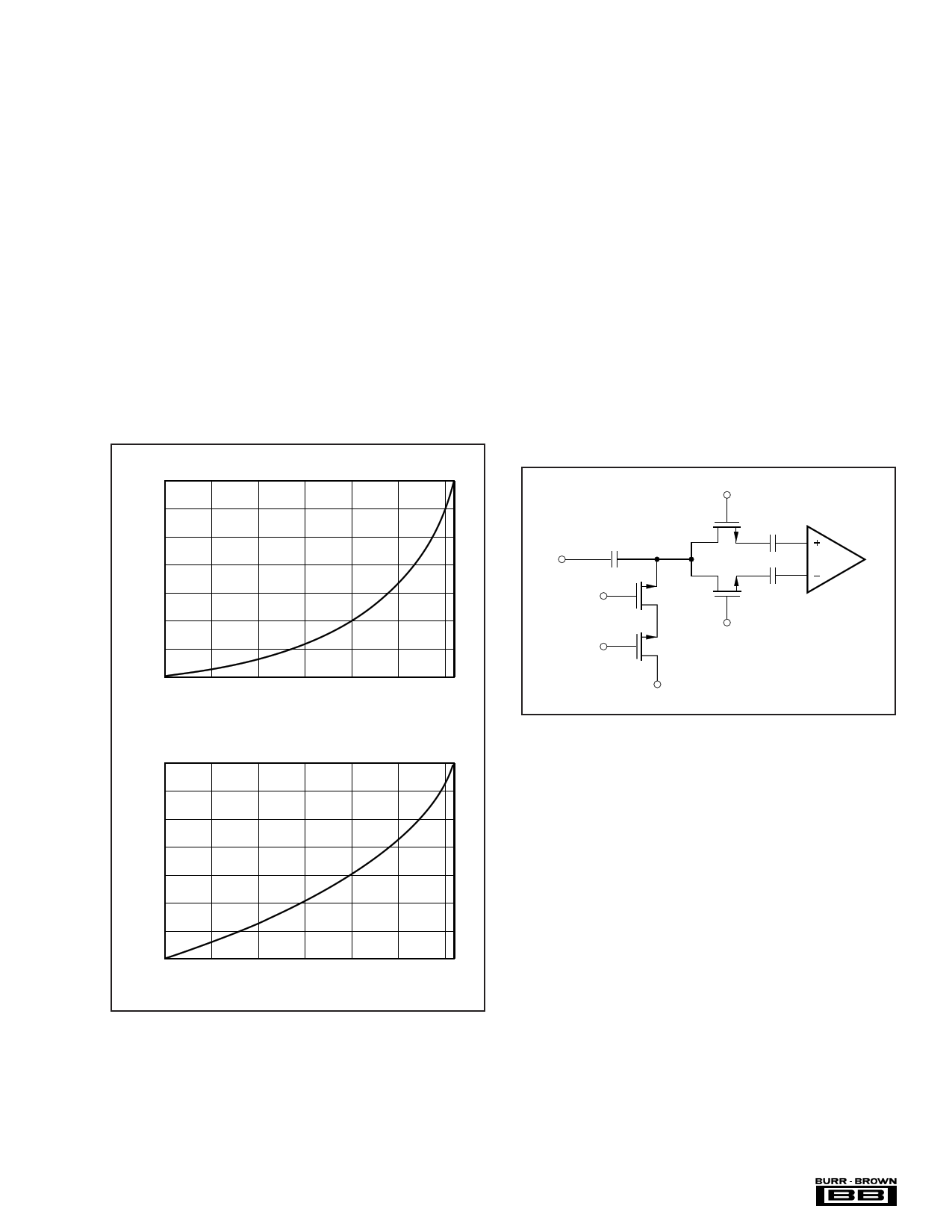

ANALOG PGA

There is one analog PGA on each channel. Each analog PGA

is controlled by a 5-bit PGA gain register. The analog PGA

gain varies from 1 to 4.44 (0dB to +13dB). The transfer

function of the PGA is:

Gain = 4/(4 – 0.1 • X)

where X is the integer representation of the 5-bit PGA gain

register. Figure 1 shows the PGA transfer function plot.

4.5

4.0

3.5

3.0

2.5

2.0

1.5

1.0

0

PGA TRANSFER FUNCTION

5 10 15 20 25

PGA Gain Setting

31

14

12

10

8

6

4

2

0

0

PGA TRANSFER FUNCTION

5 10 15 20 25

PGA Gain Setting

31

FIGURE 1. PGA Transfer Function Plot.

CHOOSING AC INPUT COUPLING CAPACITORS

The purpose of the input coupling capacitor is to isolate the

DC output of the CCD array from affecting the VSP3000. The

internal clamping circuitry restores the necessary DC compo-

nent to the CCD output signal. The internal clamp voltage,

VCLAMP, is derived from the reference. VCLAMP depends on

the value of VREF; if VREF is set to 1V, VCLAMP is 2.5V and

if VREF is set to 1.5V, VCLAMP is 3V. There are many factors

that determine the size of the input coupling capacitors

including CCD signal swing, voltage droop across the input

capacitor since the last clamp interval, leakage current of the

VSP3000 input circuitry, and the time period of CK1. Figure

2 shows a simplified equivalent circuit of the VSP3000

inputs. In this equivalent circuit, the input coupling capacitor,

CIN, and the sampling capacitor, C1, are constructed as a

capacitor divider (during CK1). For AC analysis, op amp

inputs are grounded. Therefore, the sampling voltage, VS

(during CK1) is:

VS = (CIN/CIN + C1)) • VIN

From this equation, we see that a larger value of CIN makes

VS closer to VIN. In other words, the input signal VIN will be

attenuated less if CIN is large. However, there is a disadvan-

tage to using a large value of CIN: the larger the CIN, the more

dummy or optical black pixels must be used to restore the DC

component of the input signal.

CIN

VIN

CLP

VS

CK1

CK1

C1

4pF

CK2

C2

4pF

OP

AMP

VCLAMP

FIGURE 2. Equivalent Circuit of VSP3000 Inputs.

CHOOSING CMAX AND CMIN

As mentioned previously, a large CIN is preferable if there is

enough time for the CLP signal to charge up CIN. Typically,

0.01µF to 0.1µF of CIN can be used for most cases. In order

to optimize CIN, the following two equations can be used to

calculate CMAX and CMIN:

CMAX = ( tCK1 • N)/[RSW • ln (VD/VERROR)]

where, tCK1 is the time when both CK1 and CLP are HIGH

and N is the number of black pixels, RSW is the total switch

resistance, VD is the droop across CIN and VERROR is the

difference between VS and VCLAMP. The nominal value of

RSW is 4kΩ plus the driver’s impedance. 0.1V should be

tolerable for VERROR and still keep the VSP3000 working

properly.

CMIN = ( I/VERROR) • t

where, I is 10nA, the typical leakage current of the VSP3000

input circuitry and t is the time between clamp pulses.

®

11 VSP3000

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet VSP3000Y.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| VSP3000 | 12-Bit/ 6MHz CCD/CIS SIGNAL PROCESSOR | Burr-Brown Corporation |

| VSP3000Y | 12-Bit/ 6MHz CCD/CIS SIGNAL PROCESSOR | Burr-Brown Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |