|

|

PDF VP2450 Data sheet ( Hoja de datos )

| Número de pieza | VP2450 | |

| Descripción | P-Channel Enhancement-Mode Vertical DMOS FETs | |

| Fabricantes | Supertex Inc | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de VP2450 (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

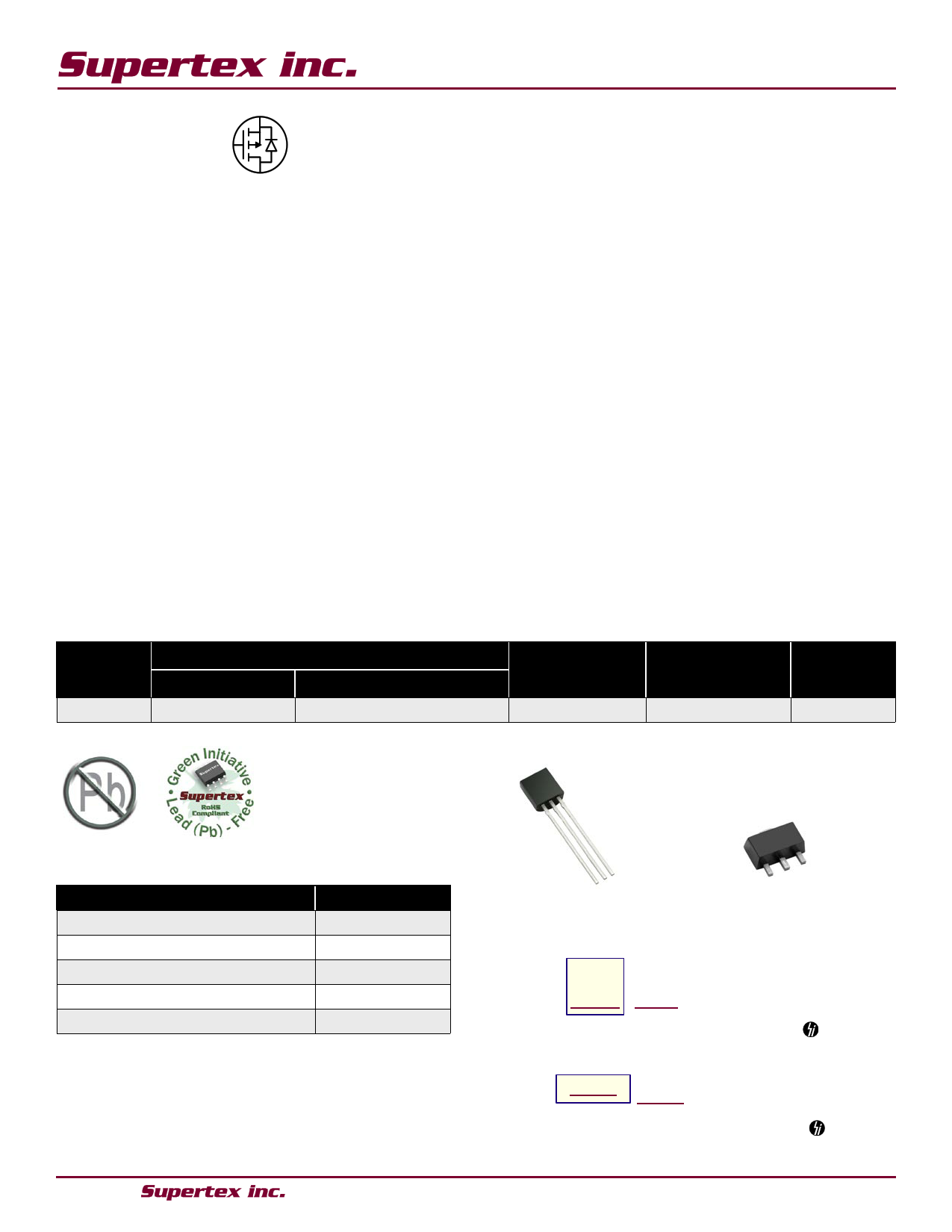

VP2450

P-Channel Enhancement-Mode

Vertical DMOS FET

Features

► Free from secondary breakdown

► Low power drive requirement

► Ease of paralleling

► Low CISS and fast switching speeds

► High input impedance and high gain

► Excellent thermal stability

► Integral source-to-drain diode

Applications

General Description

The Supertex VP2450 is an enhancement-mode (normally-

off) transistor that utilizes a vertical DMOS structure

and Supertex’s well-proven silicon-gate manufacturing

process. This combination produces a device with the

power handling capabilities of bipolar transistors, and the

high input impedance and positive temperature coefficient

inherent in MOS devices. Characteristic of all MOS

structures, this device is free from thermal runaway and

thermally-induced secondary breakdown.

► Motor controls

► Converters

► Amplifiers

► Switches

► Power supply circuits

► Drivers (relays, hammers, solenoids, lamps,

memories, displays, bipolar transistors, etc.)

Supertex’s vertical DMOS FETs are ideally suited to a

wide range of switching and amplifying applications where

very low threshold voltage, high breakdown voltage, high

input impedance, low input capacitance, and fast switching

speeds are desired.

Ordering Information

Device

Package Options

TO-92

TO-243AA (SOT-89)

BVDSS/BVDGS

(V)

VP2450

VP2450N3-G

-G indicates package is RoHS compliant (‘Green’)

VP2450N8-G

-500

Pin Configurations

RDS(ON)

(max)

(Ω)

30

ID(ON)

(min)

(mA)

-200

Absolute Maximum Ratings

Parameter

Value

Drain-to-Source voltage

Drain-to-Gate voltage

Gate-to-Source voltage

BVDSS

BVDGS

±20V

Operating and storage temperature -55OC to +150OC

Soldering temperature*

300OC

Absolute Maximum Ratings are those values beyond which damage to the device

may occur. Functional operation under these conditions is not implied. Continuous

operation of the device at the absolute rating level may affect device reliability. All

voltages are referenced to device ground.

* Distance of 1.6mm from case for 10 seconds.

DRAIN

SOURCE

GATE

TO-92 (N3)

DRAIN

SOURCE

DRAIN

GATE

TO-243AA (SOT-89) (N8)

Product Marking

SiVP YY = Year Sealed

2 4 5 0 WW = Week Sealed

YYWW

= “Green” Packaging

Package may or may not include the following marks: Si or

TO-92 (N3)

VP4EW W = Code for week sealed

= “Green” Packaging

Packages may or may not include the following marks: Si or

TO-243AA (SOT-89) (N8)

● 1235 Bordeaux Drive, Sunnyvale, CA 94089 ● Tel: 408-222-8888 ● www.supertex.com

1 page

3-Lead TO-92 Package Outline (N3)

D

Seating Plane

123

L

A

b

e1

e

Front View

c

Side View

VP2450

E1

1

E

3

2

Bottom View

Symbol

A b c D E E1

Dimensions

(inches)

MIN

NOM

MAX

.170

-

.210

.014†

-

.022†

.014†

-

.022†

.175

-

.205

.125

-

.165

.080

-

.105

JEDEC Registration TO-92.

* This dimension is not specified in the original JEDEC drawing. The value listed is for reference only.

† This dimension is a non-JEDEC dimension.

Drawings not to scale.

Supertex Doc.#: DSPD-3TO92N3, Version D080408.

e

.095

-

.105

e1 L

.045 .500

--

.055 .610*

● 1235 Bordeaux Drive, Sunnyvale, CA 94089 ● Tel: 408-222-8888 ● www.supertex.com

5

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet VP2450.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| VP2450 | P-Channel Enhancement-Mode Vertical DMOS FETs | Supertex Inc |

| VP2450 | P-Channel Enhancement-Mode Vertical DMOS FET | Microchip |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |