|

|

PDF XCR5032 Data sheet ( Hoja de datos )

| Número de pieza | XCR5032 | |

| Descripción | 32 Macrocell CPLD | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XCR5032 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

APPLICATION NOTE

0

R

XCR5032: 32 Macrocell CPLD

DS045 (v1.1) February 10, 2000

0 14* Product Specification

Features

• Industry's first TotalCMOS™ PLD - both CMOS design

and process technologies

• Fast Zero Power (FZP™) design technique provides

ultra-low power and very high speed

• High speed pin-to-pin delays of 6 ns

• Ultra-low static power of less than 75 µA

• 100% routable with 100% utilization while all pins and

all macrocells are fixed

• Deterministic timing model that is extremely simple to

use

• Two clocks with programmable polarity at every

macrocell

• Support for asynchronous clocking

• Innovative XPLA™ architecture combines high speed

with extreme flexibility

• 1000 erase/program cycles guaranteed

• 20 years data retention guaranteed

• Logic expandable to 37 product terms

• PCI compliant

• Advanced 0.5µ E2CMOS process

• Security bit prevents unauthorized access

• Design entry and verification using industry standard

and Xilinx CAE tools

• Reprogrammable using industry standard device

programmers

• Innovative Control Term structure provides either sum

terms or product terms in each logic block for:

- Programmable 3-state buffer

- Asynchronous macrocell register preset/reset

• Programmable global 3-state pin facilitates `bed of

nails' testing without using logic resources

• Available in both PLCC and VQFP packages

• Available in both Commercial and Industrial grades

Description

The XCR5032 CPLD (Complex Programmable Logic

Device) is the first in a family of CoolRunner™ CPLDs from

Xilinx. These devices combine high speed and zero power

in a 32 macrocell CPLD. With the FZP design technique,

the XCR5032 offers true pin-to-pin speeds of 6 ns, while

simultaneously delivering power that is less than 75 µA at

standby without the need for "turbo bits" or other power

down schemes. By replacing conventional sense amplifier

methods for implementing product terms (a technique that

has been used in PLDs since the bipolar era) with a cas-

caded chain of pure CMOS gates, the dynamic power is

also substantially lower than any competing CPLD. These

devices are the first TotalCMOS PLDs, as they use both a

CMOS process technology and the patented full CMOS

FZP design technique. For 3V applications, Xilinx also

offers the high speed XCR3032 CPLD that offers these fea-

tures in a full 3V implementation.

The Xilinx FZP CPLDs utilize the patented XPLA

(eXtended Programmable Logic Array) architecture. The

XPLA architecture combines the best features of both PLA

and PAL type structures to deliver high speed and flexible

logic allocation that results in superior ability to make

design changes with fixed pinouts. The XPLA structure in

each logic block provides a fast 6 ns PAL path with five ded-

icated product terms per output. This PAL path is joined by

an additional PLA structure that deploys a pool of 32 prod-

uct terms to a fully programmable OR array that can allo-

cate the PLA product terms to any output in the logic block.

This combination allows logic to be allocated efficiently

throughout the logic block and supports as many as 37

product terms on an output. The speed with which logic is

allocated from the PLA array to an output is only 2 ns,

regardless of the number of PLA product terms used, which

results in worst case tPD's of only 8 ns from any pin to any

other pin. In addition, logic that is common to multiple out-

puts can be placed on a single PLA product term and

shared across multiple outputs via the OR array, effectively

increasing design density.

The XCR5032 CPLDs are supported by industry standard

CAE tools (Cadence/OrCAD, Exemplar Logic, Mentor, Syn-

opsys, Synario, Viewlogic, and Synplicity), using text

(ABEL, VHDL, Verilog) and/or schematic entry. Design ver-

ification uses industry standard simulators for functional

and timing simulation. Development is supported on per-

sonal computer, Sparc, and HP platforms. Device fitting

uses a Xilinx developed tool, XPLA Professional (available

on the Xilinx web site).

The XCR5032 CPLD is reprogrammable using industry

standard device programmers from vendors such as Data

I/O, BP Microsystems, SMS, and others.

DS045 (v1.1) February 10, 2000

www.xilinx.com

1-800-255-7778

1

1 page

XCR5032: 32 Macrocell CPLD

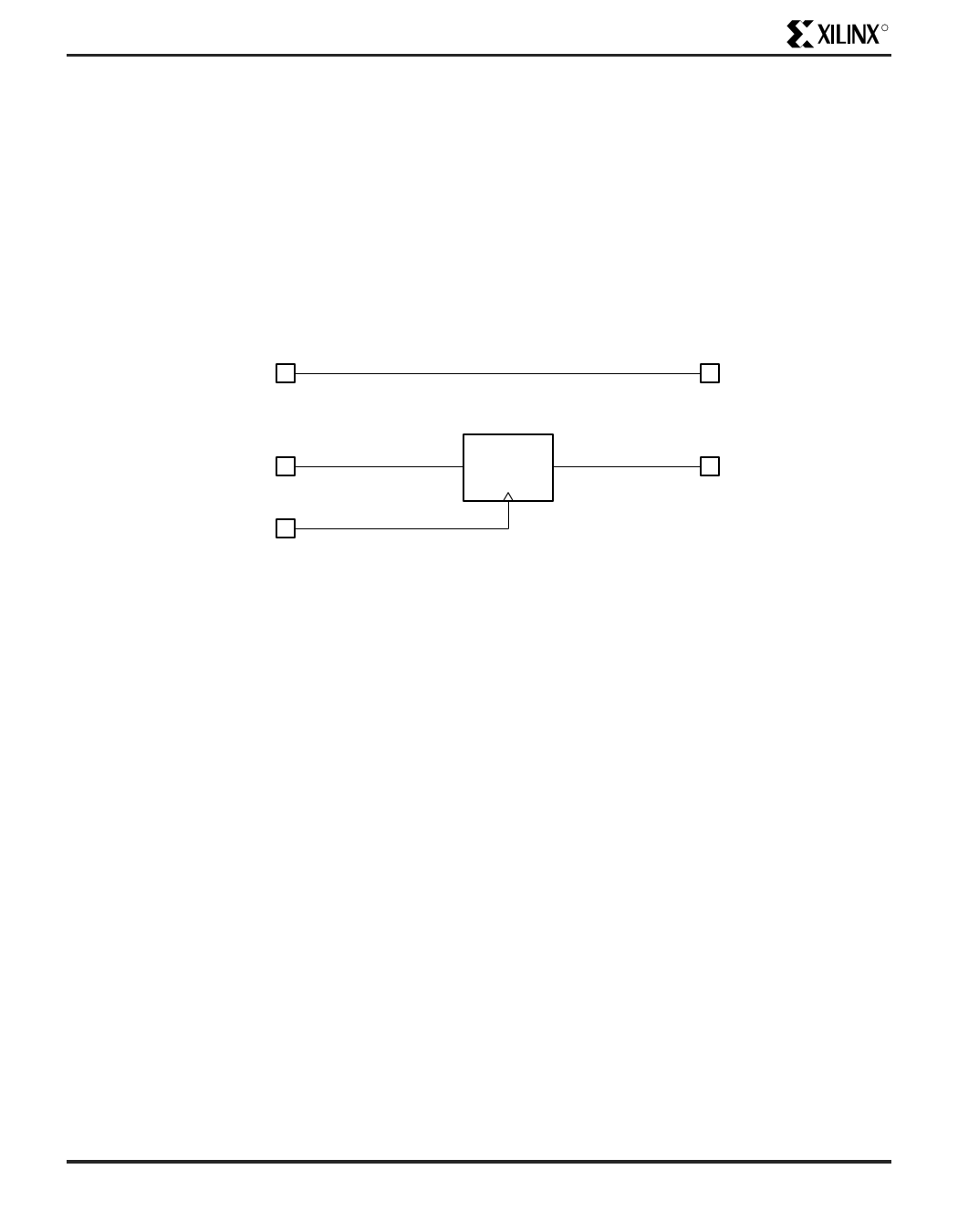

Simple Timing Model

Figure 3 shows the CoolRunner Timing Model. The Cool-

Runner timing model looks very much like a 22V10 timing

model in that there are three main timing parameters,

including tPD, tSU, and tCO. In other architectures, the user

may be able to fit the design into the CPLD, but is not sure

whether system timing requirements can be met until after

the design has been fit into the device. This is because the

timing models of competing architectures are very complex

and include such things as timing dependencies on the

number of parallel expanders borrowed, sharable expand-

R

ers, varying number of X and Y routing channels used, etc.

In the XPLA architecture, the user knows up front whether

the design will meet system timing requirements. This is

due to the simplicity of the timing model. For example, in

the XCR5032 device, the user knows up front that if a given

output uses five product terms or less, the tPD = 6 ns, the

tSU = 4.5 ns, and the tCO = 5 ns. If an output is using six to

37 product terms, an additional 2 ns must be added to the

tPD and tSU timing parameters to account for the time to

propagate through the PLA array.

INPUT PIN

INPUT PIN

tPD_PAL = COMBINATORIAL PAL ONLY

tPD_PLA = COMBINATORIAL PAL + PLA

REGISTERED

tSU_PAL = PAL ONLY

tSU_PLA = PAL + PLA

D

REGISTERED

Q tCO

GLOBAL CLOCK PIN

Figure 3: CoolRunner Timing Model

OUTPUT PIN

OUTPUT PIN

SP00441

5

www.xilinx.com

DS045 (v1.1) February 10, 2000

1-800-255-7778

5 Page

XCR5032: 32 Macrocell CPLD

Switching Characteristics

The test load circuit and load values for the AC Electrical Characteristics are illustrated below.

R

VDD

S1

R1

VIN

VOUT

R2 C1

S2

COMPONENT

R1

R2

C1

VALUES

470Ω

250Ω

35 pF

MEASUREMENT

S1

S2

tPZH

tPZL

tP

Open

Closed

Closed

Closed

Closed

Closed

NOTE: For tPHZ and tPLZ C = 5pF, and 3-State levels are

measured 0.5V from steady state active level.

SP00476

ns VCC = 5V, 25°C

6.60

6.20

5.80

5.40

TYPICAL

Voltage Waveform

+3.0V

90%

0V

1.5ns

tR tF

MEASUREMENTS:

All circuit delays are measured at the +1.5V level of

inputs and outputs, unless otherwise specified.

Input Pulses

10%

1.5ns

SP00368

5.00

4.60

12

4

8

12

Figure 5: tPD_PAL vs Outputs Switching

16

SP00448A

Table 2: tPD_PAL vs # of Outputs switching (VCC = 5V)

# of Outputs 1 2 4 8 12 16

Typical (ns) 5.1 5.2 5.5 5.9 6.1 6.3

11

www.xilinx.com

DS045 (v1.1) February 10, 2000

1-800-255-7778

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet XCR5032.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XCR5032 | 32 Macrocell CPLD | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |