|

|

PDF XCR3384XL Data sheet ( Hoja de datos )

| Número de pieza | XCR3384XL | |

| Descripción | 384 Macrocell CPLD | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XCR3384XL (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

0

R XCR3384XL: 384 Macrocell CPLD

DS024 (v1.3) August 10, 2001

0 14 Advance Product Specification

Features

• Lowest power 384 macrocell CPLD

• 7.5 ns pin-to-pin logic delays

• System frequencies up to 127 MHz

• 384 macrocells with 9,600 usable gates

• Available in small footprint packages

- 144-pin TQFP (118 user I/O)

- 208-pin PQFP (172 user I/O)

- 256-ball FBGA (212 user I/O)

- 324-ball FBGA (220 user I/O)

• Optimized for 3.3V systems

- Ultra low power operation

- 5V tolerant I/O pins with 3.3V core supply

- Advanced 0.35 micron five layer metal EEPROM

process

- FZP™ CMOS design technology

• Advanced system features

- In-system programming

- Input registers

- Predictable timing model

- Up to 23 clocks available per function block

- Excellent pin retention during design changes

- Full IEEE Standard 1149.1 boundary-scan (JTAG)

- Four global clocks

- Eight product term control terms per function block

• Fast ISP programming times

• Port Enable pin for additional I/O

• 2.7V to 3.6V supply voltage at industrial grade voltage

range

• Programmable slew rate control per output

• Security bit prevents unauthorized access

• Refer to XPLA3 family data sheet (DS012) for

architecture description

Description

The XCR3384XL is a 3.3V, 384 macrocell CPLD targeted at

power sensitive designs that require leading edge program-

mable logic solutions. A total of 24 function blocks provide

9,600 usable gates. Pin-to-pin propagation delays are

7.5 ns with a maximum system frequency of 127 MHz.

TotalCMOS™ Design Technique for

Fast Zero Power

Xilinx offers a TotalCMOS CPLD, both in process technol-

ogy and design technique. Xilinx employs a cascade of

CMOS gates to implement its sum of products instead of

the traditional sense amp approach. This CMOS gate imple-

mentation allows Xilinx to offer CPLDs that are both high

performance and low power, breaking the paradigm that to

have low power, you must have low performance. Refer to

Figure 1 and Table 1 showing the ICC vs. Frequency of our

XCR3384XL TotalCMOS CPLD (data taken with 24

up/down, loadable 16-bit counters at 3.3V, 25°C).

140

120

100

80

60

40

20

0

0

20 40 60 80 100 120 140 160

Frequency (MHz)

DS024_01_112700

Figure 1: XCR3384XL Typical ICC vs. Frequency at

VCC = 3.3V, 25°C

Table 1: Typical ICC vs. Frequency at VCC = 3.3V, 25°C

Frequency (MHz)

0

1 10 20 40 60 80 100 120 140

Typical ICC (mA)

TBD TBD TBD TBD TBD TBD TBD TBD TBD TBD

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

DS024 (v1.3) August 10, 2001

Advance Product Specification

www.xilinx.com

1-800-255-7778

1

1 page

R

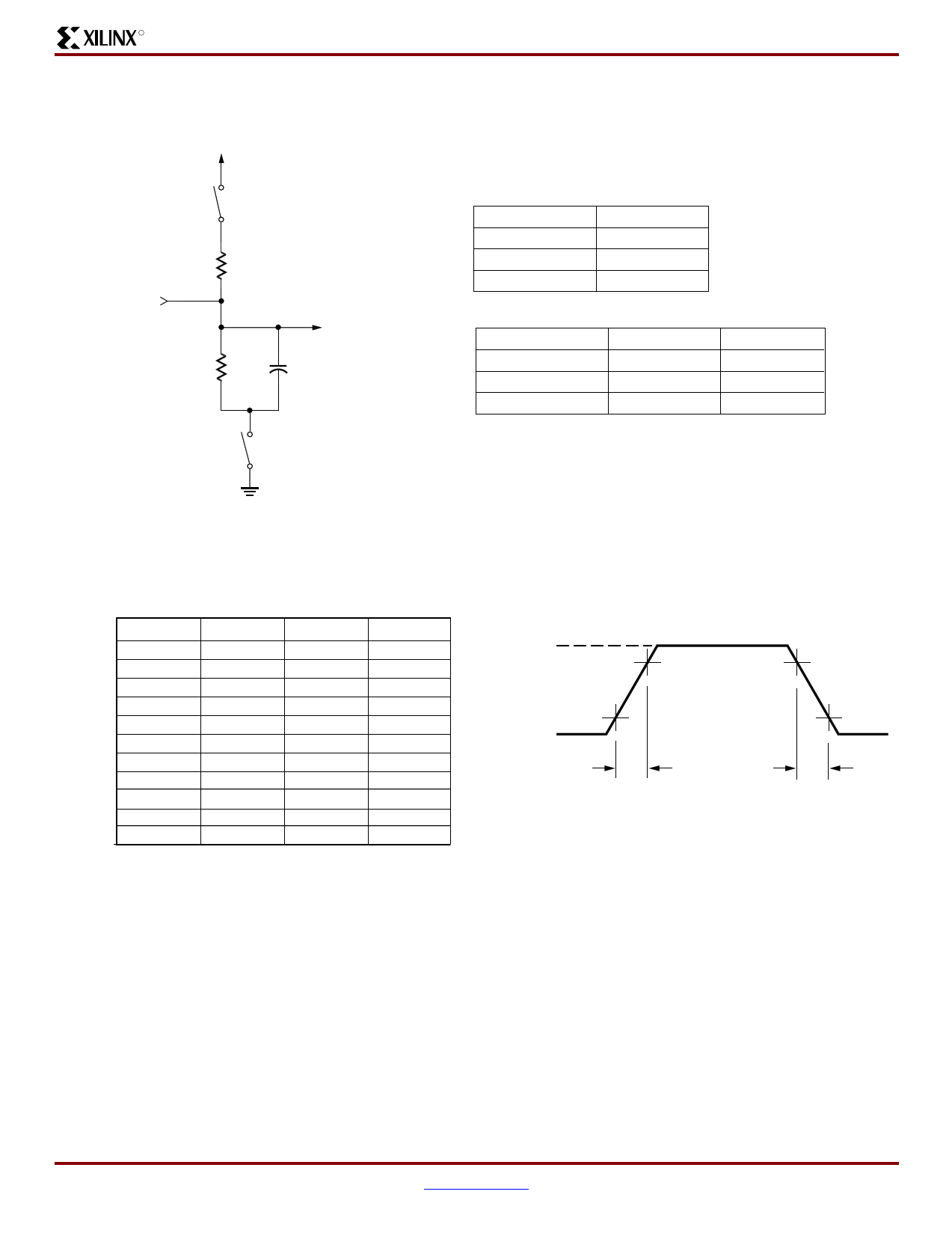

Switching Characteristics

VCC

S1

R1

VIN

R2

VOUT

C1

S2

XCR3384XL: 384 Macrocell CPLD

Component

R1

R2

C1

Values

390Ω

390Ω

35 pF

Measurement

S1

TPOE (High)

TPOE (Low)

TP

Open

Closed

Closed

Note: For TPOD, C1 = 5 pF

S2

Closed

Open

Closed

Figure 3: AC Load Circuit

DS013_03_050200

7.5

7.4

7.3

7.2

7.1

7.0

6.9

6.8

6.7

6.6

6.5

6.4

6.3

1 2 4 8 16

Number of Adjacent Outputs Switching

DS024_04_11800

Figure 4: Derating Curve for TPD2

+3.0V

90%

10%

0V

TR

1.5 ns

TL

1.5 ns

Measurements:

All circuit delays are measured at the +1.5V level of

inputs and outputs, unless otherwise specified.

DS017_05_042800

Figure 5: Voltage Waveform

DS024 (v1.3) August 10, 2001

Advance Product Specification

www.xilinx.com

1-800-255-7778

5

5 Page

R XCR3384XL: 384 Macrocell CPLD

Table 4: XCR3384XL Global, JTAG, Port Enable, Power, and No Connect Pins

Pin Type

TQ144

PQ208

FT256

FG324

IN0 / CLK0

128

181

B9

C12

IN1 / CLK1

127

182

A8

B12

IN2 / CLK2

126

183

C9

D12

IN3 / CLK3

125

184

B10

A12

TCK

86

30 J13 P20

TDI 131

176

A7

D11

TDO

121

189

C10

B14

TMS

PORT_EN

22

33

127

116(1)

K1

N1(1)

N2

T4(1)

VCC 24, 50, 51, 58, 73, 76, 95, 5, 23, 41, 63, 74, 83, 85, E8, E9, F7, F8, F9, F10, A11, A13, D8, D15, H4,

115, 123, 130, 144

107, 125,143, 165, 179, G6, G11, H5, H6, H11, H19, J10, J11, J12, J13,

186, 191

J6, J11, J12, K6, K11, L7, K9, K14, L9, L14, M1,

L8, L9, L10, M8, M9 M9, M14, N9, N14, N20,

P10, P11, P12, P13, R4,

R19, W8, W15, Y12,

AB10

GND

3, 13, 17, 52, 57, 59, 64,

85, 105, 124, 129, 135,

14, 32, 50, 72, 75, 82, 94,

134, 152, 174, 180, 185,

200

E5, F6, F11, G7, G8, G9,

G10, H7, H8, H9, H10,

J7, J8, J9, J10, K7, K8,

K9, K10, L6, L11

D4, D5, D18, D19, E4,

E19, J9, J14, K10, K11,

K12, K13, L10, L11, L12,

L13, M10, M11, M12,

M13, N10, N11, N12,

N13, P9, P14, V4, V19,

W4, W5, W18, W19

No

Connects

108, 109

1, 2, 52, 53, 54, 105, 157,

208

- A1, A2, A3, A6, A14, A21,

A22, B1, B3, B13, B22,

C1, C3, C20, C21, D20,

D21, F1, G1, G20, H22,

J1, J20, K20, L1, L22,

M21, P21, T1, U1, V1,

Y1, Y17, AA1, AA22,

AB1, AB2, AB19, AB20,

AB21, AB22

Notes:

1. Port Enable is brought High to enable JTAG pins when JTAG pins are used as I/O. See family data sheet for full explanation.

DS024 (v1.3) August 10, 2001

Advance Product Specification

www.xilinx.com

1-800-255-7778

11

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet XCR3384XL.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XCR3384XL | 384 Macrocell CPLD | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |