|

|

PDF XC95288 Data sheet ( Hoja de datos )

| Número de pieza | XC95288 | |

| Descripción | XC95288XL High Performance CPLD | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XC95288 (archivo pdf) en la parte inferior de esta página. Total 11 Páginas | ||

|

No Preview Available !

0

® XC95288 In-System Programmable

CPLD

September 15, 1999 (Version 4.0)

0 5* Product Specification

Features

• 10 ns pin-to-pin logic delays on all pins

• fCNT to 95 MHz

• 288 macrocells with 6,400 usable gates

• Up to 192 user I/O pins

• 5 V in-system programmable

- Endurance of 10,000 program/erase cycles

- Program/erase over full commercial voltage and

temperature range

• Enhanced pin-locking architecture

• Flexible 36V18 Function Block

- 90 product terms drive any or all of 18 macrocells

within Function Block

- Global and product term clocks, output enables, set

and reset signals

• Extensive IEEE Std 1149.1 boundary-scan (JTAG)

support

• Programmable power reduction mode in each

macrocell

• Slew rate control on individual outputs

• User programmable ground pin capability

• Extended pattern security features for design protection

• High-drive 24 mA outputs

• 3.3 V or 5 V I/O capability

• Advanced CMOS 5V FastFLASH technology

• Supports parallel programming of more than one

XC9500 concurrently

• Available in 352-pin BGA and 208-pin HQFP packages

Description

The XC95288 is a high-performance CPLD providing

advanced in-system programming and test capabilities for

general purpose logic integration. It is comprised of sixteen

36V18 Function Blocks, providing 6,400 usable gates with

propagation delays of 10 ns. See Figure 2 for the architec-

ture overview.

Power Management

Power dissipation can be reduced in the XC95288 by con-

figuring macrocells to standard or low-power modes of

operation. Unused macrocells are turned off to minimize

power dissipation.

Operating current for each design can be approximated for

specific operating conditions using the following equation:

ICC (mA) =

MCHP (1.7) + MCLP (0.9) + MC (0.006 mA/MHz) f

Where:

MCHP = Macrocells in high-performance mode

MCLP = Macrocells in low-power mode

MC = Total number of macrocells used

f = Clock frequency (MHz)

Figure 1 shows a typical calculation for the XC95288

device.

900

600

(500)

300

High Performance

Low Power

(700)

(500)

0 50 100

Clock Frequency (MHz)

X7131

Figure 1: Typical ICC vs. Frequency For XC95288

September 15, 1999 (Version 4.0)

1

1 page

R

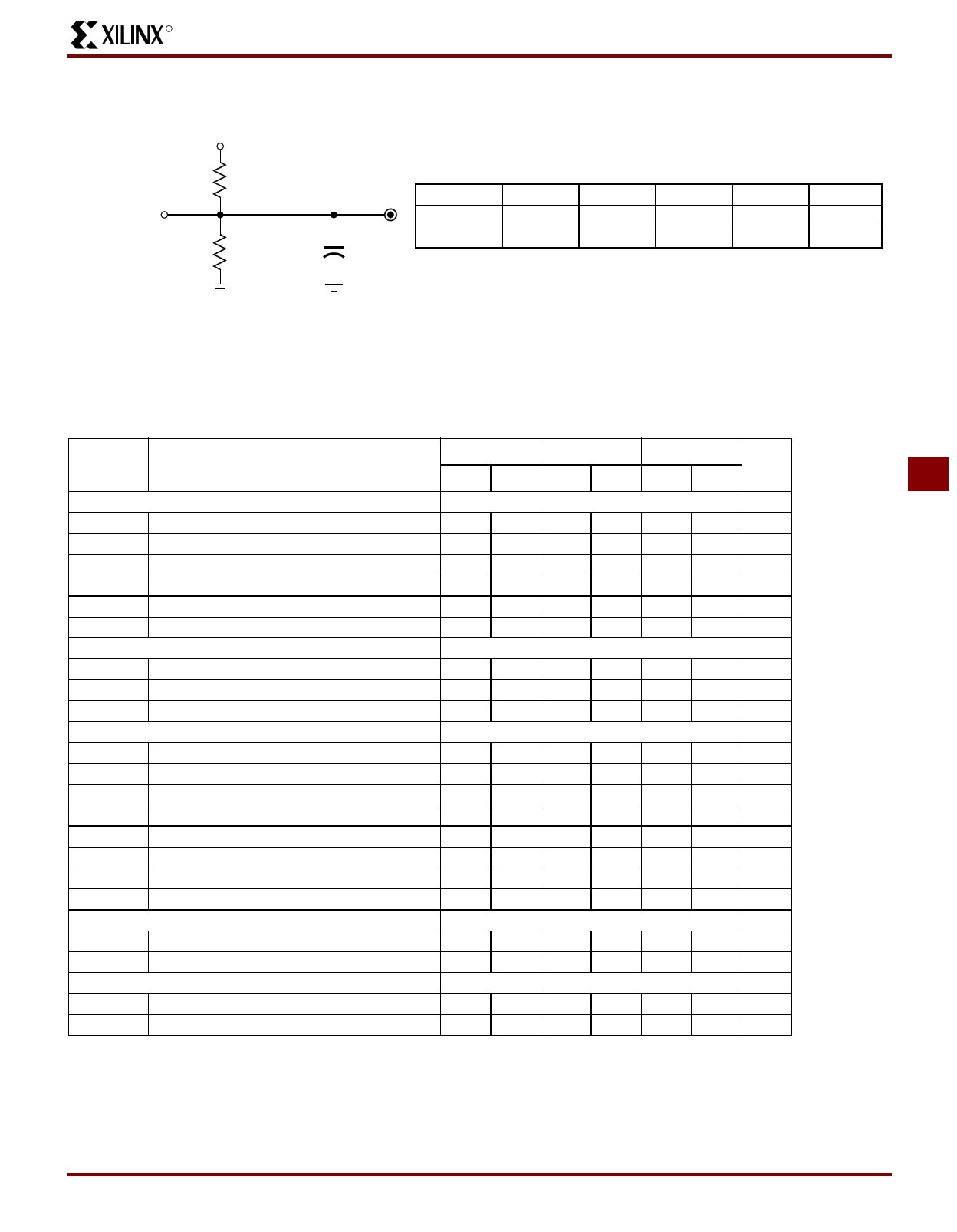

Device Output

VTEST

R1

R2

XC95288 In-System Programmable CPLD

Output Type

VCCIO

5.0 V

VTEST

5.0 V

R1

160 Ω

R2

120 Ω

CL

35 pF

3.3 V

3.3 V

260 Ω

360 Ω

35 pF

CL X5906

Figure 3: AC Load Circuit

Internal Timing Parameters

Symbol

Parameter

XC95288-10 XC95288-15 XC95288-20

Units

Min Max Min Max Min Max

Buffer Delays

tIN Input buffer delay

tGCK

GCK buffer delay

tGSR

GSR buffer delay

tGTS

GTS buffer delay

tOUT

Output buffer delay

tEN Output buffer enable/disable delay

Product Term Control Delays

3.5 4.5 6.5

2.5 3.0 3.0

6.0 7.5 9.5

6.0 11.0 16.0

3.0 4.5 6.5

0.0 0.0 0.0

tPTCK

Product term clock delay

tPTSR

Product term set/reset delay

tPTTS

Product term 3-state delay

Internal Register and Combinatorial delays

3.0 2.5 2.5

2.5 3.0 3.0

3.5 5.0 5.0

tPDI Combinatorial logic propagation delay

tSUI Register setup time

tHI Register hold time

tCOI Register clock to output valid time

tAOI Register async. S/R to output delay

tRAI Register async. S/R recovery before clock

tLOGI

Internal logic delay

tLOGILP Internal low power logic delay

Feedback Delays

2.5

3.5

10.0

1.0

0.5

7.0

2.5

11.0

3.5

4.5

10.0

3.0

0.5

8.0

3.0

11.5

3.5

6.5

10.0

4.0

0.5

8.0

3.0

11.5

tF FastCONNECT matrix feedback delay

tLF Function Block local feeback delay

Time Adders

9.5 11.0 13.0

3.5 3.5 5.0

tPTA3

Incremental Product Term Allocator delay

1.0

1.0

1.5

tSLEW

Slew-rate limited delay

4.5 5.0 5.5

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Note: 3. tPTA is multiplied by the span of the function as defined in the family data sheet.

5

September 15, 1999 (Version 4.0)

5

5 Page

R

XC95288 In-System Programmable CPLD

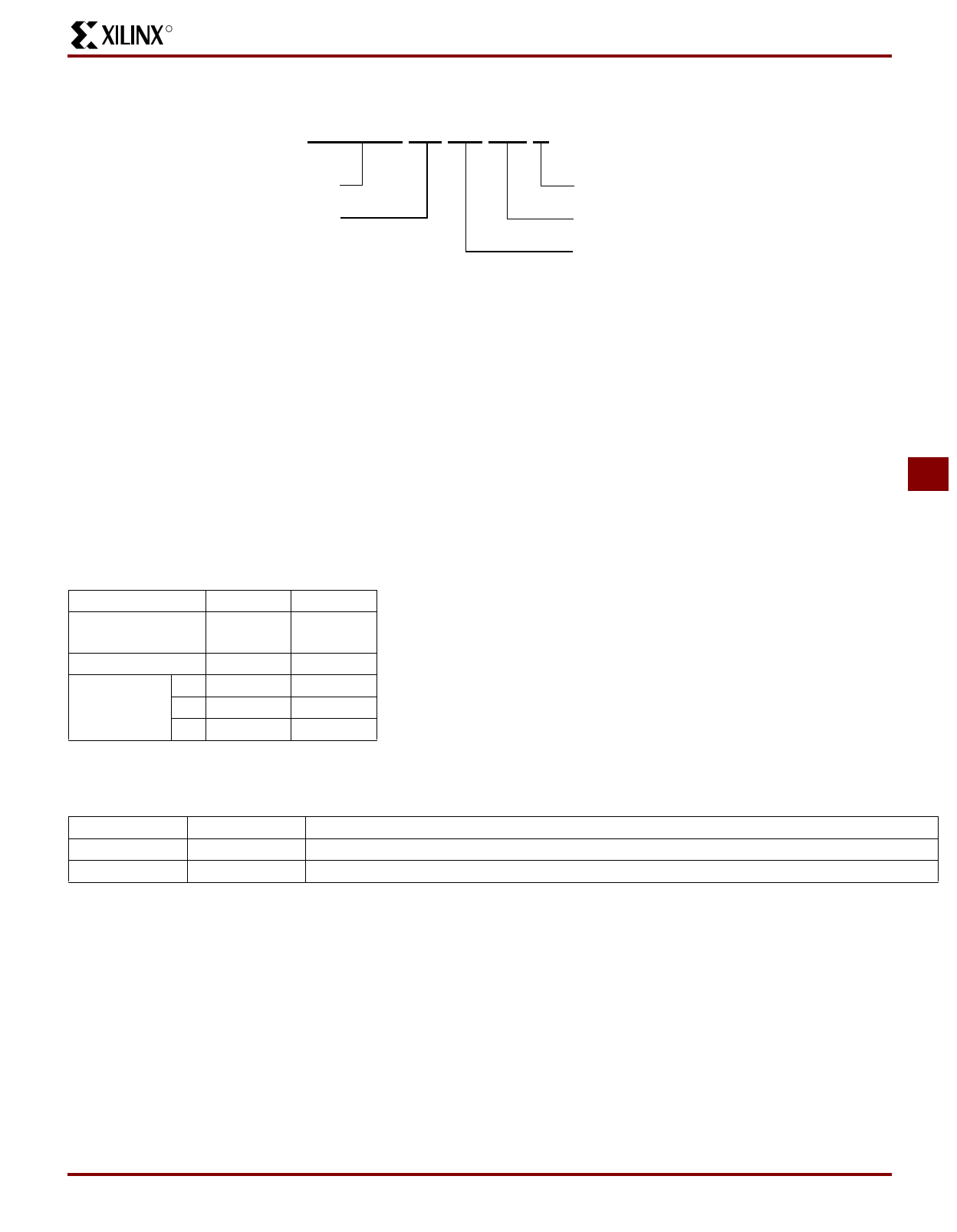

Ordering Information

XC95288 -10 HQ 208 C

Device Type

Speed

Temperature Range

Number of Pins

Package Type

Speed Options

- 20 20 ns pin-to-pin delay

-15 15 ns pin-to-pin delay

-10 10 ns pin-to-pin delay

Packaging Options

HQ208 208-Pin Heat Sink Quad Flat Pack (HQFP)

BG352 352-Pin Plastic Ball Grid Array (BGA)

Temperature Options

C Commercial 0°C to +70°C

I Industrial –40°C to +85°C

5

Component Availability

Pins

Type

Code

XC95288

208

Plastic

HQFP

HQ

–20 C(I)

–15 C(I)

–10 C

352

Plastic

BGA

BG

C(I)

C(I)

C

C = Commercial = 0° to +70°C I = Industrial = –40° to +85°C

Revision Control

Version

3.0

4.0

Date

12/4/98

9/15/99

Revision

Update AC Characteristics and Internal Parameters

Add -10 speed grade

September 15, 1999 (Version 4.0)

11

11 Page | ||

| Páginas | Total 11 Páginas | |

| PDF Descargar | [ Datasheet XC95288.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XC95288 | XC95288 In-System Programmable CPLD | Xilinx |

| XC95288 | XC95288XL High Performance CPLD | Xilinx |

| XC95288-20HQ208C | XC95288XL High Performance CPLD | Xilinx |

| XC95288XL | High Performance CPLD | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |