|

|

PDF XRD98L63 Data sheet ( Hoja de datos )

| Número de pieza | XRD98L63 | |

| Descripción | CCD Image Digitizers with CDS/ PGA and 12-Bit A/D | |

| Fabricantes | Exar Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XRD98L63 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

FEATURES

• 12-bit Resolution ADC, 30MHz Sampling Rate

• 10-bit Programmable Gain: 6dB to 36dB PGA

• Pixel-by-pixel gain switching

• Digitally Controlled Black Level Calibration with

Pixel Averager and Hot Pixel Clipper

• DNS Filter Removes Black Level Digital Noise

• Programmable Black Level, up to code 255

• Black Level Calibration Range: 300 mV

• Programmable Aperture Delays

1.0 ns/step for SBLK & SPIX

0.5 ns/step for ADCLK

• Manual Control of Offset DACs via Serial Port

for use with High-speed Scanners

• Single 2.7V to 3.6V Power Supply

• Optimize power with external resistor to 100mW

• Low Power for Battery Operation

• 100µA Stand-by Mode Current

XRD98L63

CCD Image Digitizers with

CDS, PGA and 12-Bit A/D

June 2003

• Three-state Digital Outputs

• 3,000V ESD Protection

• 48-pin TQFP Package

APPLICATIONS

• Mega pixel Digital Still Cameras

• Digital Camcorders

• 3 CCD Professional/Broadcast Camera

• Line Scan Cameras

• PC Video Cameras

• CCTV/Security Cameras

• Industrial/Medical Cameras

• 2D Bar Code Readers

• High Speed Scanners

• Digital Copiers

GENERAL DESCRIPTION

The XRD98L63 is a complete, low power CCD Image

Digitizer for digital motion and still cameras. The

product includes a high bandwidth differential Corre-

lated Double Sampler (CDS), 10-bit Programmable

Gain Amplifier (PGA) with pixel rate gain switching, 12-

bit Analog-to-Digital Converter (ADC) and improved

digitally controlled black level auto-calibration circuitry

with programmable pixel averaging, hot pixel clipping,

and a Digital Noise Suppression (DNS) filter.

The Correlated Double Sampler (CDS) subtracts the

CCD output signal black level from the video level.

Common mode and power supply noise are rejected by

the differential CDS input stage.

The PGA is digitally controlled with 10-bit resolution on

a dB scale, resulting in a gain range of 6dB to 36dB with

0.047dB per LSB of the gain code. The PGA can be

programmed to switch gain every pixel, in a user

defined pattern of up to 4 different gains. Our propri-

etary control logic allows a camera system to set the

desired gain ratios for color balance. The system gain

can then be changed by writing to a single register,

and the color balance will be maintained.

The black level auto-calibration circuit averages the

results of the Optical Black pixels to compensate for

any internal offset of the XRD98L63 as well as black

level offset from the CCD. The calibration logic uses

proprietary digital filters to eliminate line-to-line offset

noise and noise due to hot pixels in the Optical Black

areas.

The PGA and black level auto-calibration are con-

trolled through a simple 3-wire serial interface. The

timing circuitry is designed to enable users to select a

wide variety of available CCD and image sensors for

their applications. Readback of the serial data regis-

ters is available from the digital output bus.

The XRD98L63 is packaged in 48-lead TQFP to reduce

space and weight, and is suitable for hand-held and

portable applications.

ORDERING INFORMATION

Part No.

XRD98L63AIV

Package Temperature Range

48-Pin TQFP

-40°C to 85°C

Operating

Power Supply

2.7V to 3.6V

Maximum

Sampling Rate

30 MSPS

Rev.1.01

EXAR Corporation, 48720 Kato Road, Fremont, CA 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

XRD98L63

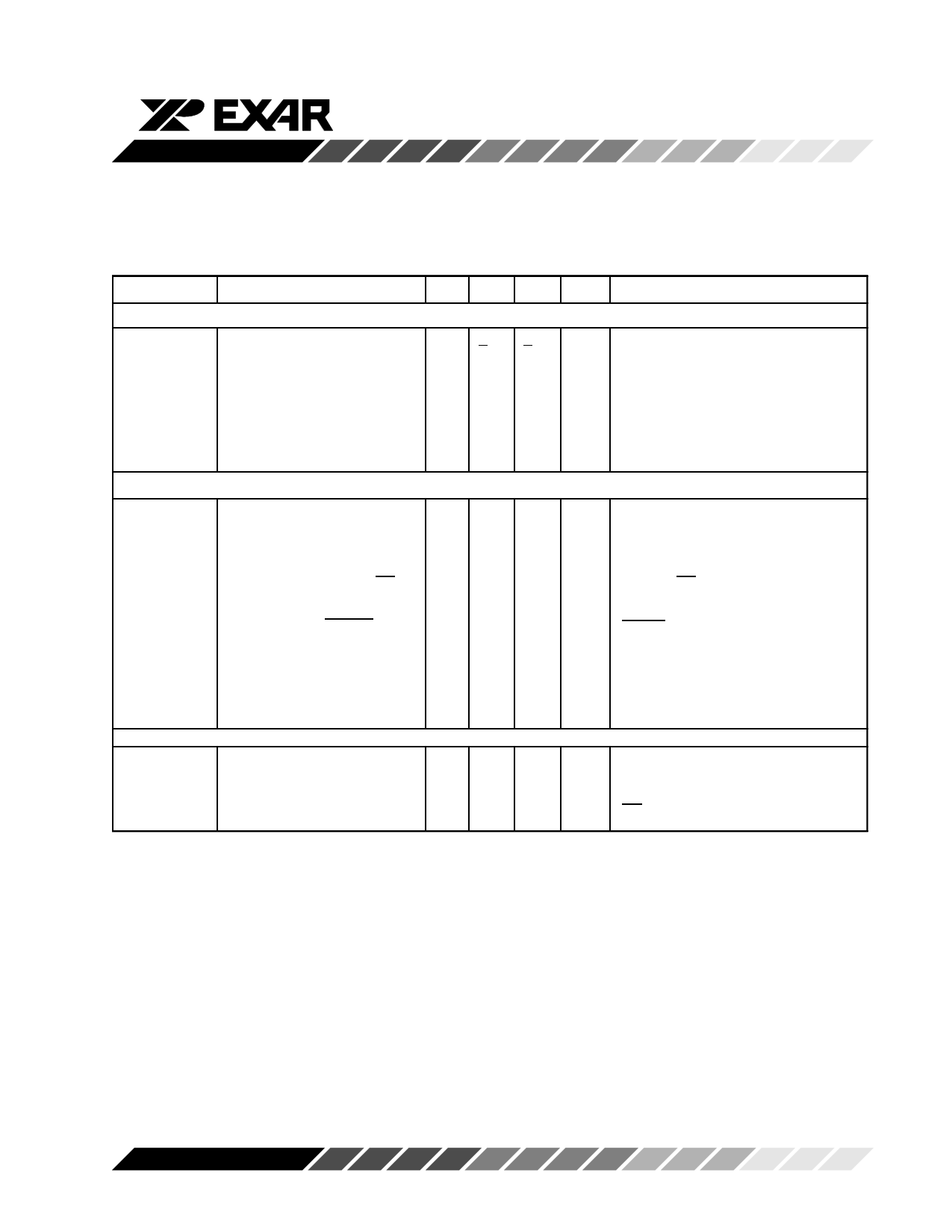

DC ELECTRICAL CHARACTERISTICS – XRD98L63 (cont'd)

Unless otherwise specified: OVDD = DVDD =AVDD = 3.0V, Pixel Rate = 30MSPS, TA = 25°C

Rext = 18.2 KΩ

Symbol Parameter

Min. Typ. Max. Unit Conditions

System Specifications

DNLS

fsmax

fsmin

en MAXAV

en MINAV

Latency

System DNL

Maximum Sample Rate

Minimum Sample Rate

Input ref. Noise, max.Gain

Input ref. Noise, min.Gain

Pipeline Delay

+0.6 +1.0 LSB No missing codes, monotonic

30 MSPS

500 KSPS Not tested

180 µVrms Gain Code = 640 (36db)

400 µVrms Gain Code = 0 (6dB)

7.5 cycles

Digital Inputs (Digital Input Thresholds are Set by DVDD)

VIH

Digital Input High Voltage

VDD-0.5

VIL Digital Input Low Voltage

GND+0.5

IL DC Leakage Current

0.05 ±1.0

IL

Input Leakage, PD and OE

-5

100

V

V

µA

µA

VIN between GND and VDD.

PD and OE have internal pull-down

resisters

IL Input Leakage, RESET

-100

5 µA RESET has an internal pull-up

resister

IL Input Leakage, All Other -100

Digital Inputs

100 nA Input = VDD or GND

CIN Input Capacitance

Digital Outputs

5 pF

VOH

VOL

IOZ

Digital Output High Voltage

Digital Output Low Voltage

High–Z Leakage

OVDD-0.5

0.05

0.5

±1.0

V

V

µA

While sourcing 2mA

While sinking 2mA

OE = 1 or PD = 1 or OE bit = 0

Rev.1.01

5

5 Page

XRD98L63

Wait A, Wait B and OB Lines Registers

WaitA

default

WaitB

default

OB Lines

default

D9

WL[11]

0

0

0

D8

WL[10]

0

0

0

D7

WL[9]

0

0

OBL[7]

1

D6

WL[8]

0

0

OBL[6]

0

D5

WL[7]

0

0

OBL[5]

0

D4

WL[6]

0

0

OBL[4]

0

D3

WL[5]

0

0

OBL[3]

0

D2

WL[4]

0

0

OBL[2]

0

D1

WL[3]

0

WL[1]

0

OBL[1]

1

D0

WL[2]

0

WL[0]

1

OBL[0]

0

WL[11:0] and OBL[7:0] are used by the Black Level Calibration logic in the Frame mode to determine which

lines to use for Calibration. (Frame mode is not currently supported)

See the “Black Level Offset Calibration” section (pg. 19) for more information.

CDAC Even and CDAC Odd Registers

CDAC Even

default

CDAC Odd

default

D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

CDE[8] CDE[7] CDE[6] CDE[5] CDE[4] CDE[3] CDE[2] CDE[1] CDE[0]

0000000000

CDO[8] CDO[7] CDO[6] CDO[5] CDO[4] CDO[3] CDO[2] CDO[1] CDO[0]

0000000000

CDE[8:0] and CDO[8:0] are used to program the internal Coarse Offset DAC in the Manual Calibration

mode. In the normal, single gain mode the value in CDE[8:0] is used. In the Multiple Gain mode, CDE[8:0] is

used for Even lines and CDO[8:0] is used for Odd lines.

See the “Black Level Offset Calibration” section (pg. 19) for more information.

FDAC Even and FDAC Odd Registers

FDAC Even

default

FDAC Odd

default

D9

FDE[9]

0

FDO[9]

0

D8

FDE[8]

0

FDO[8]

0

D7

FDE[7]

0

FDO[7]

0

D6

FDE[6]

0

FDO[6]

0

D5

FDE[5]

0

FDO[5]

0

D4

FDE[4]

0

FDO[4]

0

D3

FDE[3]

0

FDO[3]

0

D2

FDE[2]

0

FDO[2]

0

D1

FDE[1]

0

FDO[1]

0

D0

FDE[0]

0

FDO[0]

0

FDE[9:0] and FDO[9:0] are used to program the internal Fine Offset DAC in the Manual Calibration mode. In

the normal, single gain mode the value in FDE[9:0] is used. In the Multiple Gain mode, FDE[9:0] is used for

Even lines and FDO[9:0] is used for Odd lines.

See the “Black Level Offset Calibration” section (pg. 19) for more information.

Control Register

Control

default

D9

ADCpd

0

D8

AFEpd

0

D7

CHIPpd

0

D6 D5 D4 D3 D2 D1 D0

OE MultGain MGsel[1] MGsel[0] MGstart MinClip OneV

1000010

The Control register is used to program various options.

ADCpd, power down the ADC block. 0=normal operation. 1=ADC power down.

AFEpd, power down the AFE block. 0=normal operation. 1=AFE power down.

OE, output enable control. 0=DB[11:0] in high Z mode. 1=DB[11:0] in active drive mode.

MultGain, enable the Multiple Gain mode. 0=single gain mode. 1= Multiple Gain mode.

MGsel[1:0], Multiple Gain timing mode select.

MGstart, Even or Odd starting condition for MGsel[1:0]=11. 0=start with Even line, 1=start with Odd line.

MinClip, minimum clip option. 0=minimum clip disabled, 1=minimum clip enabled.

OneV, 1 volt input range option. 0=0.8V maximum input range. 1=1.0V maximum input range.

See the “Chip Power Down” section (pg. 34) for information about ADCpd, AFEpd, CHIPpd and OE.

See the “Multiple Gain Mode” section (pg. 30) for information about MultGain, MGsel[1:0] and MGstart.

See the “Other Chip Controls and Features” section (pg. 34) for information about MinClip.

See the “One Volt Input Option” section (pg. 16) for information about OneV.

Rev.1.01

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet XRD98L63.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XRD98L61 | CCD Image Digitizers | Exar |

| XRD98L62 | CCD Image Digitizers | Exar |

| XRD98L63 | CCD Image Digitizers with CDS/ PGA and 12-Bit A/D | Exar Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |