|

|

PDF ICS97U877 Data sheet ( Hoja de datos )

| Número de pieza | ICS97U877 | |

| Descripción | 1.8V Wide Range Frequency Clock Driver | |

| Fabricantes | Integrated Circuit Solution Inc | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS97U877 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

ICS97U8 7 7

1.8V Wide Range Frequency Clock Driver

Recommended Application:

• DDR2 Memory Modules / Zero Delay Board Fan Out

• Provides complete DDR DIMM logic solution with

ICSSSTU32864

Product Description/Features:

• Low skew, low jitter PLL clock driver

• 1 to 10 differential clock distribution (SSTL_18)

• Feedback pins for input to output synchronization

• Spread Spectrum tolerant inputs

• Auto PD when input signal is at a certain logic state

Switching Characteristics:

• Period jitter: 40ps

• Half-period jitter: 60ps

• CYCLE - CYCLE jitter 40ps

• OUTPUT - OUTPUT skew: 40ps

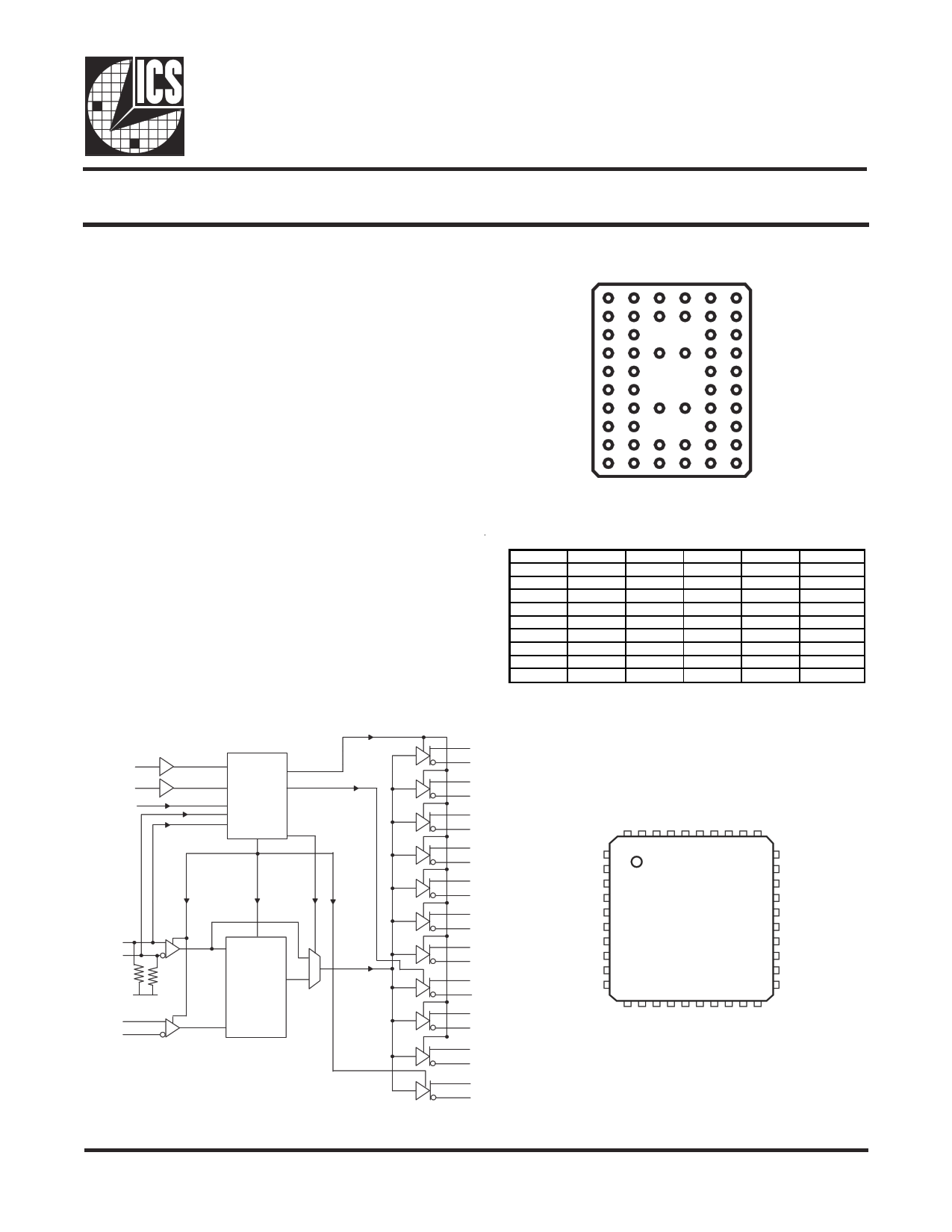

Pin Configuration

123456

A

B

C

D

E

F

G

H

J

K

1

A CLKT1

B CLKC1

C CLKC2

D CLKT2

E CLK_INT

F CLK_INC

G AGND

H AVDD

J CLKT3

K CLKC3

52-Ball BGA

Top View

2

CLKT0

GND

GND

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

CLKC4

3

CLKC0

GND

NB

VDDQ

NB

NB

VDDQ

NB

GND

CLKT4

4

CLKC5

GND

NB

VDDQ

NB

NB

VDDQ

NB

GND

CLKT9

5

CLKT5

GND

GND

OS

VDDQ

OE

VDDQ

GND

GND

CLKC9

6

CLKT6

CLKC6

CLKC7

CLKT7

FB_INT

FB_INC

FB_OUTC

FB_OUTT

CLKT8

CLKC8

Block Diagram

OE

OS

AVDD

Powerdown

Control and

Test Logic

LD* or OE

LD*, OS or OE

LD* PLL bypass

CLK_INT

CLK_INC

10K-100k

GND

PLL

FB_INT

FB_INC

* The Logic Detect (LD) powers down the device when a

logic low is applied to both CLK_INT and CLK_INC.

CLKT0

CLKC0

CLKT1

CLKC1

CLKT2

CLKC2

CLKT3

CLKC3

CLKT4

CLKC4

CLKT5

CLKC5

CLKT6

CLKC6

CLKT7

CLKC7

CLKT8

CLKC8

CLKT9

CLKC9

FB_OUTT

FB_OUTC

40 31

VDDQ 1

CLKC2

CLKT2

CLK_INT

CLK_INC

VDDQ

AGND

AVDD

VDDQ

GND 10

ICS97U877

30 CLKC7

CLKT7

VDDQ

FB_INT

FB_INC

FB_OUTC

FB_OUTT

VDDQ

OE

21 OS

11 20

40-Pin MLF

0792A—04/15/04

1 page

ICS97U8 7 7

Recommended Operating Condition (see note1)

TA = 0 - 70°C; Supply Voltage AVDD, VDDQ = 1.8 V +/- 0.1V (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

Supply Voltage

VDDQ, AVDD

CLK_INT, CLK_INC, FB_INC,

1.7

Low level input voltage

VIL FB_INT

OE, OS

High level input voltage

DC input signal voltage (note

2)

Differential input signal

voltage (note 3)

VIH

CLK_INT, CLK_INC, FB_INC,

FB_INT

0.65 x VDDQ

OE, OS

0.65 x VDDQ

VIN -0.3

DC - CLK_INT, CLK_INC,

VID

FB_INC, FB_INT

AC - CLK_INT, CLK_INC,

FB_INC, FB_INT

0.3

0.6

Output differential cross-

voltage (note 4)

VOX

VDDQ/2 - 0.10

Input differential cross-

voltage (note 4)

VIX

VDDQ/2 - 0.15

High level output current

Low level output current

Operating free-air

temperature

IOH

IOL

TA

0

TYP

1.8

VDD/2

MAX

1.9

UNITS

V

0.35 x VDDQ

0.35 x VDDQ

V

V

V

V

VDDQ + 0.3

V

VDDQ + 0.4

V

VDDQ + 0.4

V

VDDQ/2 + 0.10 V

VDDQ2 + 0.15

-9

9

70

V

mA

mA

°C

Notes:

1. Unused inputs must be held high or low to prevent them from floating.

2. DC input signal voltage specifies the allowable DC execution of differential input.

3. Differential inputs signal voltages specifies the differential voltage [VTR-VCP]

required for switching, where VTR is the true input level and VCP is the

complementary input level.

4. Differential cross-point voltage is expected to track variations of VDDQ and is the

voltage at which the differential signal must be crossing.

0792A—04/15/04

5

5 Page

ICS97U8 7 7

Figure 11. AVDD Filtering

- Place the 2200pF capacitor close to the PLL.

- Use a wide trace for the PLL analog power & ground. Connect PLL & caps to AGND trace & connect trace to one

GND via (farthest from PLL).

- Recommended bead: Fair-Rite P/N 2506036017Y0 or equivalent (0.8 Ohm DC max, 600 Ohms @ 100 MHz).

0792A—04/15/04

11

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet ICS97U877.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS97U877 | 1.8V Wide Range Frequency Clock Driver | Integrated Circuit Solution Inc |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |