|

|

PDF SAA7201H Data sheet ( Hoja de datos )

| Número de pieza | SAA7201H | |

| Descripción | Integrated MPEG2 AVG decoder | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SAA7201H (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

SAA7201

Integrated MPEG2 AVG decoder

Objective specification

File under Integrated Circuits, IC02

1997 Jan 29

1 page

Philips Semiconductors

Integrated MPEG2 AVG decoder

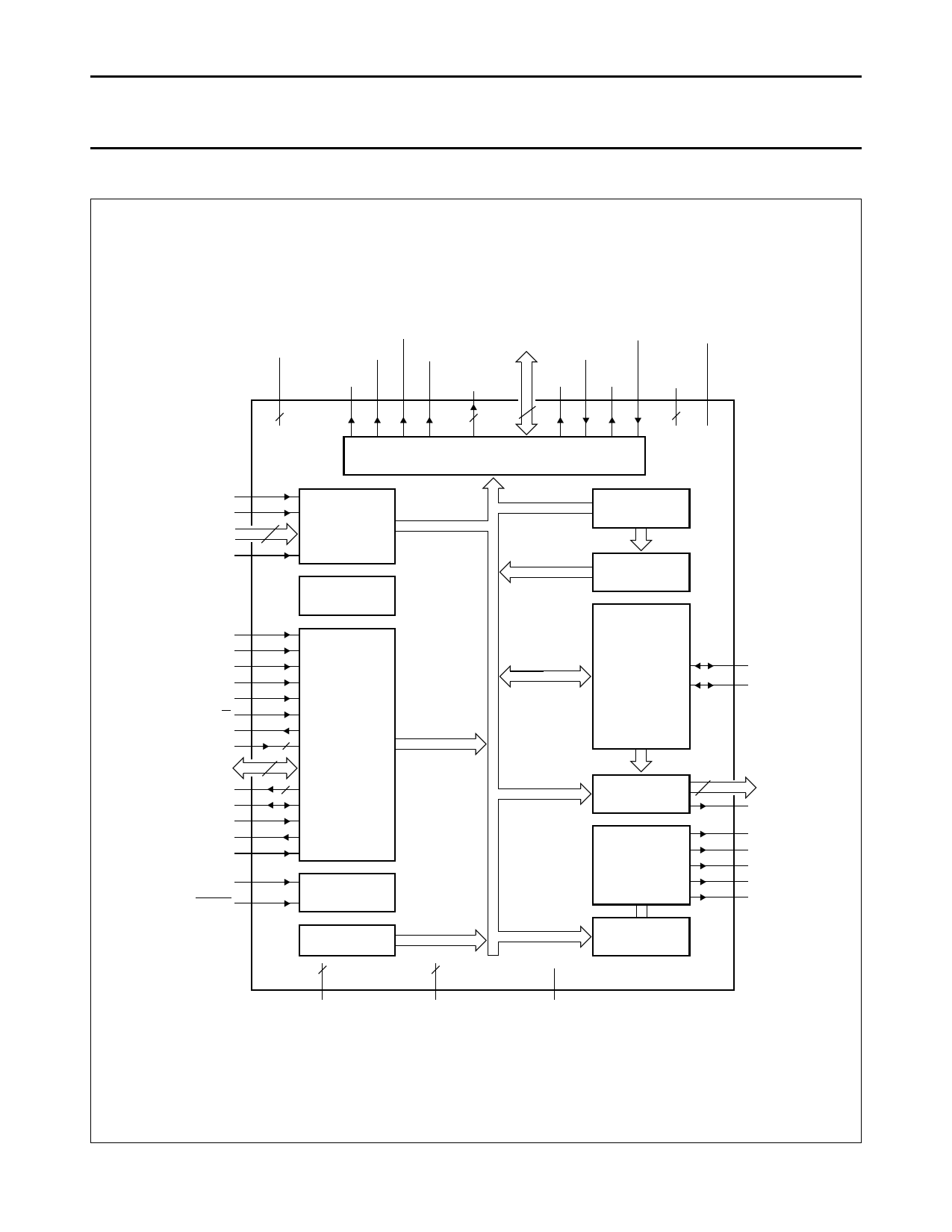

BLOCK DIAGRAM

Objective specification

SAA7201

handbook, full pagewidth

VDDCO1 to

SDRAM_WE

SDRAM_DATA

READI

VDDA

VDDCO4 SDRAM_CAS SDRAM_UDQ (15 to 0) CP81MEXT

SDRAM_RAS

SDRAM_ADDR

(11 to 0)

CP81M READO

VDD1 to

VDD16

77 75 74 78

16 84 83 81 80

121

4 12

16

MEMORY

INTERFACE

A_STROBE

V_STROBE

AV_DATA(0 to 7)

ERROR

159

148

8

147

AUDIO/VIDEO

INTERFACE

CPU_TYPE

MUX

CS

DS

AS

R/W

DTACK

ADDRESS(8 to 1)

DATA(15 to 0)

IRQ(3 to 0)

DMA_REQ

DMA_ACK

DMA_RDY

DMA_DONE

CLK

RESET

2

1

8

9

10

11

12

8

16

4

4

3

6

5

124

138

SYSTEM TIME

BASE UNIT

HOST

INTERFACE

CLOCK

GENERATION

SAA7201

VIDEO INPUT

BUFFER & SYNC

VIDEO

DECODER

DISPLAY

UNIT

106

HS

107

VS

GRAPHICS

UNIT

AUDIO

DECODER

8

119

143

142

145

146

139

YUV(7 to 0)

GRPH

SD

SCLK

WS

SPDIF

FSCLK

JTAG

4

16

VSSCO1 to VSSCO4 VSS1 to VSS16

AUDIO INPUT

BUFFER & SYNC

122

VSSA

MGD322

1997 Jan 29

Fig.1 Block diagram.

5

5 Page

Philips Semiconductors

Integrated MPEG2 AVG decoder

Objective specification

SAA7201

FUNCTIONAL DESCRIPTION

General

The SAA7201 is an MPEG2 decoder which combines

audio decoding, video decoding and enhanced region

based graphics. The decoder operates with a single

16 Mbit external synchronous dynamic random access

memory (SDRAM) and runs from a single external 27 MHz

clock. Due to the optimized memory control for MPEG2

decoding, more than 1 Mbit is available for graphics in

50 Hz systems.

MPEG2 data can be accepted up to 9 Mbytes/s through a

dedicated byte wide interface. The data on this interface

can be either in PES (Packetized Elementary Stream),

MPEG1 packet or ES (Elementary Stream) format as

described in Chapter “References”. Two additional strobe

signals distinguish between audio and video data.

The internal video decoder is capable of decoding all

MPEG compliant streams up to main level main profile as

specified in Chapter “References”. The audio decoder

implements 2 channel audio decoding according to the

standards in Chapter “References”.

All real time audio/video decoding and synchronization

tasks are performed autonomously, so the external

microcontroller only needs to perform high-level tasks like

initialization, status monitoring and trick mode control.

The main support task of the external microcontroller

concerns the control of the graphical unit. This unit should

be supplied with bit-maps, determining the contents of the

graphical regions and by a simple set of instructions

determining the appearance of the graphical data on the

screen. Most graphical information should be stored in the

external memory which implies multiple data transfers

between CPU and the external memory. By performing

these data transfers on a direct memory access (DMA)

basis, full bit-maps can be transferred within one video

frame period.

The video output, containing a mix of MPEG video and

graphical data, is at a YUV multiplexed format which can

be directly connected to an external composite video

encoder. The audio output, containing a mix of MPEG

audio and programmable ‘beeps’, is in a serial, I2S or

Japanese format which can be directly supplied to most

commercially available up-sampling audio DA converters.

A functional block diagram of the decoder is given in Fig.1.

Its application environment is depicted in Fig.24. In the

following sections, a brief description of the individual

internal blocks of the MPEG2 decoder will be given.

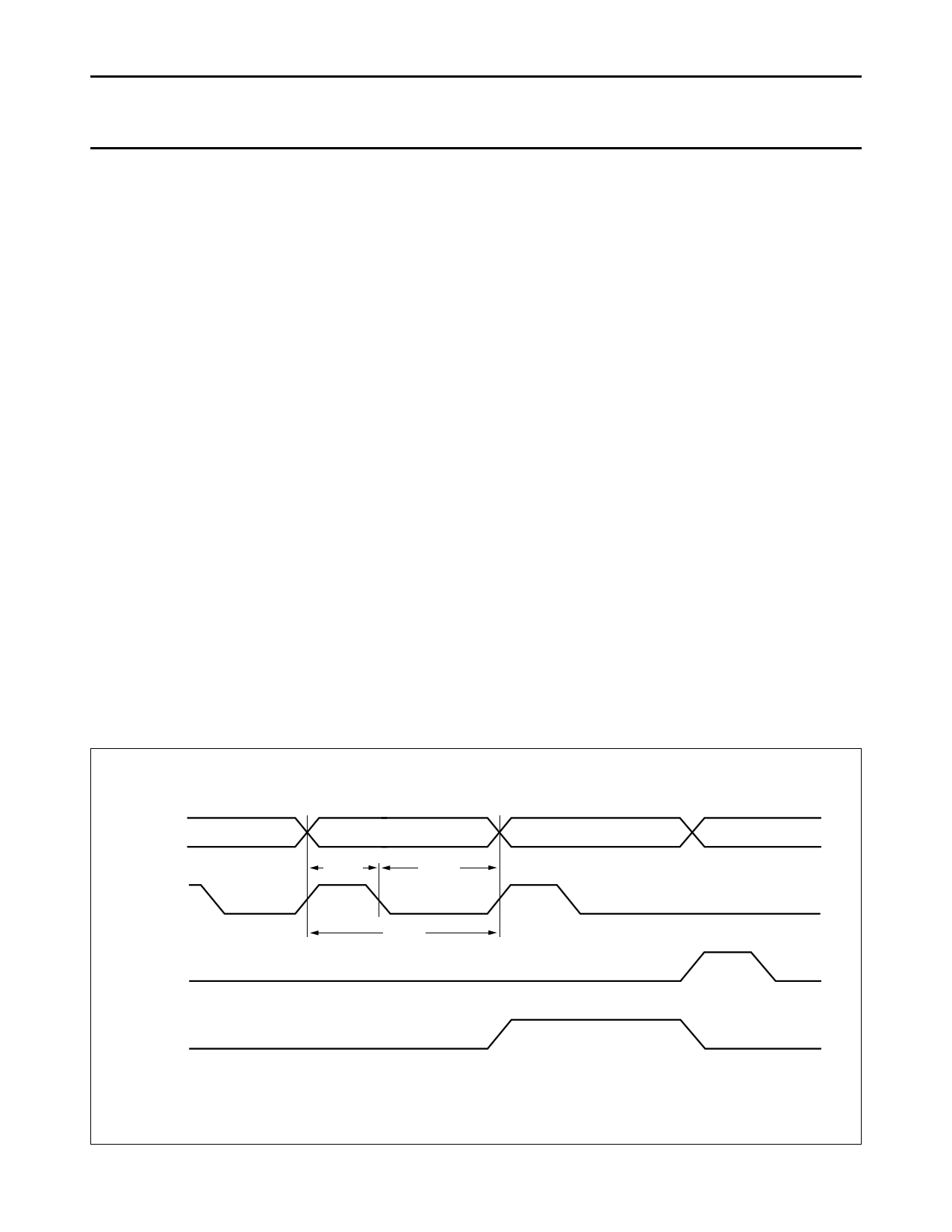

Audio/video interface

In a basic set-top box application the SAA7201 receives

audio and video PES data in a byte wide format at rates up

to 9 Mbytes/s. A timing diagram is shown in Fig.3. Next to

the 8-bit wide data bus an audio and video strobe is

expected at the input. Erroneous data may be flagged via

the error indicator.

handbooAk,Vfu_llDpAagTeAwidth

(0 to 7)

V_STROBE

A_STROBE

ERROR

1997 Jan 29

video byte (n)

≥25 ns

≥25 ns

≥111 ns

video byte (n + 1)

audio byte (m)

Fig.3 Timing diagram of parallel input mode.

11

MGD323

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SAA7201H.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SAA7201 | Integrated MPEG2 AVG decoder | NXP Semiconductors |

| SAA7201H | Integrated MPEG2 AVG decoder | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |