|

|

PDF SAA7128 Data sheet ( Hoja de datos )

| Número de pieza | SAA7128 | |

| Descripción | Digital video encoder | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SAA7128 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

SAA7128H; SAA7129H

Digital video encoder

Product specification

File under Integrated Circuits, IC22

2000 Mar 08

1 page

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

RESET SDA SCL

VDDA1 VDDA3

XTALI XTALO RCV1 RCV2 TTXRQ XCLK LLC1

VDDA2 VDDA4

VDD(I2C)

SA

20

21

40 42 41

I2C-BUS

INTERFACE

I2C-bus control

SAA7128H

SAA7129H

35 34 7 8 43 37 4

25 28 31 36

SYNC/CLOCK

clock and timing

I2C-bus control

I2C-bus control

I2C-bus control

9 to 16 MPpos

MP7 to MP0

MPneg

MPA

SWITCH

MPB

MP

FADER

VP

44

TTX

I2C-bus control

YY

CbCr

ENCODER

C

OUTPUT

INTERFACE

D

I2C-bus

control

I2C-bus control

Y

CbCr

RGB

PROCESSOR

D

30 CVBS

(CSYNC)

27 VBS

(CVBS)

A 24 C

(CVBS)

22

VSSA1

32

VSSA2

33 VSSA3

23

RED

26

GREEN

29

A BLUE

5 18 38 6 17 39 2 3

19

VSSD1 VSSD2 VSSD3 VDDD1 VDDD2 VDDD3 SP AP

RTCI

MHB572

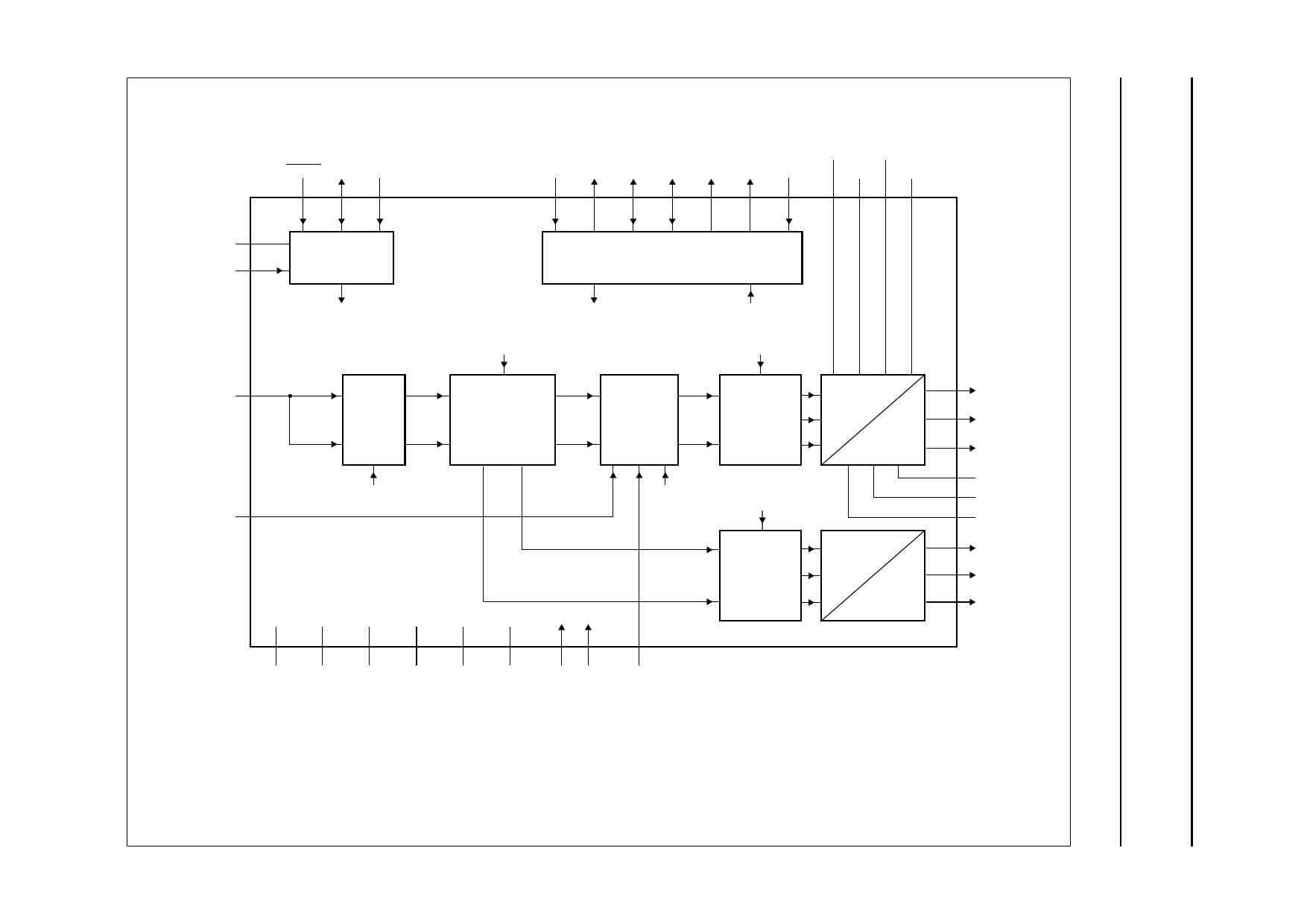

Fig.1 Block diagram.

5 Page

Philips Semiconductors

Digital video encoder

Product specification

SAA7128H; SAA7129H

7.3.2 TELETEXT INSERTION AND ENCODING

Pin TTX receives a WST or NABTS teletext bitstream

sampled at the LLC clock. Two protocols are provided:

• At each rising edge of output signal (TTXRQ) a single

teletext bit has to be provided after a programmable

delay at input pin TTX

• The signal TTXRQ performs only a single LOW-to-HIGH

transition and remains at HIGH level for 360, 296 or 288

teletext bits, depending on the chosen standard.

Phase variant interpolation is achieved on this bitstream in

the internal teletext encoder, providing sufficient small

phase jitter on the output text lines.

TTXRQ provides a fully programmable request signal to

the teletext source, indicating the insertion period of

bitstream at lines which are selectable independently for

both fields. The internal insertion window for text is set to

360 (PAL-WST), 296 (NTSC-WST) or 288 (NABTS)

teletext bits including clock run-in bits. The protocol and

timing are illustrated in Fig.23.

7.3.3 VIDEO PROGRAMMING SYSTEM (VPS) ENCODING

Five bytes of VPS information can be loaded via the

I2C-bus and will be encoded in the appropriate format into

line 16.

7.3.4 CLOSED CAPTION ENCODER

Using this circuit, data in accordance with the specification

of closed caption or extended data service, delivered by

the control interface, can be encoded (line 21). Two

dedicated pairs of bytes (two bytes per field), each pair

preceded by run-in clocks and framing code, are possible.

The actual line number where data is to be encoded in, can

be modified in a certain range.

The data clock frequency is in accordance with the

definition for NTSC-M standard 32 times horizontal line

frequency.

Data LOW at the output of the DACs corresponds to 0 IRE,

data HIGH at the output of the DACs corresponds to

approximately 50 IRE.

It is also possible to encode closed caption data for 50 Hz

field frequencies at 32 times horizontal line frequency.

7.3.5 ANTI-TAPING (SAA7128H ONLY)

For more information contact your nearest Philips

Semiconductors sales office.

7.4 RGB processor

This block contains a dematrix in order to produce red,

green and blue signals to be fed to a SCART plug.

Before Y, CB and CR signals are de-matrixed, individual

gain adjustment for Y and colour difference signals and

2 times oversampling for luminance and 4 times

oversampling for colour difference signals is performed.

The transfer curves of luminance and colour difference

components of RGB are illustrated in Figs 12 and 13.

7.5 SECAM processor

SECAM specific pre-processing is achieved in this block

by a pre-emphasis of colour difference signals (for gain

and phase see Figs 14 and 15).

A baseband frequency modulator with a reference

frequency shifted from 4.286 MHz to DC carries out

SECAM modulation in accordance with appropriate

standard or optionally wide clipping limits.

After the HF pre-emphasis, also applied on a DC reference

carrier (anti-Cloche filter; see Figs 16 and 17), line-by-line

sequential carriers with black reference of 4.25 MHz (Db)

and 4.40625 MHz (Dr) are generated using specified

values for FSC programming bytes.

Alternating phase reset in accordance with SECAM

standard is carried out automatically. During vertical

blanking the so-called bottle pulses are not provided.

7.6 Output interface/DACs

In the output interface, encoded Y and C signals are

converted from digital-to-analog in a 10-bit resolution.

Y and C signals are also combined to a 10-bit CVBS

signal.

The CVBS output occurs with the same processing delay

(equal to 82 LLC clock periods, measured from MP input

to the analog outputs) as the Y, C and RGB outputs.

Absolute amplitude at the input of the DAC for CVBS is

reduced by 15⁄16 with respect to Y and C DACs to make

maximum use of conversion ranges.

Red, green and blue signals are also converted from

digital-to-analog, each providing a 9-bit resolution.

Outputs of the DACs can be set together via software

control to minimum output voltage (approximately 0.2 V

DC) for either purpose. Alternatively, the buffers can be

switched into 3-state output condition; this allows for ‘wired

AND’ing with other 3-state outputs and can also be used

as a power-save mode.

2000 Mar 08

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SAA7128.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SAA7120 | Digital Video Encoder (ConDENC) | NXP Semiconductors |

| SAA7120H | (SAA7120H / SAA7121H) Digital video encoder | NXP Semiconductors |

| SAA7121 | Digital Video Encoder (ConDENC) | NXP Semiconductors |

| SAA7124 | Digital Video Encoder ECO-DENC | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |