|

|

PDF SAA7121 Data sheet ( Hoja de datos )

| Número de pieza | SAA7121 | |

| Descripción | Digital Video Encoder (ConDENC) | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SAA7121 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

SAA7120; SAA7121

Digital Video Encoder (ConDENC)

Preliminary specification

File under Integrated Circuits, IC22

1997 Jan 06

1 page

Philips Semiconductors

Digital Video Encoder (ConDENC)

Preliminary specification

SAA7120; SAA7121

SYMBOL

VSSD3

VDDD3

RESET

PIN

38

39

40

SCL

SDA

TTXRQ

TTX

41

42

43

44

I/O DESCRIPTION

I digital ground 3

I digital supply voltage 3

I reset input, active LOW; after reset is applied, all digital I/Os are in input mode;

the I2C-bus receiver waits for the START condition

I I2C-bus serial clock input

I/O I2C-bus serial data input/output

O teletext request output, indicating when bit stream is valid

I teletext bit stream input

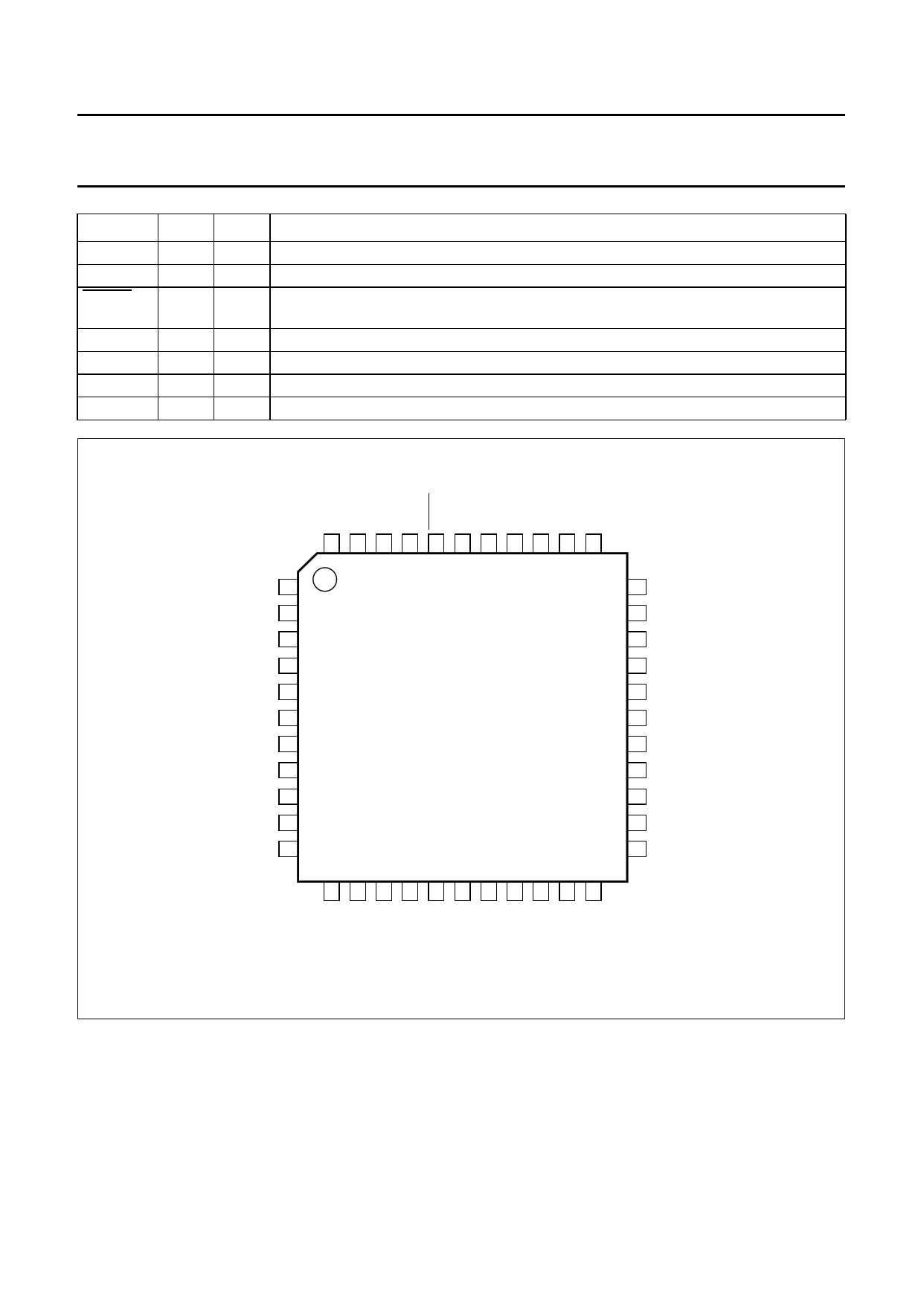

handbook, full pagewidth

res. 1

SP 2

AP 3

LLC 4

VSSD1 5

VDDD1 6

RCV1 7

RCV2 8

MP7 9

MP6 10

MP5 11

SAA7120

SAA7121

33 VSSA2

32 VSSA1

31 VDDA3

30 CVBS

29 res.

28 VDDA2

27 Y

26 res.

25 VDDA1

24 C

23 res.

MBH790

Fig.2 Pin configuration.

1997 Jan 06

5

5 Page

Philips Semiconductors

Digital Video Encoder (ConDENC)

Preliminary specification

SAA7120; SAA7121

I2C-bus interface

The I2C-bus interface is a standard slave transceiver,

supporting 7-bit slave addresses and 400 kbits/s

guaranteed transfer rate. It uses 8-bit subaddressing with

an auto-increment function. All registers are write only,

except one readable status byte.

Two I2C-bus slave addresses are present:

88H: LOW at pin SA

8CH: HIGH at pin SA.

Tables 5 and 4 summarize the format of the I2C-bus

addressing. For more information on how to use the

I2C-bus see “The I2C-bus and how to use it”, order

no. 9398 393 40011. Tables 7 to 42 contain the

programming information for the subaddresses. Table 6

summarises this information.

Table 3 8-bit multiplexed format (similar to “CCIR 601”)

Sample

Luminance pixel number

Colour pixel number

0

Cb0

0

1

Y0

0

2

Cr0

1

BITS

24

Y1 Cb2

2

5

Y2

2

6

Cr2

3

7

Y3

Table 4 I2C-bus address format; see Table 5

S SLAVE ADDRESS ACK SUBADDRESS ACK DATA 0 ACK

--------

DATA n ACK P

Table 5 Explanation of Table 4

PART

S

Slave address

ACK

Subaddress(2)

DATA

--------

P

START condition

1 0 0 0 1 0 0 x or 1 0 0 0 1 1 0 x (1)

acknowledge, generated by the slave

subaddress byte

data byte

continued data bytes and ACKs

STOP condition

DESCRIPTION

Notes

1. x is the read/write control bit; write:

x = logic 0;

read: x = logic 1, no subaddressing with read.

2. If more than 1 byte DATA is transmitted, then auto-increment of the subaddress is performed.

1997 Jan 06

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SAA7121.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SAA7120 | Digital Video Encoder (ConDENC) | NXP Semiconductors |

| SAA7120H | (SAA7120H / SAA7121H) Digital video encoder | NXP Semiconductors |

| SAA7121 | Digital Video Encoder (ConDENC) | NXP Semiconductors |

| SAA7124 | Digital Video Encoder ECO-DENC | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |