|

|

PDF SAA7103E Data sheet ( Hoja de datos )

| Número de pieza | SAA7103E | |

| Descripción | Digital video encoder | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SAA7103E (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

SAA7102; SAA7103

Digital video encoder

Product specification

File under Integrated Circuits, IC22

2001 Sep 25

1 page

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

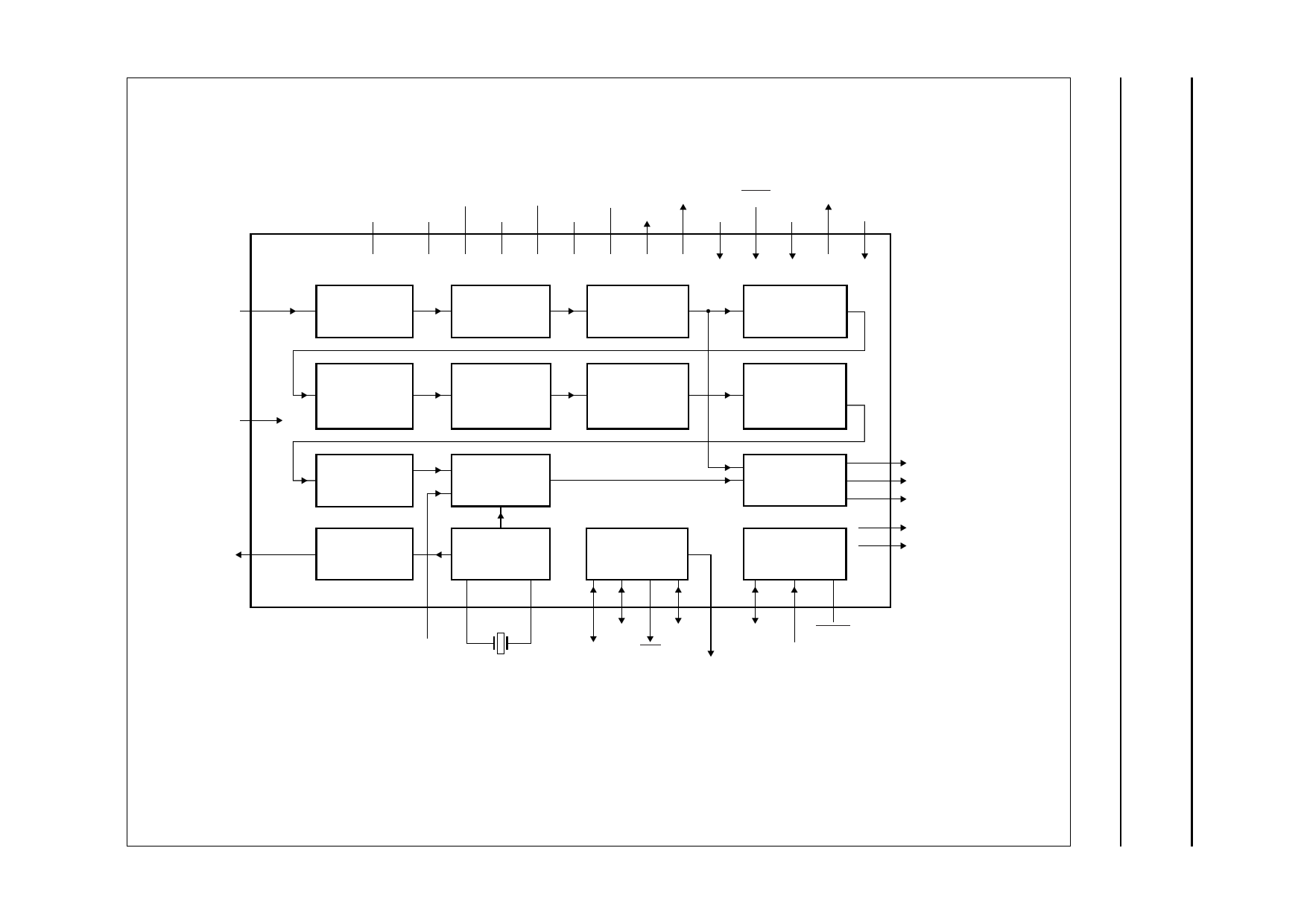

PD11 to

PD0

4 to 1,

44 to 41,

16 to 19

VDDD1

VDDD2

VDDA2

VSSA1

RSET

TRST

TDO

VSSD1

VSSD2

VDDA1

DUMP

TDI

TCLK

TMS

10 9 40 39 36 29 33 32 31 38 37 8 7 6

INPUT

FORMATTER

RGB LUT

(OR BYPASS)

CURSOR

INSERTION

RGB TO Y-CB-CR

MATRIX

(OR BYPASS)

15

PIXCLKI

20

PIXCLKO

DECIMATOR

4 : 4 : 4 to 4 : 2 : 2

(OR BYPASS)

HORIZONTAL

SCALER

VERTICAL

SCALER AND

ANTI-FLICKER

FILTER

FIFO

BORDER

GENERATOR

CGC

LOW-PASS

VIDEO

ENCODER

OSCILLATOR/

DTO

SAA7102H

SAA7103H

TIMING

GENERATOR

TRIPLE

DAC

I2C-BUS

CONTROL

30 BLUE_CB_CVBS

28 GREEN_VBS_CVBS

27 RED_CR_C

26 HSM_CSYNC

25 VSM

23 35

XTALI

TTX_SRES

27 MHz

34

XTAL

13 14 21 22 24

12

VSVGC HSVGC

SDA

FSVGC

CBO

TTXRQ_XCLKO2

11 5

RESET

SCL

MHB963

Fig.1 Block diagram.

5 Page

Philips Semiconductors

Digital video encoder

Product specification

SAA7102; SAA7103

7.1 Reset conditions

To activate the reset a pulse at least of 2 crystal clocks

duration is required.

During reset (RESET = LOW) plus an extra 32 crystal

clock periods, FSVGC, VSVGC, CBO, HSVGC and

TTX_SRES are set to input mode and HSM_CSYNC and

VSM are set to 3-state. A reset also forces the I2C-bus

interface to abort any running bus transfer and sets it into

receive condition.

After reset, the state of the I/Os and other functions is

defined by the strapping pins until an I2C-bus access

redefines the corresponding registers; see Table 2.

Table 2 Strapping pins

PIN TIED

PRESET

FSVGC (pin 13)

LOW NTSC M encoding, PIXCLK

fits to 640 × 480 graphics

input

HIGH PAL B/G encoding, PIXCLK

fits to 640 × 480 graphics

input

VSVGC (pin 14) LOW 4 : 2 : 2 Y-CB-CR graphics

input (format 0)

HIGH 4 : 4 : 4 RGB graphics input

(format 3)

CBO (pin 21)

LOW input demultiplex phase:

LSB = LOW

HIGH input demultiplex phase:

LSB = HIGH

HSVGC (pin 22) LOW input demultiplex phase:

MSB = LOW

HIGH input demultiplex phase:

MSB = HIGH

TTXRQ_XCLKO2 LOW slave (FSVGC, VSVGC and

(pin 24)

HSVGC are inputs, internal

colour bar is active)

HIGH master (FSVGC, VSVGC

and HSVGC are outputs)

If Y-CB-CR is being applied as a 27 Mbyte/s data stream,

the output of the input formatter can be used directly to

feed the video encoder block.

7.3 RGB LUT

The three 256 byte RAMs of this block can be addressed

by three 8-bit wide signals, thus it can be used to build any

transformation, e.g. a gamma correction for RGB signals.

In the event that the indexed colour data is applied, the

RAMs are addressed in parallel.

The LUTs can either be loaded by an I2C-bus write access

or can be part of the pixel data input through the PD port.

In the latter case, 256 × 3 bytes for the R, G and B LUT are

expected at the beginning of the input video line, two lines

before the line that has been defined as first active line,

until the middle of the line immediately preceding the first

active line. The first 3 bytes represent the first RGB LUT

data, and so on.

7.4 Cursor insertion

The cursor bit map is set up as follows: each pixel

occupies 2 bits. The meaning of these bits depends on the

CMODE I2C-bus register as described in Table 5.

Transparent means that the input pixels are passed

through, the ‘cursor colours’ can be programmed in

separate registers.

The bit map is stored with 4 pixels per byte, aligned to the

least significant bit. So the first pixel is in bits 0 and 1, the

next pixel in bits 3 and 4 and so on. The first index is the

column, followed by the row; index 0,0 is the upper left

corner.

Table 3 Layout of a byte in the cursor bit map

D7 D6

pixel n + 3

D1 D0

D5 D4

pixel n + 2

D1 D0

D3 D2

pixel n + 1

D1 D0

D1 D0

pixel n

D1 D0

7.2 Input formatter

The input formatter converts all accepted PD input data

formats, either RGB or Y-CB-CR, to a common internal

RGB or Y-CB-CR data stream.

When double-edge clocking is used, the data is internally

split into portions PPD1 and PPD2. The clock edge

assignment must be set according to the I2C-bus control

bits EDGE1 and EDGE2 for correct operation.

2001 Sep 25

11

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet SAA7103E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SAA7103 | Digital video encoder | NXP Semiconductors |

| SAA7103E | Digital video encoder | NXP Semiconductors |

| SAA7103H | Digital video encoder | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |