|

|

PDF K7I323682M Data sheet ( Hoja de datos )

| Número de pieza | K7I323682M | |

| Descripción | 1Mx36 & 2Mx18 DDRII CIO b2 SRAM | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de K7I323682M (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

K7I323682M

K7I321882M

1Mx36 & 2Mx18 DDRII CIO b2 SRAM

Document Title

1Mx36-bit, 2Mx18-bit DDRII CIO b2 SRAM

Revision History

Rev. No.

History

Draft Date

0.0 1. Initial document.

0.1 1. Pin name change from DLL to Doff.

2. Vddq range change from 1.5V to 1.5V~1.8V.

October, 22 2001

December, 12 2001

3. Update JTAG test conditions.

4. Reserved pin for high density name change from NC to Vss/SA

5. Delete AC test condition about Clock Input timing Reference Level

6. Delete clock description on page 2 and add HSTL I/O comment

0.2

1. Update current characteristics in DC electrical characteristics

July, 29. 2002

2. Change AC timing characteristics

3. Update JTAG instruction coding and diagrams

0.3 1. Add AC electrical characteristics.

2. Change AC timing characteristics.

Sep. 6. 2002

3. Change DC electrical characteristics(ISB1)

0.4 1. Change the data Setup/Hold time.

2. Change the Access Time.(tCHQV, tCHQX, etc.)

Oct. 7. 2002

3. Change the Clock Cycle Time.(MAX value of tKHKH)

4. Change the JTAG instruction coding.

0.5 1. Change the Boundary scan exit order.

2. Change the AC timing characteristics(-25, -20)

Dec. 16, 2002

3. Correct the Overshoot and Undershoot timing diagrams.

0.6 1. Correct the JTAG ID register definition

Mar. 20, 2003

2. Correct the AC timing parameter (delete the tKHKH Max value)

0.7 1. Change the Maximum Clock cycle time.

2. Correct the 165FBGA package ball size.

April. 4, 2003

0.8 1. Change the operating current parameter.

before after

Oct. 29, 2003

Icc(x36) -25 : 620

700

-20 : 520

600

-16 : 440

500

Icc(x18) -25 : 560

670

-20 : 470

570

-16 : 410

470

Icc(x 8 ) -25 : 540

650

-20 : 450

550

-16 : 390

450

Isb1 -25 : 200

230

-20 : 180

200

-16 : 160

190

1.0 1. Final spec release

2.0 1. Delete the x8 Org. part

2.1 1. Change the operating current parameter

before after

Isb1 -25 : 230

250

-20 : 200

230

-16 : 190

220

Oct. 31, 2003

Dec. 1, 2003

July. 27, 2004

Remark

Advance

Preliminary

Preliminary

Preliminary

Preliminary

Preliminary

Preliminary

Preliminary

Preliminary

Final

Final

Final

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the

specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any ques-

tions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

- 1 - July. 2004

Rev 2.1

1 page

K7I323682M

K7I321882M

1Mx36 & 2Mx18 DDRII CIO b2 SRAM

GENERAL DESCRIPTION

The K7I323682M and K7I321882M are 37,748,736-bits DDR Common I/O

Synchronous Pipelined Burst SRAMs.

They are organized as 1,048,576 words by 36bits for K7I323682M and 2,097,152 words by 18 bits for K7I321882M .

Address, data inputs, and all control signals are synchronized to the input clock ( K or K ).

Normally data outputs are synchronized to output clocks ( C and C ), but when C and C are tied high,

the data outputs are synchronized to the input clocks ( K and K ).

Read data are referenced to echo clock ( CQ or CQ ) outputs.

Read address and write address are registered on rising edges of the input K clocks.

Common address bus is used to access address both for read and write operations.

The internal burst counter is fiexd to 2-bit sequential for both read and write operations.

Synchronous pipeline read and late write enable high speed operations.

Simple depth expansion is accomplished by using LD for port selection.

Byte write operation is supported with BW0 and BW1 ( BW2 and BW3) pins for x18 ( x36 ) device.

Nybble write operation is supported with NW0 and NW1 pins for x8 device.

IEEE 1149.1 serial boundary scan (JTAG) simplifies monitoriing package pads attachment status with system.

The K7I323682M and K7I321882M are implemented with SAMSUNG's high performance 6T CMOS technology

and is available in 165pin FBGA packages. Multiple power and ground pins minimize ground bounce.

Read Operations

Read cycles are initiated by initiating R/W as high at the rising edge of the positive input clock K.

Address is presented and stored in the read address register synchronized with K clock.

For 2-bit burst DDR operation, it will access two 36-bit, 18-bit or 8-bit data words with each read command.

The first pipelined data is transfered out of the device triggered by C clock following next K clock rising edge.

Next burst data is triggered by the rising edge of following C clock rising edge.

Continuous read operations are initated with K clock rising edge.

And pipelined data are transferred out of device on every rising edge of both C and C clocks.

In case C and C tied to high, output data are triggered by K and K insted of C and C.

When the LD is disabled after a read operation, the K7I323682M and K7I321882M will first complete

burst read operation before entering into deselect mode at the next K clock rising edge.

Then output drivers disabled automatically to high impedance state.

Echo clock operation

To assure the output tracibility, the SRAM provides the output Echo clock, pair of compliment clock CQ and CQ,

which are synchronized with internal data output.

Echo clocks run free during normal operation.

The Echo clock is triggered by internal output clock signal, and transfered to external through same structures

as output driver.

Power-Up/Power-Down Supply Voltage Sequencing

The following power-up supply voltage application is recommended: VSS, VDD, VDDQ, VREF, then VIN. VDD and VDDQ can be applied

simultaneously, as long as VDDQ does not exceed VDD by more than 0.5V during power-up. The following power-down supply voltage

removal sequence is recommended: VIN, VREF, VDDQ, VDD, VSS. VDD and VDDQ can be removed simultaneously, as long as VDDQ

does not exceed VDD by more than 0.5V during power-down.

- 5 - July. 2004

Rev 2.1

5 Page

K7I323682M

K7I321882M

1Mx36 & 2Mx18 DDRII CIO b2 SRAM

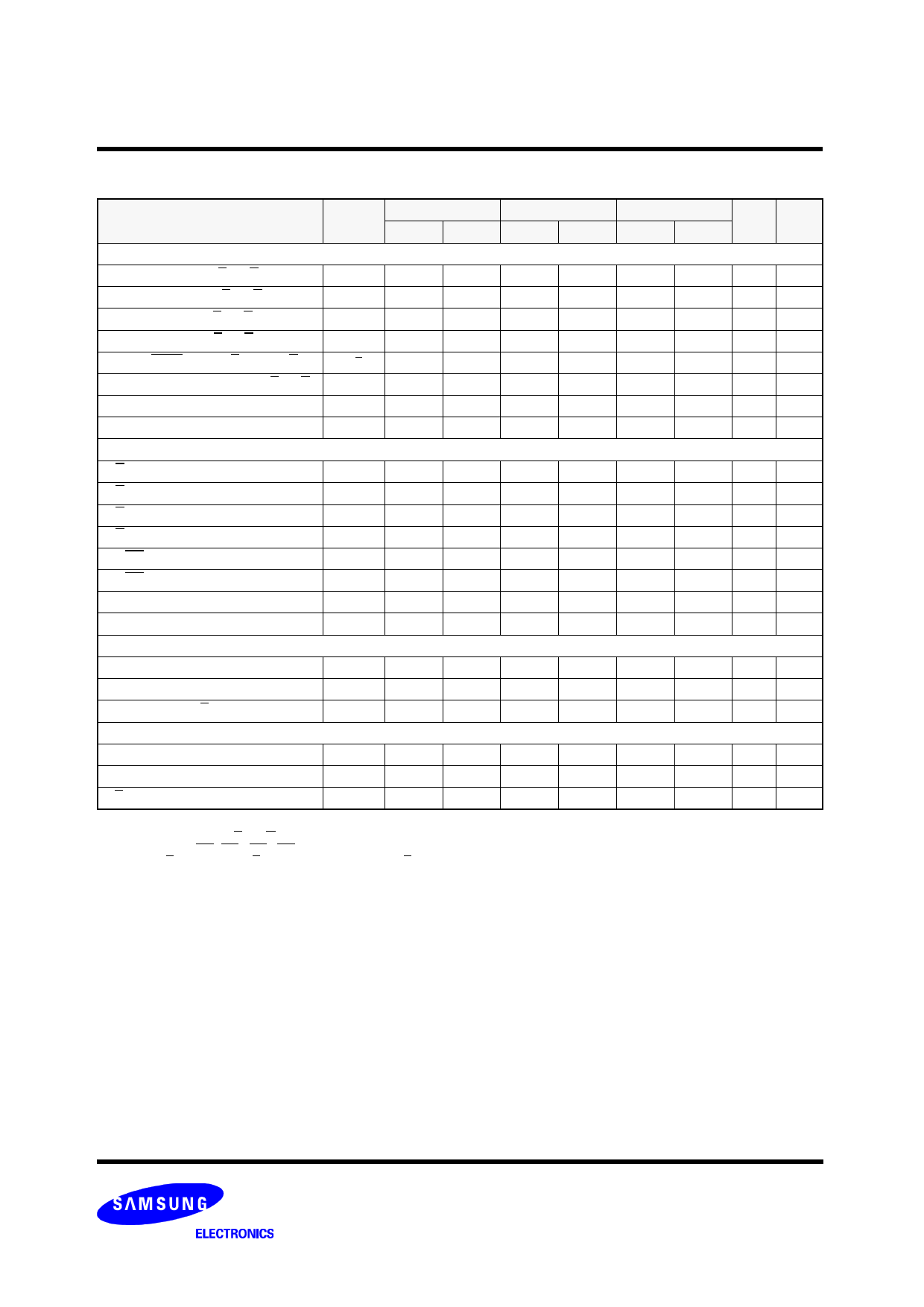

AC TIMING CHARACTERISTICS(VDD=1.8V±0.1V, TA=0°C to +70°C)

PARAMETER

SYMBOL

Clock

Clock Cycle Time (K, K, C, C)

tKHKH

Clock Phase Jitter (K, K, C, C)

tKC var

Clock High Time (K, K, C, C)

tKHKL

Clock Low Time (K, K, C, C)

tKLKH

Clock to Clock (K↑ → K↑, C↑ → C↑)

tKHKH

Clock to data clock (K↑ → C↑, K↑→ C↑) tKHCH

DLL Lock Time (K, C)

tKC lock

K Static to DLL reset

tKC reset

Output Times

C, C High to Output Valid

tCHQV

C, C High to Output Hold

tCHQX

C, C High to Echo Clock Valid

tCHCQV

C, C High to Echo Clock Hold

tCHCQX

CQ, CQ High to Output Valid

tCQHQV

CQ, CQ High to Output Hold

tCQHQX

C, High to Output High-Z

tCHQZ

C, High to Output Low-Z

tCHQX1

Setup Times

Address valid to K rising edge

tAVKH

Control inputs valid to K rising edge

tIVKH

Data-in valid to K, K rising edge

tDVKH

Hold Times

K rising edge to address hold

tKHAX

K rising edge to control inputs hold

tKHIX

K, K rising edge to data-in hold

tKHDX

-25

MIN MAX

4.00

1.60

1.60

1.80

0.00

1024

30

6.30

0.20

1.80

-0.45

-0.45

-0.30

-0.45

0.45

0.45

0.30

0.45

0.50

0.50

0.35

0.50

0.50

0.35

-20

MIN MAX

5.00

2.00

2.00

2.20

0.00

1024

30

7.88

0.20

2.30

-0.45

-0.45

-0.35

-0.45

0.45

0.45

0.35

0.45

0.60

0.60

0.40

0.60

0.60

0.40

-16

UNITS NOTES

MIN MAX

6.00

2.40

2.40

2.70

0.00

1024

30

8.40

0.20

2.80

ns

ns

ns

ns

ns

ns

cycle

ns

5

6

0.50 ns

-0.50

ns

0.50 ns

-0.50

ns

0.40 ns

-0.40

ns

0.50 ns

-0.50

ns

3

3

3

3

0.70

0.70

0.50

ns

ns 2

ns

0.70

0.70

0.50

ns

ns

ns

Notes: 1. All address inputs must meet the specified setup and hold times for all latching clock edges.

2. Control signal are R and W.

In case of BW0,BW1 (BW2, BW3, also for x36) signal follow the data setup/hold times.

3. If C,C are tied high, K,K become the references for C,C timing parameters.

4. To avoid bus contention, at a given voltage and temperature tCHQX1 is bigger than tCHQZ.

The specs as shown do not imply bus contention beacuse tCHQX1 is a MIN parameter that is worst case at totally different test conditions

(0°C, 1.9V) than tCHQZ, which is a MAX parameter(worst case at 70°C, 1.7V)

It is not possible for two SRAMs on the same board to be at such different voltage and temperature.

5. Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.

6. Vdd slew rate must be less than 0.1V DC per 50 ns for DLL lock retention. DLL lock time begins once Vdd and input clock are stable.

- 11 -

July. 2004

Rev 2.1

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet K7I323682M.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K7I323682M | 1Mx36 & 2Mx18 DDRII CIO b2 SRAM | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |