|

|

PDF S5N8947 Data sheet ( Hoja de datos )

| Número de pieza | S5N8947 | |

| Descripción | MCU for ADSL/Cable Modem | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de S5N8947 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

S5N8947X

MCU for ADSL/Cable Modem

(Revision 0.1)

May. 23, 2000

SAMSUNG ELECTRONICS PROPRIETARY

Copyright ©1999-2000 Samsung Electronics, Inc. All Rights Reserved

1 page

ELECTRONICS

S5N8947 (ADSL/Cable Modem MCU)

2. FEATURES

ü 4-Kbyte unified cache

ü SAR (Segmentation and Reassembly)

ü UTOPIA (the Universal Test & Operations PHY Interface for ATM) Level 2 Interface

ü Ethernet MAC

ü Full-rate USB controller

ü 2-CH GDMA (General Purpose Direct Memory Access)

ü UART (Universal Asynchronous Receiver and Transmtter)

ü 2 programmable 32bits Timers

ü 18 Programmable I/O ports

ü Interrupt controller

ü I2C controller

ü Built-in PLLs for System/USB

ü Cost effective JTAG-based debug solution

ü Boundary scan

ü Operating Voltage Range(2.5V +/- 0.2V)

ü Operating Frequency Up to 50MHz

ü 208 TQFP Package

SAMSUNG ELECTRONICS

Page : 5

MagIC Team

5 Page

ELECTRONICS

S5N8947 (ADSL/Cable Modem MCU)

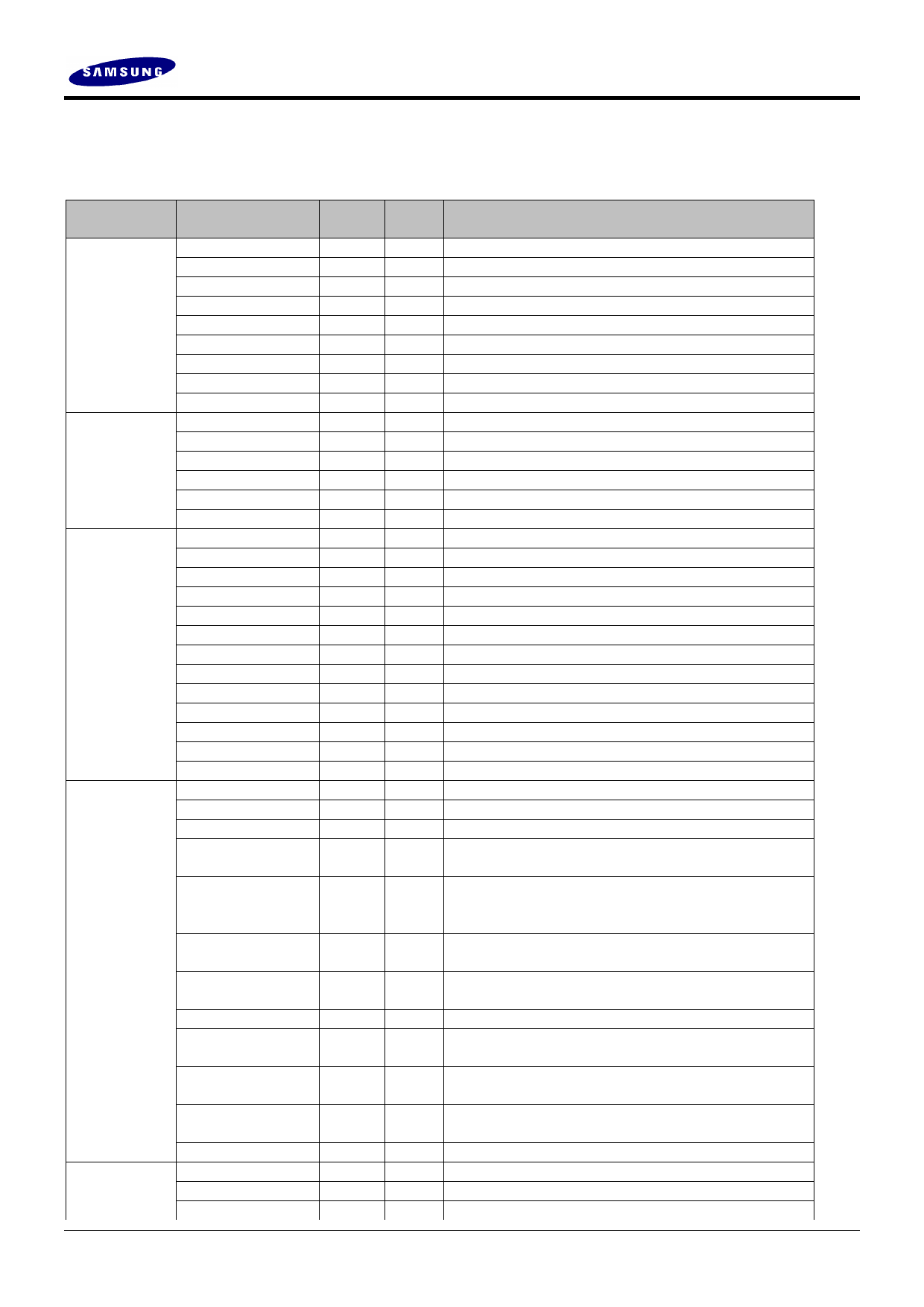

4.2. Pin Descriptions

Group

Pin Name

System

Configurations

(9)

TAP

Control

(5)

Memory

Interface

(81)

Ethernet

Controller

(18)

UART

(5)

XCLK_I

MCLKO

CLKSEL

nRESET

CLKOEN

BIGEND

FILTER_S

OSC_XIN

OSC_XO

TMODE

TCK

TMS

TDI

TDO

nTRST

ADDR[21:0]

XDATA[31:0]

nRAS[3:0]

nCAS[3:0]

nDWE

nECS[3:0]

nDTACK

nRCS[3:0]

B0SIZE[1:0]

nOE

nWBE[3:0]

ExtMREQ

ExtMACK

MCD

MDIO

COL/COL_10M

TX_CLK/

TX_CLK_10M

TXD[3:0]/

TXD_10M/

LOOP_10M

TX_EN/

TXEN_10M

TX_ERR/

PCOMP_10M

CRS/CRS_10M

RX_CLK/

RXCLK_10M

RXD[3:0]/

RXD_10M

RX_DV/

LINK_10M

RX_ERR

UCLK

UARXD

UATXD

SAMSUNG ELECTRONICS

Pin

Counts

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

22

32

4

4

1

4

1

4

2

1

4

1

1

1

1

1

1

I/O

Type

I

O

I

I

I

I

O

I

O

I

I

I

I

O

I

O

I/O

O

O

O

I/O

I

O

I

O

O

I

O

O

I/O

I

I

Description

External System Clock Source Input.

System Clock Out.

Clock Frequency Select from the internal PLL.

System Reset, Low Active.

System Clock Out Enable.

Big endian mode select pin.

PLL filter pin for System Clock Generation.

12MHz Reference Clock.

Crystal Clock Output.

Test Mode Enable.

JTAG Test Clock Input.

JTAG Test Mode Select.

JTAG Test Data Input.

JTAG Test Data Output.

JTAG Reset Signal, Low Active.

Address Bus.

External Bidirectional 32bit Data Bus.

Row AddressSstrobe for DRAM, Low Active.

Column Address Strobe for DRAM, Low Active.

Write Enable, Low Active.

External I/O Select, Low Active.

External Data Acknowledge Signal.

ROM/SRAM/Flash Chip Select, Low Active.

Bank 0 Data Bus Size for Boot ROM.

Output Enable, Low Active.

Write Byte Enable, Low Active.

External Master Bus Request.

External Bus Acknowledge.

Management data clock.

Management data I/O.

Collision detected/Collision detected for 10M.

Transmit clk/Transmit clk for 10M.

4 O Transmit data/Transmit data for 10M.

1 O Transmit enable/Transmit enable for 10M.

1 O Transmit error/Packet compression enable for 10M.

1 I Carrier sense/Carrier sense for 10M.

1 I Receive clock/Receive clock for 10M.

4 I Receive data/Receive data for 10M.

1 I Receive data valid.

1 I Receive error.

1 I External Clock Input for UART.

1 I UART Receive Data.

1 O UART Transmit Data.

Page : 11

MagIC Team

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S5N8947.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S5N8943B | G.Lite ADSL Analog Front End IC | Samsung semiconductor |

| S5N8944B | G.Lite ADSL Transceiver for CO and CPE | Samsung semiconductor |

| S5N8947 | MCU for ADSL/Cable Modem | Samsung semiconductor |

| S5N8947X | MCU for ADSL/Cable Modem | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |