|

|

PDF IDT71V256SB Data sheet ( Hoja de datos )

| Número de pieza | IDT71V256SB | |

| Descripción | 3.3V CMOS FAST SRAM WITH 2.5V COMPATIBLE INPUTS 256K (32K x 8-BIT) | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT71V256SB (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

Integrated Device Technology, Inc.

3.3V CMOS FAST SRAM

WITH 2.5V COMPATIBLE INPUTS

256K (32K x 8-BIT)

IDT71V256SB

FEATURES

• Ideal for high-performance processor secondary cache

• Fast access times:

— 12/15/20ns

• Inputs are 2.5V and LVTTL compatible: VIH = 1.8V

• Outputs are LVTTL compatible

• Low standby current (maximum):

— 2mA full standby

• Small packages for space-efficient layouts:

— 28-pin 300 mil SOJ

— 28-pin TSOP Type I

• Produced with advanced high-performance CMOS

technology

• Single 3.3V(±0.3V) power supply

DESCRIPTION

The IDT71V256SB is a 262,144-bit high-speed static RAM

organized as 32K x 8. The improved VIH (1.8V) makes the

inputs compatible with 2.5V logic levels. The IDT71V256SB

is otherwise identical to the IDT71V256SA.

The IDT71V256SB has outstanding low power character-

istics while at the same time maintaining very high perfor-

mance. Address access times of as fast as12 ns are ideal for

tag SRAM in secondary cache designs.

When power management logic puts the IDT71V256SB in

standby mode, its very low power characteristics contribute to

extended battery life. By taking CS HIGH, the SRAM will

automatically go to a low power standby mode and will remain

in standby as long as CS remains HIGH. Furthermore, under

full standby mode (CS at CMOS level, f=0), power consump-

tion is guaranteed to always be less than 6.6mW and typically

will be much smaller.

The IDT71V256SB is packaged in 28-pin 300 mil SOJ and

28-pin300 mil TSOP Type I packaging.

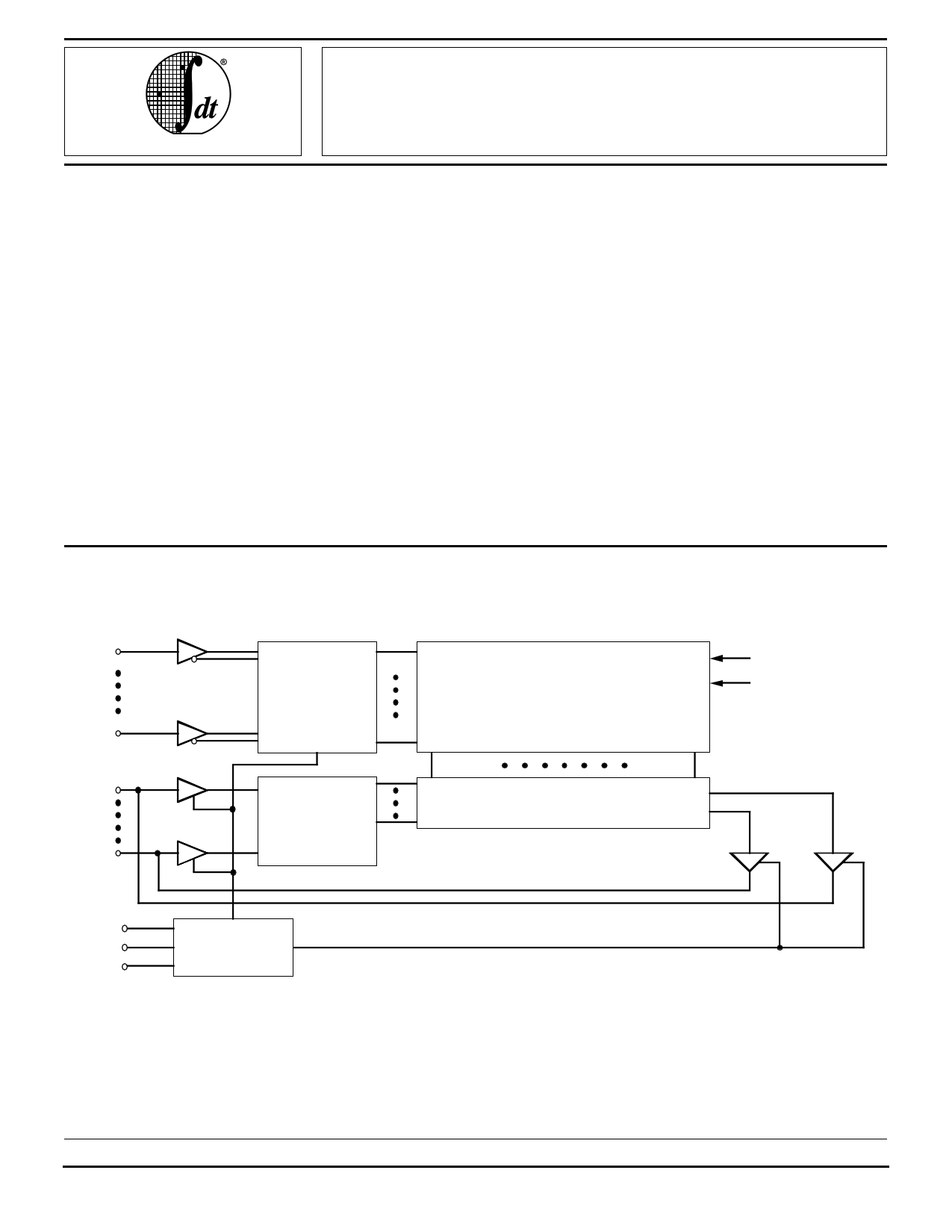

FUNCTIONAL BLOCK DIAGRAM

A0

A14

I/O0

I/O7

CS

OE

WE

ADDRESS

DECODER

INPUT

DATA

CIRCUIT

CONTROL

CIRCUIT

262,144 BIT

MEMORY ARRAY

I/O CONTROL

VCC

GND

3770 drw 01

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

COMMERCIAL TEMPERATURE RANGES

©1997 Integrated Device Technology, Inc.

7.??

JANUARY 1997

3770/1

1

1 page

IDT71V256SB

3.3V CMOS STATIC RAM WITH 2.5V COMPATIBLE INPUTS 256K (32K x 8-BIT)

TIMING WAVEFORM OF READ CYCLE NO. 2(1, 2, 4)

t RC

ADDRESS

DATAOUT

tAA

t OH

PREVIOUS DATA VALID

TIMING WAVEFORM OF READ CYCLE NO. 3(1, 3, 4)

CS

DATAOUT

t ACS

tCLZ (5)

NOTES:

1. WE is HIGH for Read cycle.

2. Device is continuously selected, CS is LOW.

3. Address valid prior to or coincident with CS transition LOW.

4. OE is LOW.

5. Transition is measured ±200mV from steady state.

COMMERCIAL TEMPERATURE RANGE

tOH

DATA VALID

3770 drw 07

DATA VALID

t CHZ (5)

3770 drw 08

TIMING WAVEFORM OF WRITE CYCLE NO. 1 (WE CONTROLLED TIMING)(1, 2, 3, 5, 7)

t WC

ADDRESS

tOHZ (6)

OE

t AW

CS

t AS

tWP (7)

t WR

WE

DATAOUT

DATAIN

t WHZ (6)

(4)

tOW (6)

t DW

t DH

DATA VALID

(4)

3770 drw 09

NOTES:

1. WE or CS must be HIGH during all address transitions.

2. A write occurs during the overlap of a LOW CS and a LOW WE.

3. tWR is measured from the earlier of CS or WE going HIGH to the end of the write cycle.

4. During this period, I/O pins are in the output state so that the input signals must not be applied.

5. If the CS LOW transition occurs simultaneously with or after the WE LOW transition, the outputs remain in a high-impedance state.

6. Transition is measured ±200mV from steady state.

7. If OE is LOW during a WE controlled write cycle, the write pulse width must be the larger of tWP or (tWHZ + tDW) to allow the I/O drivers to turn off and data

to be placed on the bus for the required tDW. If OE is HIGH during a WE controlled write cycle, this requirement does not apply and the write pulse can

be as short as the spectified tWP.

5

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet IDT71V256SB.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT71V256SA | LOW POWER 3.3V CMOS FAST SRAM 256K (32K x 8-BIT) | Integrated Device Technology |

| IDT71V256SA10PZ | LOW POWER 3.3V CMOS FAST SRAM 256K (32K x 8-BIT) | Integrated Device Technology |

| IDT71V256SA10TP | LOW POWER 3.3V CMOS FAST SRAM 256K (32K x 8-BIT) | Integrated Device Technology |

| IDT71V256SA10Y | LOW POWER 3.3V CMOS FAST SRAM 256K (32K x 8-BIT) | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |