|

|

PDF HY51V18163HGJ-7 Data sheet ( Hoja de datos )

| Número de pieza | HY51V18163HGJ-7 | |

| Descripción | 1M x 16Bit EDO DRAM | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HY51V18163HGJ-7 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

HY51V(S)18163HG/HGL

1M x 16Bit EDO DRAM

PRELIMINARY

DESCRIPTION

The HY51V(S)18163HG/HGL is the new generation dynamic RAM organized 1,048,576 words x 16bit.

HY51V(S)18163HG/HGL has realized higher density, higher performance and various functions by utiliz-

ing advanced CMOS process technology. The HY51V(S)18163HG/HGL offers Extended Data Out Page-

Mode as a high speed access mode. Multiplexed address inputs permit the HY51V(S)18163HG/HGL to be

packaged in standard 400mil 42pin SOJ and 44(50) pin TSOP-II. The package size provides high system

bit densities and is compatible with widely available automated testing and insertion equipment.

FEATURES

• Extended Data Out Mode capability

• Read-modify-write capability

• Multi-bit parallel test capability

• TTL(3.3V) compatible inputs and outputs

• /RAS only, CAS-before-/RAS, Hidden and self

refresh(L-version) capability

• Fast access time and cycle time

• JEDEC standard pinout

• 42pin plastic SOJ / 44(50)pin TSOP-II (400mil)

• Single power supply of 3.3V +/- 0.3V

• Battery back up operation(L-version)

• 2CAS byte control

Part No

HY51V(S)18163HG/HGL-5

HY51V(S)18163HG/HGL-6

HY51V(S)18163HG/HGL-7

tRAC

50ns

60ns

70ns

tCAC

13ns

15ns

18ns

tRC

84ns

104ns

124ns

tHPC

20ns

25ns

30ns

• Power dissipation

Active

Standby

50ns

60ns

70ns

684mW

612mW

540mW

7.2mW(CMOS level Max)

0.83mW (L-version : Max)

ORDERING INFORMATION

• Refresh cycle

Part No

HY51V18163HG

HY51V18163HGL

Ref Normal L-part

1K 16ms

1K 128ms

Part Number

HY51V(S)18163HGJ/HG(L)J-5

HY51V(S)18163HGJ/HG(L)J-6

HY51V(S)18163HGJ/HG(L)J-7

HY51V(S)18163HGT/HG(L)T-5

HY51V(S)18163HGT/HG(L)T-6

HY51V(S)18163HGT/HG(L)T-7

(S) : Self refresh,

(L) : Low power

Access Time

50ns

60ns

70ns

50ns

60ns

70ns

Package

400mil 42pin SOJ

400mil 44(50)pin TSOP-II

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any

responsibility for use of circuits described. No patent licenses are implied.

Rev.0.1/Apr.01

1 page

HY51V(S)18163HG/HGL

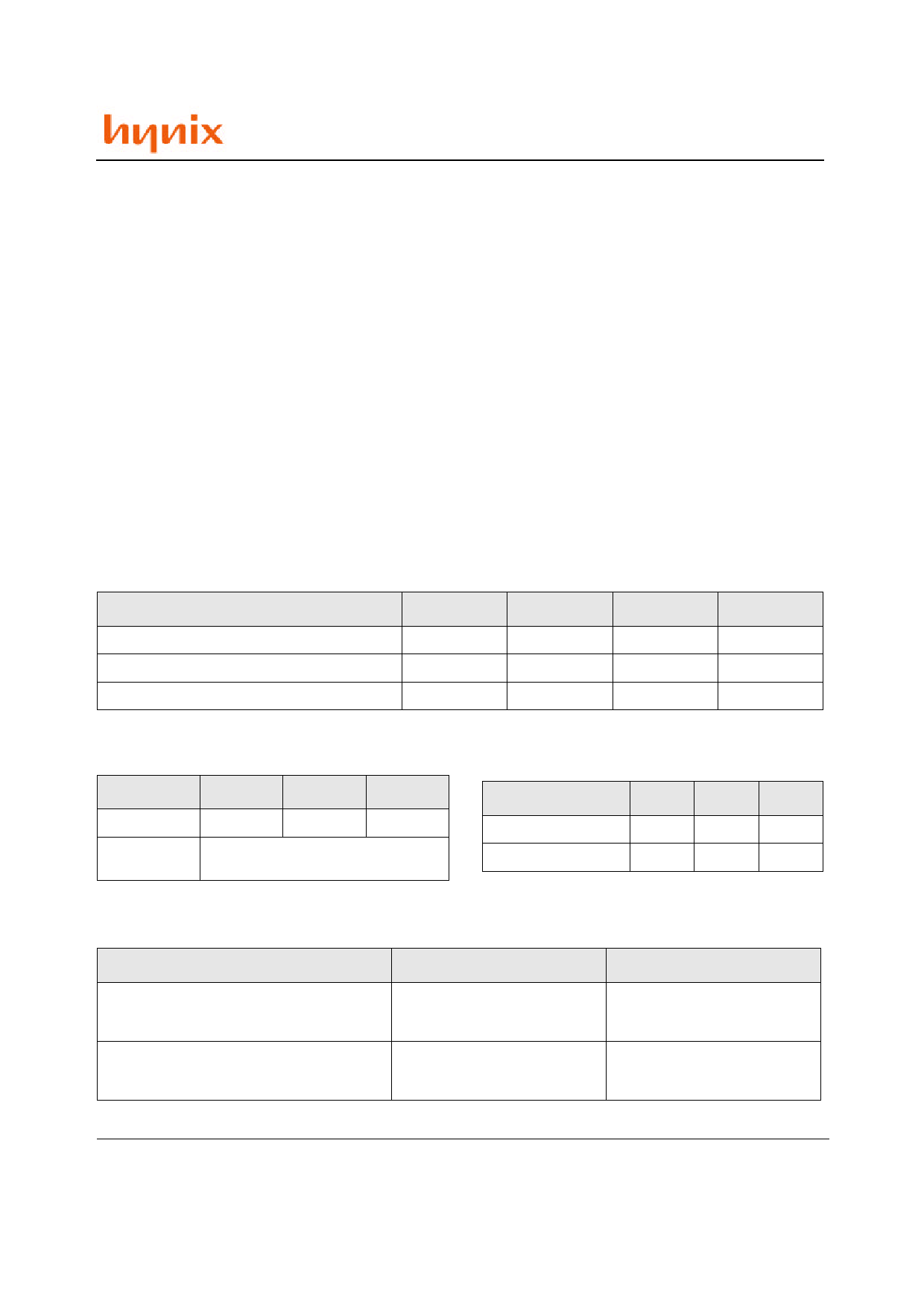

DC CHARACTERISTICS (Vcc = 3.3V +/- 10%, TA=0 to 70°C)

Symbol

Parameter

VOH

Output Level

Output Level voltage(Iout= -2mA)

VOL

Output Level

Output Level voltage(Iout=2mA)

ICC1

Operating current

Average power supply operating current

( /RAS, /CAS Cycling : tRC = tRC min)

50ns

60ns

70ns

ICC2

Standby current (TTL interface)

Power supply standby current

(/RAS, /CAS=VIH, Dout = High-Z)

ICC3

/RAS only refresh current

Average power supply current

/RAS only refresh mode

(tRC= tRC min)

50ns

60ns

70ns

ICC4

EDO page mode current

Average power supply current

EDO page mode (tPC=tPC min)

50ns

60ns

70ns

CMOS interface ( /RAS, /CAS >= Vcc-0.2V, Dout = High-Z)

ICC5

Standby current ( L-version)

50ns

ICC6 /CAS-before-/RAS refresh current (tRC=tRC min)

60ns

70ns

ICC7

Battery back up operating current ( standby with CBR ref.)

(CBR refresh, tRC=31.3us, tRAS <= 0.3us, Dout = High-Z, CMOS interface)

ICC8

Standby current

(RAS=VIH, /CAS=VIL, Dout=Enable)

ICC9

Self refresh current

(/RAS, /CAS <=0.2V, Dout=High-Z)

II(L) Input leakage current, Any input (0V<= Vin<=4.6V)

IO(L) Output leakage current, (Dout is disabled, 0V<= Vout<=4.6V)

Min Max Unit

2.4 Vcc

V

0 0.4 V

- 190

- 170 mA

- 150

- 2 mA

- 190

- 170 mA

- 150

- 185

- 165 mA

- 145

- 1 mA

- 150 uA

- 190

- 170 mA

- 150

- 400 uA

- 5 mA

- 250 uA

-10 10 uA

-10 10 uA

Note :

1. Icc depends on output load condition when the device is selected, Icc(max) is specified at the output open condition

2. Address can be changed once or less while /RAS=VIL

3. Address can be changed once or less while /CAS=VIH

4. /CAS = L (<=0.2) while /RAS=L (<=0.2)

5. L-Version

Note

1, 2

2

1, 3

5

4, 5

1

5

Rev.0.1/Apr.01

5

5 Page

HY51V(S)18163HG/HGL

17. Access time is determined by the longest among tAA or tCAC or tACP

18. In delayed write or read-modify-write cycels, OE must disable output buffer prior to applying data to the

device, After /RAS is reset, if tOEH>=tCWL, the I/O pin will remain open circuit (high impedance)

If tOEH < tCWL, invalid data will be out at each I/O

19. When both /UCAS and /LCAS go low at the same time, all 16 bit data are written into the device

/UCAS and /LCAS cannot be staggered within the same write / read cycles.

20. All the Vcc and Vss pins shall be supplied with the same voltages

21. tASC, tCAH, tRCS, tWCS, tWCH, tCSR and tRPC are determined by the earlier falling edge of /UCAS

or /LCAS.

22. tCRP, tCHR, tRCH, tACP and tCPW are determined by the later rising edge of /UCAS or /LCAS.

23. tCWL, tDH, tDS and tCSH should be satisfied by both /UCAS and /LCAS

24. tCP is determined by that time the both /UCAS and /LCAS are high.

25. tHPC(min) can be achieved during a series of EDO page mode write cycles or EDO mode write cycles

It both write and read operation are mixed in a EDO mode /RAS cycle(EDO mode mix cycle(1,2))

minimum value of /CAS cycle(tCAS+tCP+2tT) becomes greater than the specified tHPC(min) value.

The value of /CAS cycle time of mixed EDO mode is shown in EDO mode mix cycle (1) and (2)

26. When output buffers are enabled once, sustain the low impedance state until valid data is obtained

When output buffer is turned on and off within a very short time, generally it causes large Vcc/Vss line

noise, which causes to degrade VIH min / VIL max level

27. Data output turns off and becomes high impedance from later rising edge of /RAS and /CAS.

Hold time and turn off time are specified by the timing specification of later rising edge of /RAS and

/CAS between tOHR and tOH, and between tOFR and tOFF

28. EDO High-Z control by /OE or /WE. /OE rising edge disables data outputs. When /OE goes high

during /CAS high, the data will not come out until next /CAS access. When /WE goes low during

/CAS high, the data will not come out until next /CAS access

29. Please do not use tRASS timing, 10us<=tRASS<=100us. During this period, The device is in transition

state from normal operation mode to self refresh mode. If tRASS>=100us, then RAS

30. H or L ( H : VIH(min) <=VIN <= VIH(max), L : VIL(min) <= VIN <= VIL(max))

Rev.0.1/Apr.01

11

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet HY51V18163HGJ-7.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HY51V18163HGJ-5 | 1M x 16Bit EDO DRAM | Hynix Semiconductor |

| HY51V18163HGJ-6 | 1M x 16Bit EDO DRAM | Hynix Semiconductor |

| HY51V18163HGJ-7 | 1M x 16Bit EDO DRAM | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |