|

|

PDF 5962-9736101QYA Data sheet ( Hoja de datos )

| Número de pieza | 5962-9736101QYA | |

| Descripción | 16K/32K x 9 Deep Sync FIFOs | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 5962-9736101QYA (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

CY7C4261

CY7C4271

16K/32K x 9 Deep Sync FIFOs

Features

Functional Description

• High-speed, low-power, first-in first-out (FIFO)

memories

• 16K × 9 (CY7C4261)

• 32K × 9 (CY7C4271)

• 0.5-micron CMOS for optimum speed/power

• High-speed 100-MHz operation (10-ns read/write cycle

times)

• Low power — ICC = 35 mA

• Fully asynchronous and simultaneous read and write

operation

• Empty, Full, Half Full, and programmable Almost Empty

and Almost Full status flags

• TTL-compatible

• Output Enable (OE) pins

• Independent read and write enable pins

• Center power and ground pins for reduced noise

• Supports free-running 50% duty cycle clock inputs

• Width-Expansion Capability

• Military temp SMD Offering – CY7C4271-15LMB

• 32-pin PLCC/LCC and 32-pin TQFP

• Pin-compatible density upgrade to CY7C42X1 family

• Pin-compatible density upgrade to

IDT72201/11/21/31/41/51

The CY7C4261/71 are high-speed, low-power FIFO

memories with clocked read and write interfaces. All are nine

bits wide. The CY7C4261/71 are pin-compatible to the

CY7C42X1 Synchronous FIFO family. The CY7C4261/71 can

be cascaded to increase FIFO width. Programmable features

include Almost Full/Almost Empty flags. These FIFOs provide

solutions for a wide variety of data buffering needs, including

high-speed data acquisition, multiprocessor interfaces, and

communications buffering.

These FIFOs have 9-bit input and output ports that are

controlled by separate clock and enable signals. The input port

is controlled by a free-running clock (WCLK) and two

write-enable pins (WEN1, WEN2/LD).

When WEN1 is LOW and WEN2/LD is HIGH, data is written

into the FIFO on the rising edge of the WCLK signal. While

WEN1, WEN2/LD is held active, data is continually written into

the FIFO on each WCLK cycle. The output port is controlled in

a similar manner by a free-running read clock (RCLK) and two

read enable pins (REN1, REN2). In addition, the CY7C4261/71

has an output enable pin (OE). The read (RCLK) and write

(WCLK) clocks may be tied together for single-clock operation

or the two clocks may be run independently for asynchronous

read/write applications. Clock frequencies up to 100 MHz are

achievable. Depth expansion is possible using one enable

input for system control, while the other enable is controlled by

expansion logic to direct the flow of data.

Logic Block Diagram D0 − 8

INPUT

REGISTER

WCLK WEN1 WEN2/LD

WRITE

CONTROL

WRITE

POINTER

RS

RESET

LOGIC

RAM

ARRAY

16K x 9

32K x 9

THREE-STATE

OUTPUT REGISTER

Q0 − 8

OE

Pin Configuration PLCC/LCC

Top View

FLAG

PROGRAM

REGISTER

FLAG

LOGIC

READ

POINTER

EF

PAE

PAF

FF

READ

CONTROL

RCLK REN1 REN2

D1

D0

PAF

PAE

GND

REN1

RCLK

REN2

OE

4 3 2 1 32 31 30

5 29

6 28

7 27

8 CY7C4261 26

9

10

CY7C4271

25

24

11 23

12 22

13 21

14 15 16 17 18 19 20

RS

WEN1

WCLK

WEN2/LD

VCC

Q8

Q7

Q6

Q5

TQFP

Top View

D1

D0

PAF

PAE

GND

REN1

RCLK

REN2

32 31 30 29 28 27 26 25

1 24

2 23

3 22

4

CY7C4261

21

5 CY7C4271 20

6 19

7 18

8 17

9 10 11 12 13 14 15 16

WEN1

WCLK

WEN2/LD

VCC

Q8

Q7

Q6

Q5

Cypress Semiconductor Corporation • 3901 North First Street • San Jose, CA 95134 • 408-943-2600

Document #: 38-06015 Rev. *B

Revised August 21, 2003

1 page

CY7C4261

CY7C4271

RESET (RS)

DATA IN (D) 18 9

WRITECLOCK (WCLK)

WRITE ENABLE 1(WEN1)

WRITE ENABLE 2/LOAD

(WEN2/LD)

PROGRAMMABLE(PAF)

CY7C4261/71

FULL FLAG (FF) # 1

FF

EF

FULL FLAG (FF) # 2

9

Read Enable 2 (REN2)

RESET (RS)

9

READ CLOCK (RCLK)

READ ENABLE 1 (REN1)

OUTPUT ENABLE (OE)

CY7C4261/71

PROGRAMMABLE(PAE)

EMPTY FLAG (EF) #1

EMPTY FLAG (EF) #2

FF EF

9 DATA OUT (Q) 18

Read Enable 2 (REN2)

Figure 2. Block Diagram of 16K × 18/32K × 18 Deep Sync FIFO Memory Used in a Width-Expansion Configuration

Document #: 38-06015 Rev. *B

Page 5 of 18

5 Page

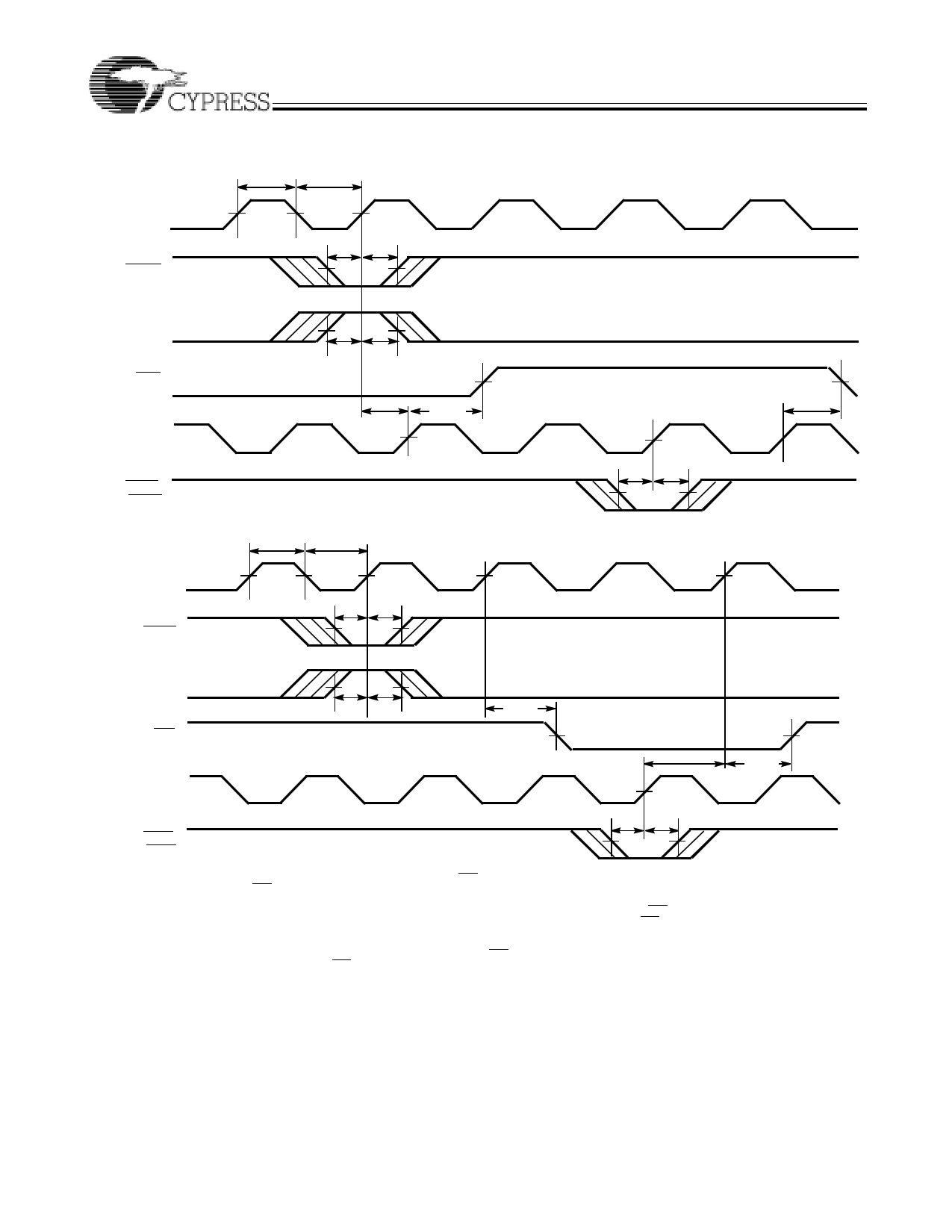

Switching Waveforms (continued)

Programmable Almost Empty Flag Timing

tCLKH

tCLKL

WCLK

WEN1

tENS tENH

CY7C4261

CY7C4271

WEN2

(if applicable)

PAE

RCLK

tENS tENH

tESKEW2[21]

Note

22

tPAE

REN1,

REN2

Programmable Almost Full Flag Timing

tCLKH

tCLKL

WCLK

WEN1

tENS tENH

Note

24

N + 1 WORDS

IN FIFO

tENS

tENS tENH

Note 23 tPAE

WEN2

(if applicable)

PAF

RCLK

tENS tENH

FULL − (M+1)WORDS

IN FIFO

Note

25

tPAF

FULL − MWORDS

IN FIFO [26]

tSKEW2 [27]

tPAF

tENS

tENS tENH

REN1,

REN2

Note:

21. tSKEW2 is the minimum time between a rising WCLK and a rising RCLK edge for PAE to change state during that clock cycle. If the time between the edge of WCLK and the rising

RCLK is less than tSKEW2, then PAE may not change state until the next RCLK.

22. PAE offset= n.

23. If a read is preformed on this rising edge of the read clock, there will be Empty + (n−1) words in the FIFO when PAE goes LOW

24. If a write is performed on this rising edge of the write clock, there will be Full − (m−1) words of the FIFO when PAF goes LOW.

25. PAF offset = m.

26. 16,384 − m words for CY7C4261, 32,768 − m words for CY7C4271.

27. tSKEW2 is the minimum time between a rising RCLK edge and a rising WCLK edge for PAF to change during that clock cycle. If the time between the rising edge of RCLK and

the rising edge of WCLK is less than tSKEW2, then PAF may not change state until the next WCLK.

Document #: 38-06015 Rev. *B

Page 11 of 18

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet 5962-9736101QYA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 5962-9736101QYA | 16K/32K x 9 Deep Sync FIFOs | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |