|

|

PDF FMS7401LEN Data sheet ( Hoja de datos )

| Número de pieza | FMS7401LEN | |

| Descripción | Digital Power Controller | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de FMS7401LEN (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

FMS7401/7401L

Digital Power Controller

www.fairchildsemi.com

General Description

The FMS7401/7401L is a family of Digital Power Control-

lers designed for applications requiring ease of digital based

control over analog based implementations. The FMS7401/

7401L family is an ideal solution to implement ballast

control, motor control and battery management functions.

This family integrates a wide variety of analog blocks with

an 8-bit microcontroller core to offer a complementary

feature set with high performance, low power and small

size in a single chip.

The FMS7401/7401L family is fabricated using CMOS

technology and is fully static. This offers significant power

savings. This family is available in both 8-pin and 14-pin

PDIP packages. SOIC and TSSOP packages are available

upon request.

The FMS7401L is intended for applications using a supply

voltage in the 2.7V to 3.6V range, while the FMS7401 is

suited for applications that use a supply voltage in the 10V to

13.5V range.

Features

• 8-bit Microcontroller Core

• 1K bytes on-board code EEPROM

• 64 bytes data EEPROM

• 64 bytes SRAM

• Watchdog Reset

• Multi-input Wakeup on all general purpose I/O pins

• Fast 12-bit PWM timer with dead time control and half-

bridge output drive

– Input Capture Mode

• 5-Ch 8-bit Analog-to-Digital Converter

– 20 µS conversion time

– Sample and Hold

– Internal Voltage Reference (1.21V)

– Gated Auto-sampling Mode

• Auto-zero Amplifier (gain 16)

• Uncommitted Amplifier

• Internal Current Source Generator (1mA)

• On-chip Oscillator

– No external components

– 1µs instruction cycle time

• On-chip Power-on Reset

• Programmable read and write disable functions

• Memory Mapped I/O

• Programmable Comparator (63 Levels)

• Brown-out Reset

• Software selectable I/O option

• Push-pull outputs with tri-state option

• Weak pull-up or high impedance inputs

• Fully static CMOS

– Power Saving Halt Mode

– FMS7401L (< 1.3µA @ 3.3V)

– Power Saving Idle Mode

– FMS7401L (< 180µA @ 3.3V)

• Single supply operation

– 10V – 13.5V (FMS7401)*

– 2.7V – 3.6V (FMS7401L)

• 40 years data retention

• 100,000 data changes

• 8-/14-pin PDIP, SOIC, and TSSOP packages

• In-circuit programming

– Fast Page-write Programming Mode

Device

FMS7401L

FMS7401L

FMS7401*

Supply Voltage

2.7V – 3.6V

2.7V – 3.6V

10V – 13.5V

Program

Memory (bytes)

1K

1K

1K

Data Memory (bytes)

SRAM

Data EEPROM

64 64

64 64

64 64

I/O

6

8

8

Pin Count

8

14

14

* Contact your local Fairchild Sales Representative for FMS7401 availability.

REV. 1.0.2 6/23/04

1 page

PRODUCT SPECIFICATION

FMS7401/7401L

10 8-Bit Microcontroller Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

10.1 Core Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

10.1.1 Accumulator (A) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

10.1.2 X-Pointer (X) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

10.1.3 Program Counter (PC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

10.1.4 Stack Pointer (SP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

10.1.5 Status Register (SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

10.1.6 Interrupt Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

10.2 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

11 Device Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

11.1 Initialization Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

11.2 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

12 In-circuit Programming Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

12.1 Programming Mode Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

12.2 Programming Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

12.2.1 Byte Write Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

12.2.2 Page Write Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

12.2.3 Byte Read Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

12.2.4 Program Memory Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

13 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

13.1 FMS7401L (2.7V to 3.6V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

REV. 1.0.2 6/23/04

5

5 Page

PRODUCT SPECIFICATION

FMS7401/7401L

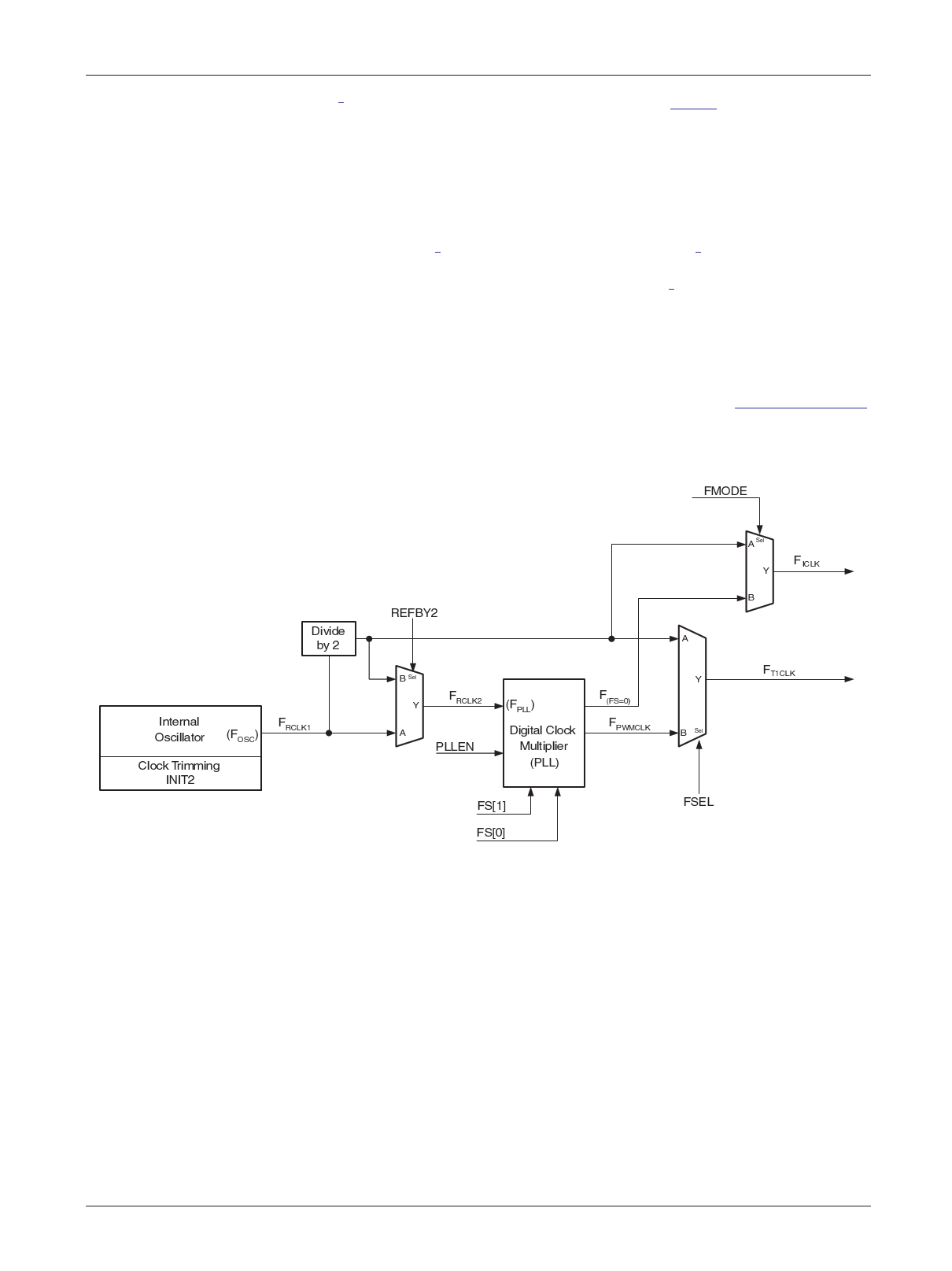

The FS[1:0] bits of the PSCALE register4 select the divide factor for the FPWMCLK output (see Table 3). The FS bits may be

changed by software at any time; however, if the PWM Timer 1 circuit is in run mode the FS[1:0] value will not change the

FPWMCLK output frequency until after the PWM cycle ends (once the TMR1 counter overflows). The last FS[1:0] value at the

PWM cycle end time will dictate the divide factor of the FPWMCLK output for the next PWM cycle. When reading the FS[1:0],

the value reported will be the last value written by software (it may not necessarily reflect the divide factor for the current

PWM cycle).

The main system instruction clock (FICLK) source may be provided by the internal oscillator (FOSC) or the PLL’s F(FS=0) output

with the same divide factor as the FS[1:0] = 00 selection.6 The FMODE bit of the PSCALE register4 selects between the F(FS=0)

(if FMODE=1) or FRCLK1 divided-by-2 signal. With the FMODE bit enabled, it is possible to execute instructions at a speed

eight times faster than the standard. The FMODE bit may not be set if the PLL is not enabled.5 Any attempts to write to

FMODE while PLLEN=0 will force FMODE=0 ignoring any set instruction. Once the PLL has been enabled, software may

change FICLK’s source on-the-fly during normal instruction execution in order to speed-up a particular action.

In order to synchronously disable the PLL clocking structure, software must clear FSEL and FMODE before clearing the

PLLEN bit in order to disable the PLL successfully e.g. using separate instructions like “RBIT PLLEN, PSCALE.” There are

also special conditions for Halt/Idle power saving modes that must also be considered. Please refer to the Power Saving Modes

section of the datasheet for details.

Figure 3. Internal Clock Scheme

FMODE

Divide

by 2

n nerI t

al

O rscillato

(FOSC)

C T mm nrlock i

ig

INIT2

FRCLK1

REFBY2

A

B Sel

Y

FRCLK2

A

PLLEN

(FPLL)

CDigital lock

Multiplier

(PLL)

F(FS=0)

FPWMCLK

FS[1]

FS[0]

Y

B Sel

FSEL

A Sel

Y

B

FICLK

FT1CLK

REV. 1.0.2 6/23/04

11

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet FMS7401LEN.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FMS7401LEN | Digital Power Controller | Fairchild Semiconductor |

| FMS7401LEN14 | Digital Power Controller | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |