|

|

PDF FAN5063 Data sheet ( Hoja de datos )

| Número de pieza | FAN5063 | |

| Descripción | ACPI Dual Switch Controller | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de FAN5063 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

FAN5063

ACPI Dual Switch Controller

www.fairchildsemi.com

Features

• Implements ACPI control with PWROK, SLP_S3 and

SLP_S5

• Switch and linear regulator controller for 3.3V Dual (PCI)

• Linear regulator controller and linear regulator for VADJ

Dual output adjustable from 2.5V to 3.5V

• Break-before-Make

• Drives all N-Channel MOSFETs plus NPN

• Latched overcurrent protection for outputs

• Power-up softstarts for the linear regulators

• UVLO guarantees correct operation for all conditions

• 16 pin SOIC package

Description

The FAN5063 is an ACPI Switch Controller for the Camino,

Whitney and Tehama Platforms. It is controlled by PWROK,

SLP_S3 and SLP_S5, and provides 3.3V Dual for PCI and

VADJ Dual output for SDRAM or RAMBUS with 200mA

minimum base current for an external NPN transistor. An on-

board precision low TC reference achieves tight tolerance volt-

age regulation without expensive external components. The

FAN5063 also offers integrated Current Limiting that protects

each output, and softstart for the linear regulators. The

FAN5063 is available in a 16 pin SOIC.

Applications

• Camino Platform ACPI Controller

• Whitney Platform ACPI Controller

• Tehama Platform ACPI Controller

Block Diagram

PWR_OK SLP_S3 SLP_S5

97

8

+5V Standby

+12V

31

2 16

10 Softstart

Osc

+5V Main

15

14

VADJ Dual

(2.5V RAMBUS

or 3.3V SDRAM)

13

12

Over Current

+ REF

-

-

REF +

11

-

+

+ REF

-

+3.3V Main

4

+5V Standby

5

6

+3.3V Dual (PCI)

REV. 1.0.0 12/4/00

1 page

PRODUCT SPECIFICATION

FAN5063

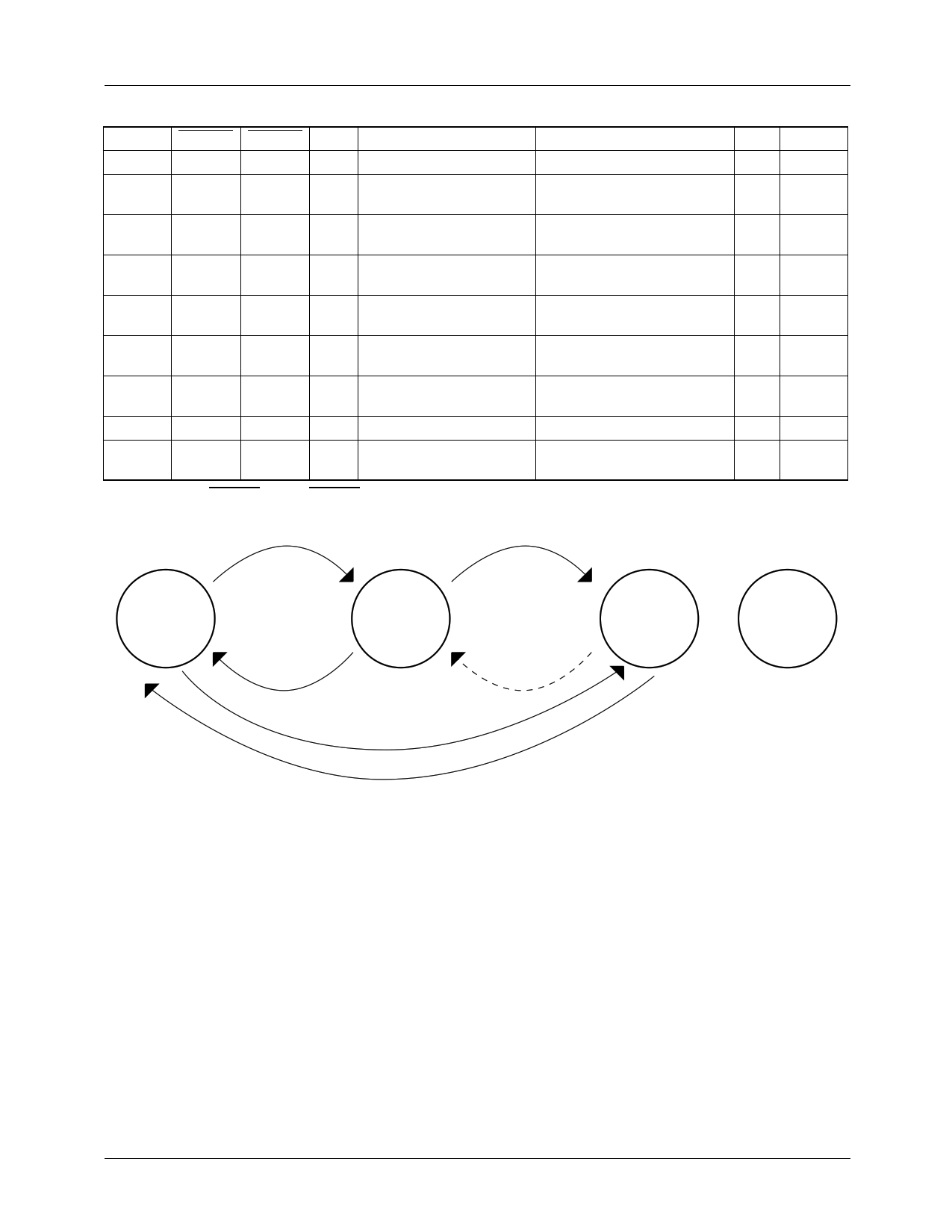

Table 1. Power Descriptors

PWROK SLP_S3 SLP_S5 Main

3.3V Dual

VADJ

1 1 1 ON ON, Powered from MAIN ON, Powered from MAIN

1

0

1 OFF ON, Powered from

ON, Powered from

STANDBY

STANDBY

0

0

1 OFF ON, Powered from

ON, Powered from

STANDBY

STANDBY

0

1

1 OFF ON, Powered from

ON, Powered from

STANDBY

STANDBY

1

0

0 OFF ON, Powered from

OFF

STANDBY

0

0

0 OFF ON, Powered from

OFF

STANDBY

0

1

0 OFF ON, Powered from

OFF

STANDBY

1 1 0 ON ON, Powered from MAIN OFF

0

0 0 → 1 OFF ON, Powered from

OFF

STANDBY

State Usage

S0 S0

S3 S0 → S3

S3 S3

S3 S3 → S0

S5 S0 → S5

S5 S5

S5 S5 → S0

S5 Not Used

S5* *

*When PWROK = SLP_S3 = 0 and SLP_S5 transitions from 0 to 1, the FAN5063 remains in the S5 state. See Table 2.

101

111 001

S0 S3

000

S5

011

100

Blocked

010

Figure 1. Power State Usage Diagram

110

Not

Used

REV. 1.0.0 12/4/00

5

5 Page

PRODUCT SPECIFICATION

FAN5063

Softstart

Pin 10 of the FAN5063 functions as a softstart. When power

is first applied to the chip, a constant current is applied from

the pin into an external capacitor, linearly ramping up the

voltage. This ramp in turn controls the internal reference of

the FAN5063. providing a softstart for the linear regulators.

The actual state of the FAN5063 on power up will be deter-

mined by the state of its control lines.

The switches in the system must be either on or off, and so

softstart has no effect on their characteristics: if the appropri-

ate control signals are asserted, they will turn on at once.

The softstart is effective only during power on. During a

transition between states, such as from S5 → S0, the linear

regulators are not softstarted.

It is important to note that the softstart pin is not an enable;

pulling it low will not necessarily turn off all outputs.

Charge Pump

In main power operation, the FAN5063 is run from the +12V

main supply. This supply also provides voltage to the various

MOSFET gates. However, during standby, this supply is off.

To provide power to the chip and the appropriate gates, the

FAN5063 incorporates a free-running charge pump. As

shown in Figure 4, and in the block diagram on the front

page, a capacitor attached between pins 1 and 2 of the

FAN5063 acts as a charge pump with internal diodes. The

charge pump output is internally diode or’red with the 12V

input. The 12V input must have a series diode to prevent

back-feeding the charge pump to the + 12V main when in

standby. The 12V input line needs a bypass capacitor for

high-frequency noise rejection.

Overcurrent

The FAN5063 does not directly detect current through the

devices that power its outputs. Instead, it monitors the output

voltages. In the event of a hard short, the voltage drops

below 80% of nominal, and all outputs are latched off, and

remain off until 5V standby power is recycled. The overcur-

rent latch off is delayed by 150µsec to prevent nuisance trips.

During softstart, the overcurrent voltage monitors are kept

proportional to the reference, to avoid tripping overcurrent

during startup.

In the S5 state, when the memory outputs are off, the voltage

monitors on the memory lines are disabled, to prevent trip-

ping the overcurrent. When turning these lines back on from

the S5 state, overcurrent is prevented from tripping because

the S3 state is blocked. See Table 2.

If the adjustable dual is not used, its feedback line, pin 12,

must be connected to 5V STBY, to prevent an overcurrent

trip.

UVLO

If the +5V standby is below approximately 4.5V, the

FAN5063 will leave off or turn off all outputs. Similar com-

ments apply to the +12V main at 7.5V. The +5V standby

UVLO has approximately 0.5V hysteresis, the +12V main

UVLO 1V.

Over Temperature

The FAN5063 is capable of sourcing substantial current,

200mA minimum to the adjustable voltage transistor’s base dur-

ing S0 and 144mA to the line during S3. As a result, there can

be heavy power dissipation in the IC. While the FAN5063 is

designed to accept this power dissipation, any overloading of

outputs can cause excessive heating. If the FAN5063 die

temperature exceeds about 150°, all outputs are shut off.

Outputs remain off until the die temperature returns to its

safe area.

Transistor Selection

External transistor selection depends on usage, differing for

the linear regulators and the switches.

The MOSFET switches, should be sized based on regulation

requirements and power dissipation. Since the ATX outputs

are ±5%, the outputs driven from them must be wider. As an

example, if we want to hold 3.3V PCI to -10%, we can drop

only 5% = 165mV across Q1. At 2.4A, this means Ql must

have a maximum RDS,on of 165mV/2.7A = 68mΩ, including

tolerance and self-heating effects. We thus choose a Fairchild

FDC633N, which has 72mΩ maximum RDS, on at 4.5V VGS

at 25°C. We can estimate power dissipation as (2.4A)2 *

42mΩ = 270mW, which should be acceptable for this pack-

age.

Q2 is a MOSFET functioning as a linear regulator. Since it

delivers only 500mA, it is easy to select a MOSFET, it need

only be able to handle 500mA * (5V + 5% – 3.3V) = 1W.

We select the Fairchild FDS6630A in an SO-8 package.

Q3 is an NPN bipolar functioning as a linear regulator. As

already discussed, it must have a VCE,sat lower than 1.45V at

IE = 2A and IB = 200mA. Its power dissipation can be as

high as (5V + 5%–3.3V) * 2A = 3.9W.

REV. 1.0.0 12/4/00

11

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet FAN5063.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FAN5063 | ACPI Dual Switch Controller | Fairchild Semiconductor |

| FAN5066 | Ultra Low Voltage Synchronous DC-DC Controller | Fairchild Semiconductor |

| FAN5067 | ACPI Dual Switch Controller | Fairchild Semiconductor |

| FAN5068 | DDR-1/DDR-2 plus ACPI Regulator Combo | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |