|

|

PDF LU3X54FTL Data sheet ( Hoja de datos )

| Número de pieza | LU3X54FTL | |

| Descripción | QUAD-FET for 10Base-T/100Base-TX/FX | |

| Fabricantes | Agere Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LU3X54FTL (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Data Sheet

July 2000

LU3X54FTL

QUAD-FET for 10Base-T/100Base-TX/FX

Introduction

Configuration

The LU3X54FTL is a four-channel, single-chip com-

plete transceiver designed specifically for dual-speed

10Base-T, 100Base-TX, and 100Base-FX repeaters

and switches. It supports simultaneous operation in

three separate IEEE standard modes: 10Base-T,

100Base-TX, and 100Base-FX. The LU3X54FTL

provides a 3.3 V or 5.0 V MII interface logic level.

Each channel implements:

s 10Base-T transceiver function of IEEE 802.3.

s Physical coding sublayer (PCS) of IEEE 802.3u.

s Physical medium attachment (PMA) of IEEE

802.3u.

s Autonegotiation of IEEE 802.3u.

s MII management of IEEE 802.3u.

s Physical medium dependent (PMD) of IEEE 802.3.

The LU3X54FTL supports operations over two pairs

of unshielded twisted-pair (UTP) cable (10Base-T

and 100Base-TX), and over fiber-optic cable

(100Base-FX).

It has been designed with a flexible system interface

that allows configuration for optimum performance

and effortless design. The individual per-port inter-

face can be configured as 100 Mbits/s MII, 10 Mbits/s

MII, 7-pin 10 Mbits/s serial, or bused mode.

s Autopolarity detection and correction

s Adjustable squelch level for extended line length

capability (two levels)

s Interfaces with IEEE 802.3u media independent

interface (MII) or a serial 10 Mbits/s 7-pin interface

s On-chip filtering eliminates the need for external

filters

s Half- and full-duplex operations

100 Mbits/s TX Transceiver

s Compatible with IEEE 802.3u MII (clause 22), PCS

(clause 23), PMA (clause 24), autonegotiation

(clause 28), and PMD (clause 25) specifications

s Scrambler/descrambler bypass

s Encoder/decoder bypass

s 3-statable MII in 100 Mbits/s mode

s Selectable carrier sense signal generation (CRS)

asserted during either transmission or reception in

half duplex (CRS asserted during reception only in

full duplex)

s Selectable MII or 5-bit code group interface

s Full- or half-duplex operations

s Optional carrier integrity monitor (CIM)

s On-chip filtering and adaptive equalization that

eliminates the need for external filters

Features

10 Mbits/s Transceiver

100 Mbits/s FX Transceiver

s Compatible with IEEE 802.3U 100Base-FX stan-

dard

s Compatible with IEEE * 802.3 10Base-T standard

for twisted-pair cable

* IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

Note: Advisories are issued as needed to update product information. When using this data sheet for design purposes, please contact

your Lucent Technologies Microelectronics Group Account Manager to obtain the latest advisory on this product.

1 page

Data Sheet

July 2000

LU3X54FTL

QUAD-FET for 10Base-T/100Base-TX/FX

Description (continued)

The bused mode has two additional submodes of

operation:

s Separate Bused MII Mode. This mode is designed

to operate with two independent repeater ICs, one

repeater operating at 100 Mbits/s and the other oper-

ating at 10 Mbits/s.

Figure 6 shows a block diagram of this mode in

which separate pins (four of each) are used for

COL_10(4), COL_100(4), CRS_10(4), CRS_100(4),

RX_EN10(4), RX_EN100(4), TX_EN10 (4), and

TX_EN100(4).

The signals RX_CLK10, RXD_10, TX_CLK10, and

TXD_10 (all from ports A, B, C, and D) are internally

bused together and connected to MII port B.

The signals TX_CLK25, TXD_100[3:0], TX_ER,

RX_CLK25, RXD_100[3:0], RX_DV, and RX_ER (all

from ports A, B, C, D) are internally bused together

and connected to MII port A.

The repeater ICs will enable the particular port to

which it will communicate by enabling the port with

TX_EN 10, TX_EN100, RX_EN10, or RX_EN100.

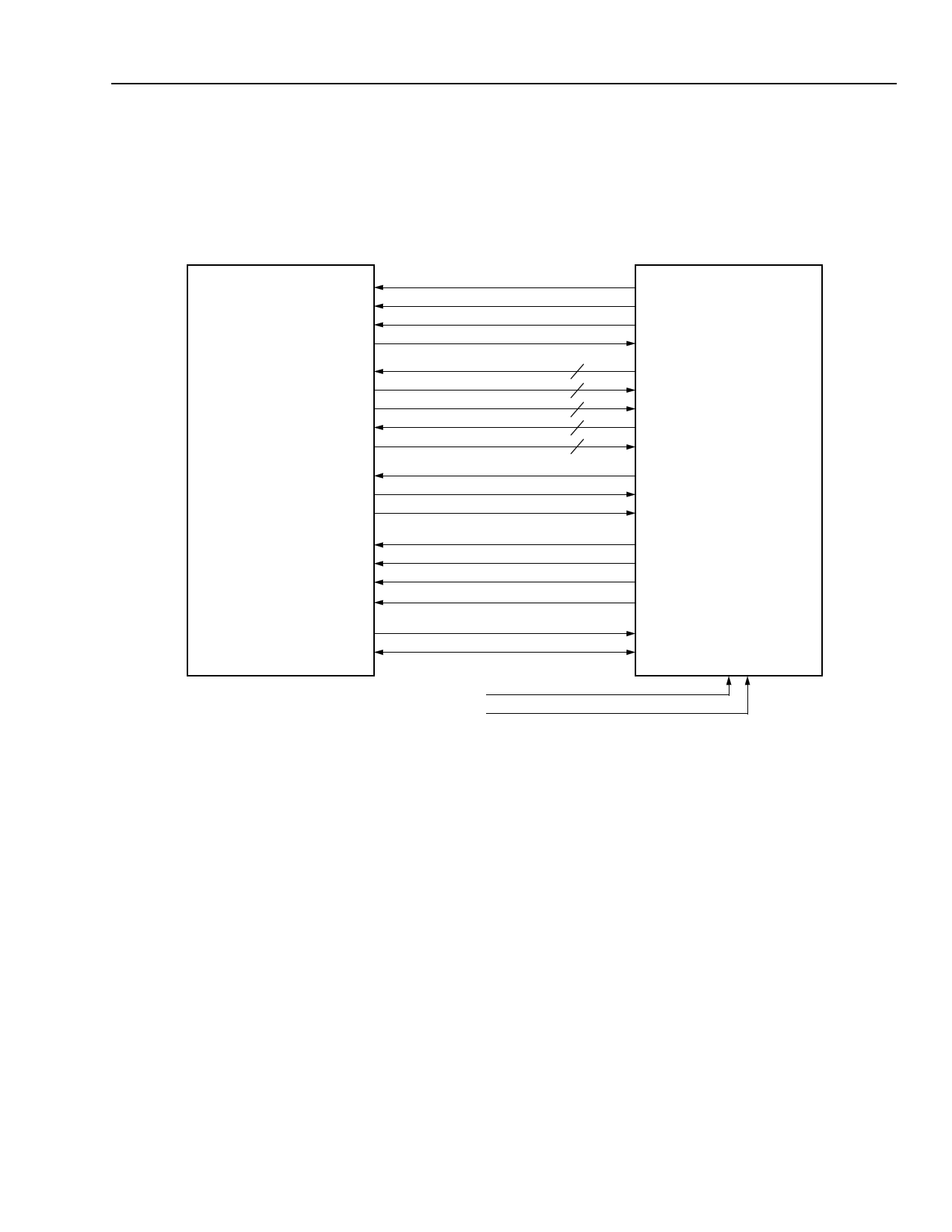

s Smart Bused MII Mode. This mode is used when

the LU3X54FTL is communicating with a single

(smart) 10/100 Mbits/s repeater IC, and allows the

use of the security feature.

Figure 5 shows a block diagram of the smart bused

mode of operation. In this mode, a common set of

pins is used for CRS_10/100[D:A],

RX_EN10/100[D:A], TX_EN10/100, and

COL_10/100.

The 10 Mbits/s (7-pin 10 Mbits/s serial interface) sig-

nals are still routed to port B (RX_CLK10, RXD_10,

TX_CLK10, and TXD_10).

The 100 Mbits/s signals are still routed to port A

(TX_CLK25, TXD_100[3:0], TX_ER, RX_CLK25,

RXD_100[3:0], RX_DV, and RX_ER).

The bused interface allows each of the four transceiv-

ers to be connected to one of two system interfaces:

s Port A: 100 Mbits/s MII interface.

s Port B: 7-pin 10 Mbits/s serial interface.

This configuration allows 10/100 Mbits/s segment seg-

regation or port switching with conventional multiport

shared-media repeaters.

The port speed configuration and connection to the

appropriate bused output is done automatically and is

controlled by autonegotiation.

Figure 1 gives a functional overview of the LU3X54FTL

while Figure 2 details its single-channel functions.

Figure 3 shows how the LU3X54FTL single-channel

interfaces to the twisted pair (TP).

Clocking

The LU3X54FTL requires an internal 25 MHz clock and

a 20 MHz clock to run the 100Base-TX transceiver and

10Base-T transceiver.

These clocks can be supplied as follows:

s As separate clock inputs: 25 MHz and 20 MHz.

s The 20 MHz clock can be internally synthesized from

the 25 MHz clock.

s The 25 MHz clock can also be internally generated

by an on-chip oscillator if an external crystal is sup-

plied.

The LU3X54FTL will automatically detect if a 25 MHz

clock is supplied, or if a crystal is being used to gener-

ate the 25 MHz clock.

Lucent Technologies Inc.

5

5 Page

Data Sheet

July 2000

Description (continued)

Block Diagrams

Smart Bused MII Mode

LU3X54FTL

QUAD-FET for 10Base-T/100Base-TX/FX

10/100 Mbits/s

SMART

REPEATER

RX_CLK10

RXD_10

TX_CLK10

TXD_10

CRS_10/100

RX_EN10/100

TX_EN10/100

COL_10/100

SECURITY10/100

4

4

4

4

4

TX_CLK25

TXD_100[3:0]

TX_ER

RX_CLK25

RXD_100[3:0]

RX_DV

RX_ER

MDC

MDIO

RX_CLK10

RXD_10

TX_CLK10

TXD_10

CRS_100

RX_EN100

TX_EN100

COL_100

TX_EN10/SECURITY_10/100

TX_CLK25

TXD_100[3:0]

TX_ER

LU3X54FTL

RX_CLK25

RXD_100[3:0]

RX_DV

RX_ER

MDC

MDIO

SMART_MODE_SELECT

BUSED_MII_MODE

Figure 5. Smart 10/100 Mbits/s Bused MII Mode

5-5599.gr1

Lucent Technologies Inc.

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet LU3X54FTL.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LU3X54FT | QUAD-FET (Fast Ethernet Transceiver) for 10Base-T/100Base-TX/FX | Agere Systems |

| LU3X54FTL | QUAD-FET for 10Base-T/100Base-TX/FX | Agere Systems |

| LU3X54FTL-HS208-DB | QUAD-FET for 10Base-T/100Base-TX/FX | Agere Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |