|

|

PDF HMP9701ACN Data sheet ( Hoja de datos )

| Número de pieza | HMP9701ACN | |

| Descripción | AC97 Audio Codec | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HMP9701ACN (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

November 19S9e8micondFucOctoRarllACoPer OnOetmSBraSSalIiOBlA:LLpEcEpeTlSinEctUaaPBtpiRoSpOn@TsDIThU1Ua-Cr8TrT0Eis0.P-c4Ro4Om2-D7U74C7T

HMP9701A

AC’97 Audio Codec

Features

Description

• Compliant with the Audio Codec ‘97 Standard

The HMP9701A is the next generation PC based audio codec

•

[

/-HTiiDgthlAeCF(iSdHeNMlRityP81976d7-B0B1itAΣ)∆

Converters

/S-ubAjDecCtS(NARC8’59d7BAudio Codec)

•/AAudtdhiotiron()al A/D for Microphone Pass-Through

solution. The HMP9701A is compliant to the new AC’97 stan-

dard and, as such, interfaces to any AC’97 compliant digital

controller. The HMP9701A offers the designer a solution to sat-

isfy the demand for flexibility and improved High Fidelity sound

in a PC environment. As part of the AC’97 PC audio standard

/Keywords (Harris Semiconductor, Audio Codecs, PCarchitecture, the HMP9701A helps pave the way for PC’97

• AC Link Serial Interface Compatible with AC’97 Digital

AuCdoinotr,oPllCer’s98, PC98, PC 98, PC’99, PC 99, PC99,

•THFiDxe,dP4C8kIHAzuSdaimo,pAlinCg9R7a,teAC’97, AC 97, AC’98, AC

AC98, SNR, AC Link, PC’97, PC 97, PC97, GAM

compliant desktop, portable and entertainment

e9f8fe,ctive high-quality audio solution.

As the analog front end of the AC’97 chipset,

PCs with a cost

the HMP9701A

•PC6ICShoanunnedl,InTpouttaMl Hixearrmonic

Distortion,

Signal

to

Noacisocecneveprtstslitnhee

level audio inputs from

analog audio to 16-bit

seven

digital

different

streams

sources

of either

and

ste-

•RaPtrioog,rRamecmoarbdleGPaoiwnerdown Modes

reo or mono data. The 48 kss data is transmitted to the control-

•) 48 Lead TQFP Package

•/CSrienagtloer+(5)V Supply

/DOCINFO pdfmark

Applications

[• /MPualgtiemMedoidaeP/CUAspepOliucatltiinoness

/D-ODCeVskIEToWp PpCdsfmark

- Notebook PCs

- PCI Sound Cards

ler via the AC’97 standard five wire interface. The controller

sends digital audio data to the HMP9701A to be converted to

analog stereo or monaural line output using two DACs.

We include an additional ADC to be used for Acoustic Echo

Canceling needed for video conferencing applications. This

ADC has a dedicated microphone input. It has the same high

quality performance as the stereo ADCs. The small 48 lead

TQFP (Thin 1.5mm and 7mm x 7mm footprint Quad Flat Pack-

age) makes it easy to locate the analog codec close to the ana-

log sources. Thus, reducing noise and lowering the cost of

- Motherboards

implementation.

• Video Conferencing

• Speaker Phones

Table of Contents

Page

Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Ordering Information

TEMP.

PART NUMBER RANGE (oC)

PACKAGE

HMP9701ACN

0 to 70 48 Ld TQFP†

PKG. NO.

Q48.7x7A

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 HMP9701EVAL2 PCI Bus Evaluation Board (Includes codec)

Serial Digital Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 † TQFP is also known as PQFP and MQFP.

Control Register Description . . . . . . . . . . . . . . . . . . . . . . . . 8

Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

AC and DC Electrical Specifications . . . . . . . . . . . . . . . . . 13

ADC/DAC Filter Response Curves . . . . . . . . . . . . . . . . . . 17

AC Timing Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Schematic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright © Harris Corporation 1998

1

File Number 4473.1

1 page

HMP9701A

TABLE 1. BIT MAP FOR SLOT 1: CONTROL ADDRESS

BITS DESCRIPTION

COMMENT

19 Read/Write

1 = Read, 0 = Write

18:12 Control Register Identifies the Target Control Register

Index

11:0 Reserved

Set to “0”

Audio Output Slot 2: Control Data

This Slot is used to deliver the 16-bit control data if the cur-

rent control register access is a write operation (Bit 19 of Slot

1 is set to “0”). The bit map for Slot 2 is given in Table 2.

samples are returned in slots 3, 4 and 6 as shown in

Figure 2. As before, the tag slot, Slot 0, is a special reserved

time slot containing 16 bits that tell the AC-link interface cir-

cuitry the validity of the following data slots.

The HMP9701A starts a new audio input frame when SYNC

makes a low to high transition and is sampled low by the falling

edge of BIT_CLK as shown in Figures 5 and 6. On the next ris-

ing edge of BIT_CLK, the HMP9701A drives SDATA_IN with

the first bit of slot 0 (Codec Ready bit). The HMP9701A drives

the remaining audio frame bits out on SDATA_IN with each ris-

ing edge of BIT_CLK. Note: SYNC must be synchronous to

BIT_CLK.

TABLE 2. BIT MAP FOR SLOT 2: CONTROL DATA

BITS DESCRIPTION

COMMENT

19:4 Control Register Set to “0” if Read operation

Write Data

3:0 Reserved

Set to “0”

Audio Output Slot 3: PCM Playback Left Channel

This time slot contains the audio sample that will be input to

the left channel DAC. The HMP9701A DAC resolution is 17

bits. All audio samples of 17 or less bits should be MSB jus-

tified within the 20-bit frame, and the trailing bits should be

set to “0”. Audio samples greater than 17 bits will be rounded

to 17 bits.

TABLE 3. BIT MAP FOR SLOT 3: PCM PLAYBACK LEFT

CHANNEL

BITS DESCRIPTION

COMMENT

19:0 PCM Audio

Sample for Left

Channel

Set unused bit positions to “0”

Audio Output Slot 4: PCM Playback Right Channel

This time slot contains the audio sample that will be input to

the right channel DAC. The DAC’s resolution is 17 bits. All

audio samples of 17 or less bits should be MSB justified

within the 20-bit frame, and the trailing bits should be set to

“0”. Audio samples greater than 17 bits will be rounded to 17

bits.

TABLE 4. BIT MAP FOR SLOT 4: PCM PLAYBACK RIGHT

CHANNEL

BITS DESCRIPTION

COMMENT

19:0 PCM Audio

Set unused bit positions to “0”

Sample for Right

Channel

HMP9701A SAMPLES

SYNC ASSERTION

HMP9701A OUTPUTS

FIRST BIT OF AUDIO INPUT FRAME

SYNC

BIT_CLK

SDATA_IN

CODEC

READY

SLOT 1

SLOT 2

PREVIOUS AUDIO FRAME

FIGURE 5. START OF AUDIO INPUT FRAME

The first bit of an input audio frame (Slot 0, bit 15) indicates

whether the HMP970’s AC Link is functional. If the “Codec

Ready” bit is a 0, the HMP9701A is not ready for normal

operation. If the “Codec Ready” bit is “1”, the HMP9701A is

ready to perform control and status register transfers. At this

point, it is the responsibility of the digital controller to exam-

ine the Powerdown Control/Status register (see Control Reg-

ister Section) to determine the operational state of the codec

subsections. The 12 bits following the “Codec Ready” Bit in

Slot 0 identify which of the 12 time slots contain valid data.

The HMP9701A outputs each time slots data word MSB first

on SDATA_IN. All non-valid bit positions (for active or inac-

tive time slots) are stuffed with 0’s by the HMP9701A.

Input Audio Slot 1: Status Address

This slot echoes the index of the control register whose con-

tents are returned in slot 2. The data in this register is the

result of a control register read operation initiated by an Out-

put Audio Frame transfer.

TABLE 5. BIT MAP FOR SLOT 1: STATUS ADDRESS

BITS DESCRIPTION

COMMENT

Audio Output Slots 5-12: Reserved

Audio output slots 5-12 are reserved for future use and

should be set to “0” for proper operation.

AC Link Input Frame (SDATA_IN)

The audio input frame contains captured audio samples and

codec status for output onto the AC-Link. The codec status

is transmitted in slots 1 and 2, and the 16-bit captured audio

19 Reserved

Stuffed with 0

18:12 Control Register Echo of Control Register Index for

Index

which data is being returned

11:0 Reserved

Stuffed with 0’s

5

5 Page

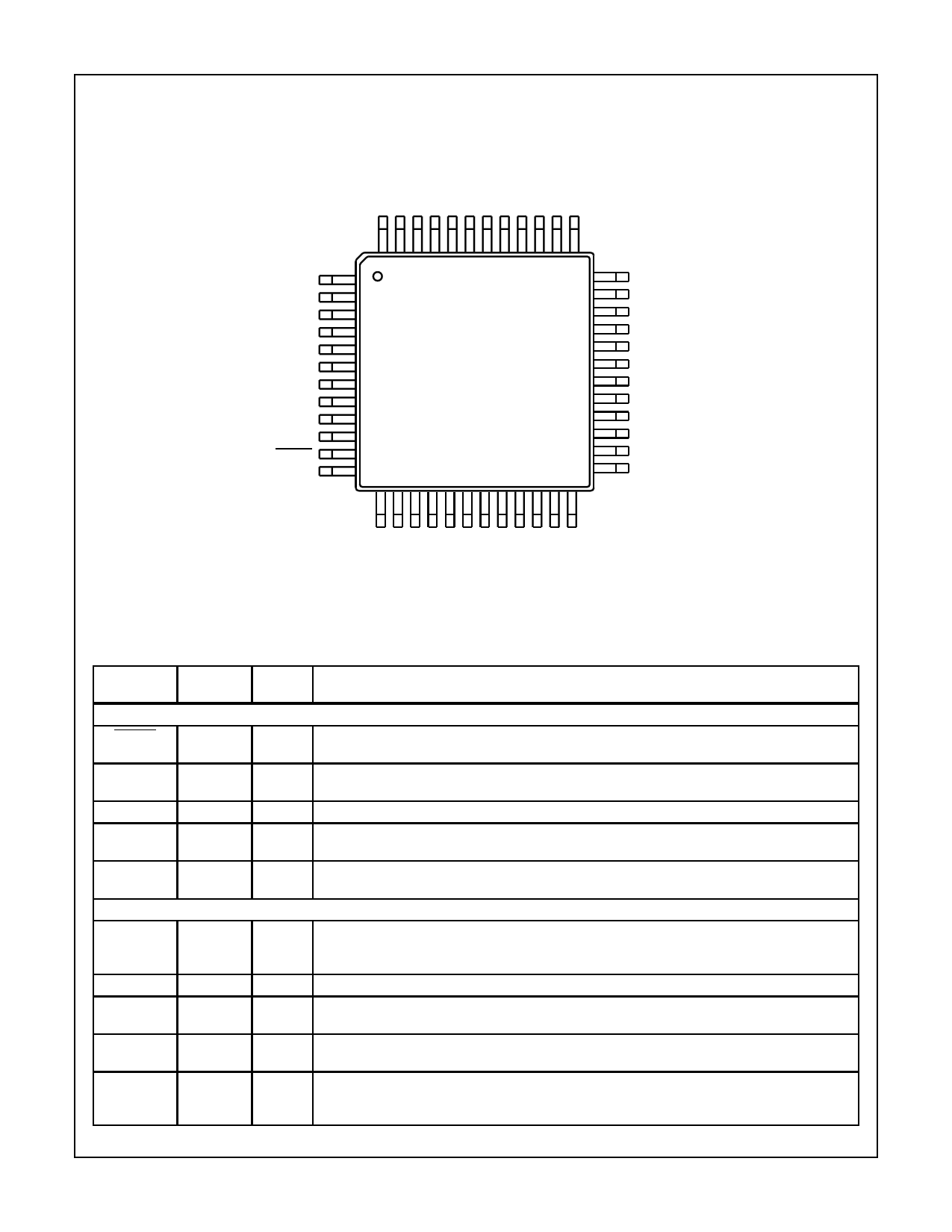

Pinout

HMP9701A

HMP9701A (TQFP)

TOP VIEW

VDD

XTL_IN

XTL_OUT

GND

SDATA_OUT

BIT_CLK

GND

SDATA_IN

VDD

SYNC

RESET

PC_BEEP

48 47 46 45 44 43 42 41 40 39 38 37

1 36

2 35

3 34

4 33

5 32

6 31

7 30

8 29

9 28

10 27

11 26

12 25

13 14 15 16 17 18 19 20 21 22 23 24

LINE_OUT_R

LINE_OUT_L

NC

RESERVED

NC

AFILT3

AFILT2

AFILT1

VREFOUT

VREF

AGND

VAA

Pin Descriptions

NAME

TQFP PIN INPUT/

NUMBER OUTPUT

DESCRIPTION

DIGITAL I/O

RESET

11

I RESET - This active low signal causes a HMP9701A hardware reset that will return the control/sta-

tus registers to their default conditions.

SYNC

10

I SYNC - 48kHz sync pulse which defines the beginning of serial audio I/O frames. Note: must be

synchronous to BIT_CLK.

BIT_CLK

6

O BIT Clock - 12.288MHz serial data clock derived by dividing down 24.576MHz crystal input.

SDATA_OUT

5

I Serial Data Out - Output bit stream that contains audio playback samples as well as control data.

This input is sampled on the falling edge of BIT_CLK.

SDATA_IN

8

O Serial Data In - Input bit stream that contains recorded audio samples as well as codec status in-

formation. Data output on the rising edge of BIT_CLK.

ANALOG I/O

PC_BEEP

12

I PC Beep. Mono Input for PC Beep pass through to LINE_OUT. This input is attenuated from 0dB

to 45dB in 3dB steps and then summed with left and right line outputs (LINE_OUT_L,

LINE_OUT_R)

PHONE

13

I Phone. Mono Input from telephony subsystem speaker phone (or DLP - Down Line Phone)

MIC1 21 I Microphone Input 1. The MIC input may be either line-level or -20dB from line-level. In the latter

case, a software controlled 20dB gain block may be activated.

MIC2 22 I Microphone Input 2. The MIC input may be either line-level or -20dB from line-level. In the latter

case, a software controlled 20dB gain block may be activated.

LINE_IN_L

23

I Left Line Input. The left line-level may be selected for recording via one of the stereo ADC’s via the

Input Mux. In addition, this input can be gained/attenuated from +12dB to -34.5dB in 1.5dB steps

and then summed with left line output (LINE_OUT_L).

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet HMP9701ACN.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HMP9701ACN | AC97 Audio Codec | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |